Преобразователь напряжения в интервал времени

Иллюстрации

Показать всеРеферат

Союз Советских

Сощиалистияеских

Ресоубттик

ОЛ ИКАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (; i 855994 (6! ) Дополнительное к «вт. свид-ву

Э (51)М. Кл. (22) Заявлено 04.01. 79 (21) 2705589/18-21 с присоединением заявки №

Н 03 К 13/20

Государственный комитет (23) 11риоритет по делам иэооретеиий н открытий

Опубликовано 15.08.81. Бюллетень Л 30 (53 ) У Д К 68 1. 325 (088.8 ) Дата опубликования описания 15.08.8 1 (72) Авторы изобретения

А. Н. Гончар-EbIUl, E. И. Мттхайпов и Г.1Ф. 7 и аттттова

1

i (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ НА ПРЯ)КЕНИЯ Q

ИНТЕРВАЛ ВРЕМЕНИ

Изобретение относится к электроизмеритеттьной технике, в частности к аналогоо цтарровым преобразователям двухтактного интегрирования и может быть использовано в цифровых вольтметрах, измерительных системах.

Известен аналого-цифровой преобразователь с однополярным источником опорно, го разрядного напряжения и выпрямитепем напряжения в канапе прохождения из10 меряемого напряжения U 1 .

Недостаток этого преобразователя - наличие погрешности преобразования при превышении сигналом помех величины преобразуемого напряжения.

Бель изобретения — уменьшение пот решности преобразования напряжения.

Поставленная цепь достигается тем, что в преобразоватепь напряжения в интерватт времени, содержаший входной уситттттель, вход которого соединен с шиной входного сигнала, а выход соединен через первый кпюч со входом интегратора, вход которого через второй ключ подключен к выходу первого опорного источника, а выход соединен со входом компаратора, при этом шина запуск соединена с первыми входами триггеров такта и цикла, а выход триггера цттктта через формирователь длительности первого такта подключен ко второму входу триггера цикла, выход которого соединен с управляющим входом первого ключа, введены инвертор, элемент 2И-НЕ, первый и второй триггеры полярности, второй опорный источник и третий ключ, причем вход инвертора co— единен с выходом компаратора и с единичным входом первого триггера полярности, а выход соединен с единичным входом второго триггера полярности, первый нулевой вход которого соединен с выходом триггера такта и первым нулевым входом первого триггера полярности, а орой нулевой вход соединен со вторым выходом триггера цикла и вторым нупевт. м входом первого триггера полярнос и, прямой выход соединен с управляющим входом третьего ключа, а ин3 85 версный выход соединен с первым входом элемента 2И-НЕ, второй вход которого соединен с инверсным выходом первого триггера полярности, а выход подключен ко второму входу триггера цикла, при этом прямой выход первого триггера полярности соединен с управляющим входом второго ключа, а второй опорный источник через третий ключ подключен ко в коду интегратора.

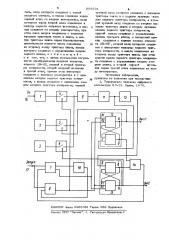

На чертеже представлена структурная схема преобразователя нап ряжения в интервал времени. Преобраэова.. тель содержит входной усилитель 1„опор ные источники 2 и 3, ключи 4-6, триггер 7 цикпа, триггер 8 такта, интеко ратор 9, формирователь 10 дпитепьности первого такта, компаратор 11, первый и второй триггеры 12 и 13 полярности, элемент 2И-HE 14, инвертор 15, вину

16 входного сигнала, щину 17 запуска.

Устройство р аботает следующим обр аэом.

Э исходном остоянии ключи 4-6 разомкнуты, интегратор 9 разряжен. Ключи 4-6 замыкаются, когда потенциал на управляющем входе соответствует логическому нулю, и размыкаются при погической единице. С приходом . запускающего щчпульса триггеры 7 и 8 изменяют состояние, п,ри этом ключ 4 замыкается, начинается заряд интегратора 9. Потенциалы на первых выходах триггеров 12 и 13 не изменяются. Компаратор 11 устанавливается в состояние, определяемое полярностью преобразуемого напря— жения U величиной напряжения, помех о состоянием интегратора.

Во время первого такта интегрирования при любом состоянии инвертора и интегратора на одном .входе элемента

2И- HE 14 присутствует потенциал, со» ответствующий логической единице, а на другом входе — логическому нулю. Поэтому независимо от полярности преобразуемого напряжения 0х на выходе элемента

2И-НЕ 14 присутствует потенциал, соответствующий логической единице. Йли тепьность первого такта интегрирования Т1 определяется формирователем 10 дпитепьнссти первого такта, который через интервал длительностью 71 с момента запуска, возвращает триггер такта в исходное состояние. Напряжение на выходе интегратора к концу первого такта иитегрирсвания будет равно: Г1 = к (о„ „,„вь ы+мун, 0 гдето„0„ - напряжение помехи. Õ 71 т = — „

Выходная информация снимается с выхода триггеров 1 2 и 1 3.

Таким образом, устройство исключает

50, погрешность измерения при превышении напряжением помех величины постоянного преобразуемого напряжения Ок .

5

10 !

Интегрирование нроизводитсч с учетом полярности преобразуемого сигнала, и интеграл от суммы равен сумме интегралов. В случае, если время интегрирования 7. кратно периоду помехи, то

7„ 71

К < 5"и Ф МЖ =О, а О„=К u

1 Х.

После возвращения в исходное состояние триггера 8 такта, ключ 4 размыкается, и начинается второй такт интегрирования, когда производится разряд интегратора. Во время второго такта на всех входах сброса триггеров 12 и 13 присутствуют потенциалы, соответствующие логической единице, дальнейшее со=тояние триггеров определяется только потекциалами на входах установки. При положи-тельной полярности выходного напряжения интегратора, триггер 12 замыкает ся, кпвч 5 замыкается, и начинается разряд интегратора от опорного источника 2. Как топько,апряжение на выходе интегратора достигает исходной величины,компаратор 11, а за ним и инвертор изменяют состояния.

При этом триггер 13 полярности изменяет состояние, а триггер 12 попярности остается в прежнем состоянии.

После этого потенциалы на входах элемент та 2И-НЕ 14 соответствуют логической единице, а на выходе — ее нупю. Зпемент 14 возвращает триггер 7 цикла по второму входу в исходное состояние.

Триггер 7 цикла, опрокидываясь, возвращает триггеры 12 и 13 полярности по вторым нулевым входаМ в исходное сос» тояние. Ключ 6 размыкается.,0литепьность интервала времени между= опрокидыванием триггера 12 и аозвращением в исходное состояние onðåäeëàåòñà задержками прохождения информации и может быть сделана сколь угодно малой. Ьжтельность второго такта интегрирования

Т1 равна

Формул а изобретения

Преобразователь напряжения в интервал времени, содержащий входной усилитель, вход которого соединен с шиной входного сигнала, а выход соединен через первый ключ со входом интегратора, вход которого через второй ключ подключен к

I BbIxogg lI8PBoPo оН0Р80Р0 источника, а BbE» 5 ход соединен со входом компаратора, при этом шина запуск соединена с первыми входами триггеров такта и иакпа, а выход триггера цикла через Формирователь длительности первого такта подключен $0 ко второму входу триггера никла, выход которого соединен с управляющим входом первогоключа, отлич ающийс я тем, что, с пенью уменьшения погреш ности преобразования введены инвертор, 1З элемент 2И-НЕ, первый и второй триггеры полярности, второй опорный источник и третий ключ, причем вход инвертора соединен с выходом компаратора и с единичным входом первого триггера полярности, а выход соединен с единичным входом второго триггера полярности, первый

94 6 нулевой вход которого соединен с выходом триггера такта и с первым нулевым входом первого триггера полярности, а вто рой нулевой вход соединен со вторым выходом триггера никла и вторым нулевым входом первого триггера полярности, прямой выход соединен с управляющим входом третьего ключе, а инверсный вы. ход соединен с первым входом элемента 2И-НЕ, второй вход которого соединен с инверсным выходс м первого вериг» гера полярности, а выход подключен ко второму входу триггера дикла, при этом прямой Выход первого триггер & попярнос» ти соединен с управляющим входом второго ключа, авторой,норнь.й источник через третий ключ подключен ко входу интегратора.

Источники информации, принятые во внимание при экспертизе

1, Техническое описание щ фрового вольтметра В7-22, Львов, 1970.

ВНИИПИ Заказ 6965/86 Тираж 9SB Подписное

Филиал ППП "Патент", г. Ужгород.,ул.Проектная,4