Счетное устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналистнческмх

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву— (22) Заявлено 151 1 79 (21) 284 2720/1 8-2 1 (51 ) M.

Н 03 К 23/00 с присоединением заявки Но (23) Приоритет

Государственный комитет

СССР ио делам изобретений и открытий

Опубликовано 15.0881. Бюллетень Но 30

Дата опубликования описания 150881 (53) УДК 6 21 . 3 74 . 34 (088. 8) (72) Авторы изобретения

И.E. Бугринова, Л.И. Миронова н A.B. Ход (71) Заявитель (54) СЧЕТНОЕ УСТРОЙСТВО

Изобретение относится к цифровой технике и предназначено для использования в аппаратуре обработки цифровой информации. Устройство может найти применение в измерительной аппаратуре, в частности в электронных измерителях времени.

Известно счетное устройство, содержащее речист сдвига, блок коррекции, блок двоичного вычитания, блок синхронизации и элементы И, ИЛИ (11, Недостатки этого устройства - его относительная сложность и малое быстродействие.

Наиболее близким техническим решением к предлагаемому является счетное устройство, содержащее матрицу памяти, с дешифратором адреса, счетчик адреса, счетчик числа, входную шину, шину установки и блок управления, информационные выходы и входы счетчика числа соединены соответственно с информационными входами н выходами матрицы памяти с дешифратором адреса, адресные входы которой соединены с информационными выходами счетчика адреса, входная шина соединена с тактовым входом счетчика числа, первый и второй выходи блока управления соединены соответ- З0 ственно со счетным входом счетчика числа и со входом управления записи матрицы памяти с дешифратором адреса.

Это устройство работает следующим образом.

Из блока управления на вход управления записи матрицы памяти с дешифратором поступает импульс, по которому содержимое -счетчика числа записывается в ячейку памяти с адресом выбранным содержимым счетчика адреса, после чего содержимое счетчика адреса увеличивается на единицу и в счетчик числа переписывается содержимое ячейки памяти с адресом, укаэанным содержимым счетчика адреса.

После этого к содержимому регистра числа прибавляются импульсы, поступающие по входной шине до тех пор, пока иэ блока управления не поступит следующий импульс на вход управления записи матрицы памяти и цикл повторяется (2).

Недостаток этого устройства — оно не может быть использовано в качестве многоразрядного счетчика импульсов.

Цель изобретения-расширение функциональных возможностей.

856011

Поставленная цель достигается тем, что в счетном устройстве, содержашем матрицу памяти с дешифратором адреса, счетчик адреса, счетчик числа, входную шину, шину установки и блок управления, информационные выходы и входы счетчика чисел соединены соответственно с информационными входами

1 и выходами матрицы памяти с дешифратором адреса, адресные входы которой соединены с информационными выходами счетчика адреса, блок управления состоит нз узла анализа переносов и хранения импульсов, нз узла установки и элемента ИЛИ, выход которого соединен со входом записи матрицы памяти с дешифратором адреса, входная шина соединена с тактовыми входами узла анализа переносов и хранения импульсов и узла установки, первый, второй, . третий и четвертый выходы которого соединены соответственно со входами сброса счетчика адреса, счетчика числа, первым входом элемента

ИЛИ и со входом сброса узла анализа переносов и хранения импульсов, первый,второй, третий и четвертый выходы которого соединены соответственно с тактовыми входами счетчиков адреса, числа, входом управления загрузкой счетчика числа, и вторым входом элемента ИЛИ, шина установки соединена с первым входом узла установки, второй вход которого соединен с выходом переноса счетчика адреса и с первым входом узла анализа переносов и хранения импульсов, второй вход которого соединен с выходом переноса счетчика числа.

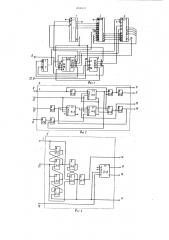

На фиг. 1 приведена функциональная схема счетного, устройства; на фиг.2 — схема выполнения узла анализа переносов и распределения импульсов; на фиг. 3 - схема узла установки в нулевое состояние счетного устройства; на фиг. 4 — временные диаграммы работы устройства.

Устройство содержит счетчик 1 адреса, матрицу 2 памяти, с дешифратором адреса, счетчик 3 числа, узел

4 анализа переносов и распределения импульсов, узел 5 установки, выход

6 переноса счетчика 1 адреса, элемент 7 ИЛИ, входную шину 8, соответственно первый, второй, третий и четвертый выходы 9 — 12 узла 4 переносов и распределения импульсов, выход

13 переноса счетчика 3 числа, соответственно первый, второй, третий и четвертый выходы 14 — 17 узла 5 установки, соответственно первый и второй входы 18 и 19 узла 5 установки, соответственно, первый, второй входы

20 и 21 и вход 22 узла 4 анализа переносов и распределения импульсов, шину 23 установки, вход 24 записи матрицы 2 памяти.

Информационные входы и выходы счетчика 3 числа соединены соответственно с информационными выходами и входами матрицы 2 памяти с дешифратором адреса, адресные входы которой соединены с информационными вы-. ходами счетчика 1 адреса, входная шина 8 соединена с тактовыми входами узла 4 анализа переносов и хране. ния импульсов и узла 5 установки, выходы 14 - 17 которого соединены соответственно со входами сброса счеl. чика 1 адреса, счетчика 3 числа, первым входом элемента 7 ИЛИ и со входом

22 сброса узла 4 анализа переносов и хранения импульсов, выходы 9-12 которого соединены соответственно с

15 тактовыми входами счетчиков 1 адреса, числа 3, входом управления загруз .кой счетчика 3 числа и вторым входом элемента 7 ИЛИ, шина 23 установки соединена со входом 18 узла 5 установки, вход которого 19 соединен с

20 выходом 6 переноса счетчика 1 адреса и со входом 21 узла 4 анализа переносов и хранения импульсов, вход

20 которого соединен с выходом 13 переноса счетчика 3 числа, выход

25 элемента 7 ИЛИ соединен со входом 24 записи матрицы 2 памяти с дешифратором адреса.

На фиг. 2 обозначено: Д-триггеры

4=1-4=3; элементы 4=4-4=8 НЕ и элементы 4=9-4=11 И-НЕ.

На фиг. 3 обозначено: элементы

5=1-5=6 И-НЕ; элементы 5=7 и Д-триггер 5=8.

На фиг. 4 номера диаграмм одинаковы с номерами соответствующих элементов, входов и выходов на фиг.1-3.

Узел 4 служит для управления работой матрицы 2 памяти и счетчиков

1 и 3. Счетчики 1 и 3 могут быть двоичными, так и иметь любой коэф4О фициент пересчета, что обеспечивается наличием в них соответствующих внутренних обратных связей.

Узел 5 служит для формирования импульсов сброса для узла 4, счет4 чиков 1 и 3 и для обнуления матрицы

2 памяти.

Устройство работает следующим образом.

Перед. началом счета при подаче

«О по шине 23 импульса установки и по шине 8 тактовых импульсов узел 5 вырабатывает импульсы сброса счетчиков 1 и 3 узла 4 и последовательно обнуляет все ячейки памяти матрицы

2 (см. Фиг ° 4).

Поступивший по входной шине 8 импульс счета формирует на выходе 11 отрицательный импульс, который считает число (в данном случае — 0 ) из матрицы 2 памяти по нулевому адd0 ресу в счетчик 3. На выходах узла 4

Формируются импульс счета (выход 9) для счетчика 1 и импульс записи (выход 12) содержимого счетчика 3 числа (в данном случае 0 ) в нулевую

65 ячейку памяти матрицы 2.

856011

Следующий счетный импульс по шине 8 производит считывание числа из памяти матрицы 2 по первому адресу, но изменения состояния счеТчика 3 числа и записи в память матрицы 2 произведено не будет, так как триг геры 4=3 и 4=2 (см. Фиг. 2) находятся в нулевом состоянии (см. фиг.4).

Последующие импульсы на шине 8 вызывают появление импульсов на выходах 9 и 11 узла 4 до тех пор, пока ц счетчик 1 не переберет по очереди все числа иэ памяти матрицы 2. Переполнение счетчика 1 переводит триггер 4=2 в состояние единицы и следующим импульсом по шине 8 содержимое памяти матрицы 2 по нулевому адресу увеличивается на единицу. Данный цикл повторяется без изменения до тех пор, пока по нулевому адресу в памяти матрицы 2 не формируется число, которое в счетчике 3 вызывает сигнал перепол- ® нения на выходе 13.

Переполнение счетчика 3 числа переводит триггеры 4=3 и 4=1 (см.фиг.2) в состояние единицы, что обеспечи" вает добавление единицы в содержимое матрицы 2 памяти по следующему адресу, т.е. будет осуществлен в следующую тетраду.

В счетном устройстве младшие раэ- ЗО ряды кодируются параллельным кодом на выходах счетчика 1 адреса, старшие разряды кодируются последователь.ным кодом, получаемым на выходах счетчика 3. 3S

При необходимости, индикация состояния счетного устройства в младших разрядах осуществляется стати- О стическим индикатором, в старших разрядах — динамическим индикатором, в данном случае роль распределителя импульсов играет счетчик адреса с дешифратором адреса, информацию на индикатор необходимо снимать со счет- 45 чика числа.

Формула изобретения

Счетное устройство, содержащее матрицу памяти с дешифратором адреса, счетчик адреса, счетчик числа входную шину, шину установки и блок управления, информационные выходы и входы счетчика числа соединены соответственно с информационными входами и выходами матрицы памяти с дешифратором адреса, о т л и ч а ю щ е ес я тем, что, с целью расширения функциональных воэможностей, блок управления состоит из узла анализа переносов и хранения импульсов (иэ узла установки и элемента ИЛИ, выход которого соединен со входом записи матрицы памяти с дешифратором адреса входная шина соединена с тактовыми входами узла анализа переносов и хранения импульсов и узла установки, первый, второй, третий и четвертый выходы которого соединены соответственно со входами сброса счетчика адреса, счетчика числа, первым входом элемента ИЛИ и со входом сброса узла анализа переносов и хранения импульсов, первый, второй, третий и четвертый выходы которого соединены соответственно с тактовыми входами счетчиков адреса, числа, входом управления загрузкой счетчика числа, и вторым входом элемента ИЛИ, шина установки соединена с первым входом узла установки, второй вход которого соединен с выходом переноса счетчика адреса и. с первым входом узла анализа переносов и хранения импульсов, второй вход которого соединен с выходом переноса счетчика числа.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке В 2610335/18-21, кл. Н 3 К 27/00, 24.04.7S.

2. Техническое описание накопителя спектров Сигма П53031,002

Сх.Б., 1968 (прототип).

856011

Ь.4

Редактор И. Касардаа

Закаэ 6966/87

Я

11

Ф=(1

4=2

f2

23

fO

f7

16

Составитель . Ранов техред Н. Ковалева Корректор М. Демчик

Тирах 988 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, X-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4