Дифференциальная система

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Otl HCAHHE

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ИЛЬСТВУ (61) Дополнительное к авт. сеид-ву(22) Заявлено 241079 (21) 2830331/18-09

<«> 856018 (51)М. Кл З

Н 04 В 1/52 с присоединением заявки Йо— (23) ПриоритетГосударственный комитет

СССР но делам изобретений и открытнй

Ю) ЧФ 621.395 ° 376 (088.8) Опубликовано 15,08,81. Ьоллетень Н9 30

Дата опубликования описания 15Ì81

О.Н. Чепорнюк, В.И. Вышняков, A B ° Гнрн к и С.A. Иванова (72) Авторы изобретения (71) Заявитель

Научно-исследовательский институт автоматизированных систем планирования и управления в строительстве

° (54 ) ДИФФЕРЕНЦИАЛЬНАЯ СИСТЕМА

Изобретение относится к электросвязи и может использоваться в аппа-, ратуре передачи данных.

Известна дифференциальная система, содержащая трансформатор с балансным контуром, усилитель, последовательно соединенные интегратор и первый пороговый блок, а также сумматор (!).

Однако точность разделения сигналов в данной системе невысока..

Цель изобретения . — повышение точности разделения сигналов.

Цель достигается тем, что в дифференциальную систему введены последовательно соединенные первый режекторный фильтр, первый ограничитель, триггер, счетчик и первый коммутатор, а также второй ограничитель, резисторная матрица, и последовательно соединенные второй режекторнай фильтр второй пороговый блок и второй коммутатор, второй вход которого соединен с генератором управляющего сигнала, а выход второго коммутатора соединен с первым входом реэисторной матрицы, выход которой соединен с . первым входом сумматора, второй вход которого соединен с входом второго ограничителя и первым выходом усилителя, второй выход которого соединен с первым входом трансформатора с балансным контуром, выход которого соединен с входом первого режекторного фильтра и вторым входом реэисторной матрицы, при этом выход сумматора соединен с входом второго режекторного фильтра, выход второго ограничителя соединен со вторым входом триггера, выход которого соединен с вторым входом интегратора, а выход первого порогового блока соединен со вторым входом первого комкутатора, выход которого соединен со

15 вторым входом трансформатора с балансным контуром.

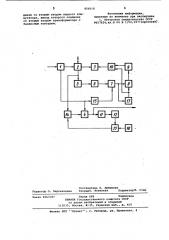

На чертеже представлена структурная электрическая схема предлагаемой системы.

20 дифференциальная система содержит усилитель 1, трансформатор 2 с балан сным контуром 3, сумматор 4 первый режекторный фильтр 5, первый ограничитель 6, триггер 7, интегратор 8, первый пороговый блок 9, первый коммутатор 10, второй режекторный фильтр

ll второй пороговый блок 12, второй коммутатор 13, резисторную матрицу

14, второй ограничитель 15, генератор

30 16 управляющего сигнала и счетчик 17., 856018

Устройство работает следующим образом.

Передаваемый сигнал через усилитель 1 поступает на трансформатор 2 и далее в канал связи (на чертеже не показан} . С выхода трансформатора 2 этот же сигнал через резисторную матрицу 14 поступает на один вход сумматора 4, на другой вход которого поступает сигнал с инверсного выхода усилителя 1. Таким образом передаваемый сигнал иа входах сумматора 4 находится в противофазе. На выходе сумматора 4 при неизменном волновом сопротивлении канала связи передаваемый сигнал уничтожается и на выходе устройства отсутствует.

При изменении волнового сопротивления канала связи передаваемый сигнал на выходе траясформатора 2 изменяется по амплитуде и фазе. С выхода трансформатора 2 сигнал через первый режекторный фильтр 5,настроенный на частоту принимаемого сигнала,и первый ограничитель б поступает на установочный вход триггера 7, на вход сброса которого через второй ограничитель 15 поступает сигнал с инверсного выхода усилителя 1. В результате на выходе триггера 7 получаются импульсы, длительность которых пропорциональна фазовому сдвигу, вносимому в сигнал изменением волнового сопротивления канала связи. С выхода триггера 7 эти импульсы поступают на интегратор 6, на выходе которОго появляется сигнал в виде постоянного напряжения, пропорционального указанному фазовому сдвигу за несколько периодов передаваемого сигнала. Это число периодов задается счетчиком 17, считающим эти импульсы. Когда счетчик 17 заполнится, он выдает разрешение на переключение первого коммутатора 10. Первый коммутатор 10 переключается в том случае, если напряжение на выходе интегратора 8 выше уровня срабатывания первого порогового блока 9,т.е. если фазовый сдвиг больше принятого допустимого значения. При этом первый коммутатор 10 переключает в балансном контуре 3 конденсатор, что дополнительно сдвигает фазу передаваемого сигнала.

Процесс перестройки длится до тех пор, пока балансный контур 3 не скомпенсирует фазовый сдвиг, вносимый волновым сопротивлением канала связи, о чем свидетельствует непревышение сигналом с выхода интегратора 8 порога первого порогового блока 9, что, в свою очередь, запрещает переключение первого коммутатора 10. В результате укаэанной подстройки сигналы на входах сумматора 4 удерживаются в противофазе. Компенсация изменения амплитуды передаваемого сигнала осуществляется с помощью реэисторной матрицы 14, управляемой вторым коммутатором 13 и генератором lб. Разрешение на переключение второго коммутатора 13 выдается в случае превышения передаваемым сигналом на еыходе устройства порога второго порогового блока 12. Для устранения влияния принимаемого сигнала на процесс.подстройки второй пороговый блок 12 подключен к выходу сумматора 4 через второй режекторный фильтр 11, настроенный на частоту принимаемого сигнала.

10 Таким образом, независимо от волнового сопротивления канала связи передаваемый сигнал на выходе дифференциальной системы не превышает заданного уровня, определяемого порогом срабатывания второго порогового блока 12. ,Сигнал, принимаемый из канала связи через трансформатор 2, резисторную матрицу 14 и сумматор 4, беспре2О пятственно поступает на выход устройства.

30

Формула изобретения

Сравнительные испытания предлагаемого и известного устройств на реальных коммутируемых каналах телефонной связи общего пользования показали, что точность согласования возрастает на }0-20 дБ..

Дифференциальная система, содержащая трансформатор с балансным контуром, усилитель, последовательно соединенные интегратор и первый пороговый блок, а также сумматор, о тл и ч а ю щ а я с я тем, что, с целью повышения точности разделения сигналов, введены последовательно соединенные первый режекторный фильтр, первый ограничитель, триггер, счетчик и первый коммутатор, а также второй ограничитель, резисторная матрица, и последовательно соединенные второй режекторный фильтр, второй пороговый блок н второй коммутатор, второй вход которого соединен с генератором управляющего сигнала, а выход второго коммутатора соединен с первым входом реэисторной матрицы, выход которой соединен с первым входом сумматора, второй вход которого соединен с входом второго ограничителя и первым выходом усилителя, второй выход которого соединен с пер вым входом трансформатора с балансным контуром, выход которого соединен с входом первого режекторного фильтра и вторым входом резисторной матрицы, при этом выход сумматора соединен с входом второго режекторного фильтра, выход второго ограничителя соединен со вторым входом триггера, выход которого соединен с вторым входом интегратора, а выход первого порогового блока сое856018

Составитель Е. Любимова

ТехредН. Ковалева Корректор И. Стед

Редактор О. Перси янцева

Тирам 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, X-35, Раумская наб., д. 4/5

Заказ 6967/87

Филиал ППП Патент,.г. Уигород, ул. Проектная, 4 динен со вторым входом первого коммутатора, выход которого соединен со вторым входом трансформатора с .балансным контуром.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9657624,кл.Н 04 В 1/52,1977(прототип).