Устройство контроля характеристик цифровых каналов связи

Иллюстрации

Показать всеРеферат

(1856021

Союз Соеетских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕИЛЬСТВУ (61) Дополнительное к авт. сеид-ву (22) Заявлено 2212.78 (21) 2701871/18-09 с присоединением заявки Ио (23) Г1риоритет (51)М. Кл з

Н 04 В 3/46

Государственный комитет

СССР по делам нзобретений н открытий

Опубликовано 1 5083 1. Бюллетень М 30

Дата опубликования описания 150831 (53) УДК621. З91.8ЗЗ (088 ° 8) (72) Авторьз изобретения

Г.П. Абугов, В.Ф. Зенкин, Ю.И. Лукьянов и А.М. Рахман (71) Заявитель (54 ) УСТРОИСТВО КОНТРОЛЯ ХАРАКТЕРИСТИК

ЦИФРОВЫХ КАНАЛОВ СВЯЗИ

Изобретение относится к электросвязи и может использоваться в аппаратуре многоканальных цифровых линий передачи и синхронных цифровых сетей.

Известно устройство контроля характеристик цифровых каналов связи, содержащее генератор эталонной последовательности, блок сравнения, выход которого подключен к информационному входу регистра сдвига, счетчик, выход которого через блок фазирования подключен к первому входу генератора эталонной последовательности, и элемент ИЛИ (1).

Однако точность контроля данным 15 устройством недостаточна.

Цель изобретения — повышение точности контроля характеристик цифровых каналов связи. цель достигается тем, что в уст- 20 ройство контроля характеристик цифровых каналов связи, содержащее генератор эталонной последовательности, блок сравнения, выход которого подключен к информационному входу регистра сдвига, счетчик, выход которого через блок фазирования подключен к первому входу генератора эталонной последовательности, и элемент ИЛИ, введены два сумматора по модулю два, 30 три элемента И, два дополнительных счетчика и три элемента ИЛИ, при этом первый выход генератора эталонной последовательности через первый сумматор по модулю два подключен к первому входу первого элемента И, второй выход генератора эталонной последовательности подключен ко входу блока сравнения, к другому входу первого сумматора пО модулю два и ко входу второго сумматора по модулю два, другой вход которого соединен с третьим выходом генератора эталонной последовательности, выход второго сумматора по модулю два подключен к первому входу второго элемента И, выход блока сравнения подключен ко вторым входам первого и второго элемента И, к другому входу блока фазирования, к первому входу третьего элемента И, к первому входу элемента ИЛИ и к установочному входу счетчика, выход первого элемента И через первый дополнительный счетчик подключен к первому входу первого элемента ИЛИ, к первому входу второго элемента ИЛИ и к третьему входу генератора эталонной последователь- ности, выход второго элемента H через второй дополнительный счетчик

856021.ír„,ê 1ю ей ко второму входу второго

:элемента ИЛИ, к первому входу треть-. его элемента ИЛИ, вторые входы перво го и третьего элементов ИЛИ соединены с выходом счетчика, со вторым входом третьего элемента И и со вторым входом элемента ИЛИ, выход первого элемента ИЛИ подключен к установочному входу второго дополнительного счетчика, выход третьего элемента ИЛИ подключен к установочному входу первого дополнительного счетчика, выход второго элемента ИЛИ подключен к установочному входу регистра сдвига, тактовый вход которого соединен с выходом элемента ИЛИ.

При этом генератор эталонной последовательности выполнен в виде регистра сдвига, первый и второй выходы которого подключены соответственНо к первому и второму входам сумматора по модулю два, выход которого подключен к первому входу регистра сдвига, третий выход регистра сдвига является вторым выходом генератора эталонной последовательности, четвертый выход регистра сдвига является первым выходом генератора эталонной последовательности, второй выход регистра сдвига является третьим выходом генератора эталонной последовательности, все выходы регистра сдвига подключены к соответствующим входам элемента ИЛИ, выход которого подключен к первому входу элемента И, второй вход которого является первым входом генератора эталонной последовательности, третий вход элемента И является вторым входом генератора эталонной последовательности, выход элемента И подключен к первому входу дополнительного элемента ИЛИ, второй вход которого является третьим входом генератора эталонной последовательности, выход дополнительного элемента ИЛИ подключен к тактовому входу регистра сдвига.

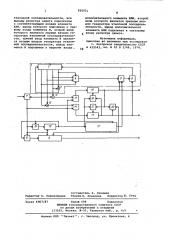

На чертеже приведена структурная электрическая схема предлагаемого устройства контроля характеристик цифровых каналов связи.

Устройство содержит генератор 1 эталонной последовательности, в состав которого входят регистр 2 сдвига, сумматор 3 по модулю два элемент ИЛИ 4, элемент И 5 и дополнительный элемент ИЛИ 6, блок 7 сравнения, элемент 8 ИЛИ, регистр 9 сдвига, счетчик 10, блок 11 Фазирования, первый и второй сумматоры 12 и 13 по модулю два, первый, второй и третий элементы 14 - 16 И, первый и второй дополнительные счетчики 17 и 18, первый, второй и третий дополнительные элементы ИЛИ 19 - 21.

Устройство работает следующим образом.

Блок 7 сравнения осуществляет посимвольное сравнение принимаемого сигнала с эталонной последовательностью. Счетчик 10 подсчитывает импульсы совпадений, поступающие на его счетный вход, через третий элемент

И 16, а при несовпадении обнуляется импульсом на установочном входе. При отсутствии синхронизма блок 11 Фаэирования через элемент И 5 и элемент

ИЛИ 6 подает импульсы на тактовый вход регистра 2 сдвига генератора 1 эталонной последовательности. Таким образом при несовпадении символов регистр 2 сдвига остается в прежнем состоянии. За счет таких остановок

15 эталонный сигнал подстраивается под принимаемую последовательность.

После окончания подстройки при отсутствии сбоев выходные импульсы счетчика 10 выключают блок 11 фази-

Щ рований и редкие сбои принимаемого сигнала не влияют на работу генератора 1 эталонной последовательности.

Импульсы, соответствующие сбоям, поступают на информационный вход регистра 9 сдвига и вписываются тактовыми импульсами с элемента 8 ИЛИ.

При отсутствии фазового сдвига эти сбои сравнительно редки, поэтому счетчик 10 быстро вновь фиксирует наличие синхроннзма и блокируется во включенном состоянии третьим элементом 16 И. При этом с выхода счетчика 10 через элемент 8 ИЛИ на тактовый вход регистра 9 сдвига поступают импульсы, продвигающие на выход регистра 9 сдвига сигналы, соответствующие сбоям.

Сигналы о, появлении дискретного сдвига выделяются первым и вторым

4Q элементами 14 и 15 И, на вторые вхо° ды которых поступают сигналы ошибки с блока 7 сравнения. При этом первый и второй сумматоры 12 н 13, сравнивающие эталонный сигнал на выходе регистра 2 сдвига генератора 1 эталонной последовательности с сигналами, сдвинутыми на величину ожидаемого

Фазового сдвига в сторону опережения и отставания,, выдают импульсы, О исключающие из рассмотрения тактовые позиции, на которых посылки этих сигналов совпадают. Действительно, искажение посылок принимаемого сигнала на этих позициях не может быть свидетельством ни наличия, ни от 5 сутствия фазового сдвига, так как в обоих случаях фиксируется сбой входного сигнала. На остальных тактовых позициях элементы И 14 и 15 открыты, и при наличии сигнала ошибки на выЩ ходе блока 7 сравнения пропускают импульсы на счетный вход дополнительных счетчиков 17 и 18. При отсутствии Фазового сдвига дополнительные счетчики обнуляются импульсами с выхода счетчика 10. При появлении

856021 дискретного фазового сдвигЬ ожидаемой величины на счетных входах обоих дополнительных счетчиков 17 и, 18 появляются импульсы, однако частота их на входе счетчика, фиксирующего сдвиг в соответствующую сторону оказывается значительно выше. Поэтому при фазовом сдвиге в сторону опережения срабатывает дополнительный счетчик 18, который, запирая элемент И 5, запрещает соответствующее ожидаемому фазовому сдвигу число ! импульсов на входе регистра 2 сдвига, корректируя фазу эталонной последовательности. При фазовом сдвиге в сторону отставания аналогичная коррекция производится дополнительным счетчиком 17, путем добавления соответствующего числа тактовых импульсов на элементе ИЛИ б. Сбои импульсов принятого сигнала не обнуляют дополнительные счетчики 17 и 18, а 20 ускоряют принятие решения о фазовой коррекции. Соответствующие наличию фазового сдвига импульсы s зависимости от направления "сдвига поступают на вход одного из внешних инди- 5 каторов. Одновременно зти импульсы через первый и третий дополнительные элементы ИЛИ 19 и 21 обнуляют дополнительный счетчик, а через второй дополнительный элемент ИЛИ 20-регистр 9 сдвига. Поскольку емкость дополнительных счетчиков 17 и 18 выбирается равной емкости регистра 9 сдвига, из сбоев, зафиксированных блоком сравнения, исключается лишь то число импульсов, которое потребовалось для определения наличия дискретного фазового сдвига, остальные сбои, в том числе и отмеченные во время фазового сдвига при запертых элементах И 14 и 15 с выхода реги- 40 стра 9 сдвига поступают на вход внешнего индикатора сбоев.

Таким образом, предлагаемое устрой. ство корректирует лишь фазовые сдвиги, возникающие при правильной работе 45 оборудования канала связи, определяет направление сдвига и отмечает наличие искажений, посылок принимаемого тест-сигнала даже во время фиксации фазового сдвига. Это улуч- 58 шает качество контроля исправности аппаратуры, обеспечивает своевременный ремонт ее или переключение на ре эерв и за счет этого повышает достоверность передачи информации по цифровому каналу связи.

Формула изобретения

1. Устройство контроля характе- 60 ристик цифровых каналов связи, содержащее генератор эталонной последовательности, блок сравнения, выход которого подключен к информационному входу регистра сдвига, счетчик, вы-.. 6$ ход которого через блок фазирования подключен к первому входу генератора эталонной последовательности, н элемент ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью повышения точности контроля, введены два сумматора по модулю два, три элемента И, два дополнительных счетчика и три элемента ИЛИ, при этом первый выход генератора эталонной последовательности через первый сумматор по модулю два подключен к первому входу первого элемента И, второй выход генератора эталонной последовательности подключен яо входу-блока сравнения, к другому входу первого сумматора по модулю два и ко входу второго сумматора по модулю два, другой вход которого соединен с третьим выходом генератора эталонной последовательности, выход второго сумматора по модулю два подключен к первому входу второго элемента И, выход блока сравнения подключен ко вторым входам первого и второго элементов И, к другому входу блока фазирования, к первому входу третьего элемента И, к первому входу элемента ИЛИ и к установочному входу счетчика, выход первого элемента И через первый дополнительный счетчик подключен к первому входу первого элемента ИЛИ, к первому входу второго элемента ИЛИ и к третьему входу генератора эталонной последовательности, выход второго элемента И через второй дополнительный счетчик подключен ко второму входу второго элемента ИЛИ, к первому входу третьего элемента ИЛИ, вторые входы первого и третьего элементов ИЛИ соединены с выходом счетчика, со вторым входом третьего элемента И и со вторым входом элемента

ИЛИ, выход первого элемента ИЛИ подключен к установочному входу второго дополнительного счетчика, выход третьего элемента ИЛИ подключен к установочному входу первого дополнительного счетчика, выход второго элемента ИЛИ подключен к установочному входу регистра сдвига, тактовый вход которого соединен с выходом элемента ИЛИ.

2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что генератор эталонной последовательности выполнен в виде регистра сдвига, первый и второй выходы которого подключены соответственно к первому и второму входам сумматора по модулю два, выход которого подключен к первому входу регистра сдвига, третий выход регистра сдвига является вторым выходом генератора эталонной последо. вательности, четвертый выход регистра сдвига является первым выходом генератора эталонной последовательности, второй выход регистра сдвига является третьим выходом генератора

856021

Составитель В. Лякишев

Редактор О. Персиянцева Техред Н.. Ковалева Корректор Н. Стец

Эакаэ 6967/87

Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 эталонной последовательности, все выходы регистра сдвига подключены к соответствующим входам элемента

ИЛИ, выход которого подключен к первому входу элемента И, второй вход которого является первым входом генератора эталонной последовательности, третий вход элемента И является вторым входом генератора эталонной последовательности, выход элемента .И подключен к первому входу дополнительного элемента ИЛИ, второй вход которого является третьим входом генератора эталонной последовательности, выход дополнительного элемента ИЛИ подключен к тактовому входу регистра сдвига °

Ф

Источники информации, . принятые во внимание при экспертизе

1. Авторское свидетельство СССР

У 429543у кл Н 03 В 3/46, 1974.