Цифровой измеритель скорости и соотношения скоростей вращения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗЬЬРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советским

Социалистическик

Реслублик (61) Дополнительное к авт. свид-ву— (22) Заявлено 11.07.79 (21) 2807722/18-10 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

G0l P 3/60

Государственный коннтет (53) УДК 621.317.,39:531.7 (088.8) но делан изобретений и открытий

Опубликовано 23.08.81. Бюллетень № 31

Дата опубликования описания 03.09.81 (72) Авторы изобретения

В. И. Гунченков, Ю. Е. Денищенко и М* И. Стремлйй " (54) ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СКОРОСТИ

И СООТНОШЕНИЯ СКОРОСТЕЛ ВРАЩЕНИЯ

Устройство относится к автоматике, вычислительной технике, измерению и контролю параметров движения.

Известны измерители скорости вращения которые обладают малой точностью измерения (11.

Известен также цифровой измеритель скорости и соотношения скоростей вращения, содержащий датчики эталонной и сравниваемой частоты, счетчики импульсов, подключенные к датчикам через двухвходовые схемы совпадения, вторые входы которых связаны с прямым выходом триггера разрешения счета, инверсный вход которого подключен к выходу схемы И совпадения сигналов на инверсных выходах всех разрядов счетчика иМпульсов эталонной, скорости, инверсный выход триггера разрешения счета соединен с входом реле времени индикации результата измерения, инверсный выход которого связан с входом формирователя импульсов установки нуля и с одним из входов трехвходовой схемы И совпадения, второй вход которой соединен с инверсным входом формирователя импульсов установки нуля, а третий — с прямым выходом датчика импульсов сравниваемой скорости, выход же трехвходовой схемы совпадения связан с прямым входом триггера подготовки схемы к запуску, прямой выход которого соединен через двухвходовую схему И совпадения с прямым входом триггера запоминания момента запуска схемы, прямой же выход последнего связан через формирователь импульсов начала отсчета с прямым входом триггера разрешения счета, причем второй вход последней двухвходовой схемы И совпадения через формирователь задержки импульсов эталонной скорости подключен к инверсному выходу датчика импульсов эталонной скорости, а входы установки нуля обоих счетчиков, триггера под-. готовки схемы к запуску и триггера запоминания момента запуска схемы соединены с прямым выходом формирователя импульсов установки нуля (21.

Недостатком этого устройства является неравномерность ошибки измерения по диапазону измерения сравниваемых скоростей и ограниченный диапазон измерения сравниваемой скорости, которая не может быть больше эталонной скорости.

857879

Цель изобретения — повышение точности измерения и расширение диапазона срав ниваемых скоростей.

Поставленная цель достигается тем, что в устройство введены три схемы ИЛИ, две схемы И коммутации и две схемы И установки.

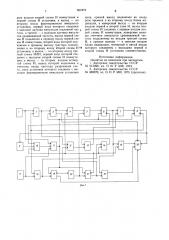

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2—

5 —, диаграммы напряжений, поясняющие его работу.

Устройство содержит датчик 1 импульсов эталонной частоты, первую схему И 2 сов.падения, счетчик 3 импульсов эталонной скорости, пятую схему И 4 совпадения первую схему ИЛИ 5, триггер 6, подготовку схемы, четвертую схему И 7 совпадения, триггер 8, разрешения счета, бесконтактное реле 9 времени индикации, вторую схему ИЛИ 10, формирователь 11 импульсов установки нуля триггера 6 подготовки схемы, первую схему И 12 коммутации, третью схему ИЛИ

13, вторую схему И 14 коммутации. первую схему И 15 установки, блок 16 индикации, датчик 17 импульсов сравниваемой частоты, вторую схему И 18 совпадения, счетчик 19 импульсов сравниваемой скорости, третью схему 20 совпадения, триггер 21 запоминания вторую схему И 22 установки.

Выходы датчиков импульсов эталонной скорости 1 и сравниваемой скорости 17 соединены через соответствующие схемы И 2 и 18 с первыми входами схем И 12, 14 и со счетными входами счетчиков импульсов эталонной скорости 3 и сравниваемой скорости

19, прямые выходы всех разрядов счетчиков 3, 19 соединены с соответствующими входами блока 16 индикации, а инверсные выходы разрядов счетчиков 3 и 19 соединены с входами cxdM И 4, 20 соответственно так, что единичный сигнал на выходах этих схем соответствует нулевому состоянию счетчиков

3 и 19. Выход схемы И 4 подключен через схему ИЛИ 5 к прямому входу триггера 6 подготовки схемы, инверсный выход которого соединен с первым входом трехвходовой схемы ИЛИ 10, а прямой выход связан с первыми входами схемы И 15, 22 и через схему И 7 с прямым входом триггера 8 разрешения счета, инверсный выход которого связан со вторыми входами схем И 2, 18, а прямой выход — с соответствующим входом блока 16 индикации и входом реле 9 времени индикации результата измерения.

Выход реле 9 времени через трехвходовую схему ИЛИ 10 соединен со вторым входом формирователя 11 импульсов установки нуля, первый и третий входы которого соединены с выходами датчиков 1 и 17 соответственно. Выход формирователя 11 соединен с входами установкы нуля счетчиков 3, 19 и триггеров 6, 8, 21. Выход схемы И 20 соединен со вторым входом схемы ИЛИ 5 и прямым входом триггера 21 запоминания, Устройство работает следующим образом.

Пусть fop (f > (фиг. 2). При окончании времени индикации результата измерения на выходе реле 9 времени появляется импульс напряжения, который, проходя через схему ИЛИ 10, запускает формирователь 11, который формирует импульс установки нуля, причем фронт этого импульса совпадает с фронтом импульса сравниваемой скорости., а спад — со спадом импульса, идущего с датчика эталонной скорости, ближайшим к импульсу, идущему с датчика сравниваемой скорости. Импульс установки нуля устанавливает счетчики 3, 19 и триггеры 6, 8, 21 в состояние, при котором на их прямых выходах потенциал отсутствует. При этом схемы

И 7, 12, 15, 22 закрыты, схемы И 4, 14 подготовлены к приему сигнала по второму входу, а схемы И 2, 18 открыты и через них с выходов датчиков 1, 17 импульсы эталонной и сравниваемой скорости поступают на входы счетчиков 3, 19 соответственно. По окончании импульса установки нуля счетчики 3, 19 начинают считать поступающие на их входы импульсы. Так как частота импульсов сравниваемой скорости меньше частоты импульсов эталонной скорости, а емкость счетчиков равны, то счетчик 3 заполняется раньше счетчика 19 и на выходе схемы И 4, на входы которой заведены инверсные выходы разрядов счетчика 3, появляется сигнал, который пройдя через схему

ИЛИ 5 на прямой вход триггера 6, переводит его из состояния «О» в состояние <1».

При этом положительный потенциал с прямого выхода триггера 6 открывает схемы

И 7, 22, проходит через открытую схему

И 15 на первый вход установки блока 16 индикации. С приходом очередного импульса с датчика 1 счетчик 3 начинает второй цикл счета. При приходе ближайшего, после окончания первого цикла счета счетчиком 3, импульса сравниваемой скорости, который проходит с выхода схемы И 18 через схемы

И 14; ИЛИ 13, И 7 на прямой вход триггера 8, триггер 8 из состояния «О» переходит в состояние «1», на его инверсном выходе появляется потенциал, равный нулю, что приводит к закрытию схем И 2, 18 н прекращению работы счетчиков 3, 19, а положи15

2О

ЗО

4О

55 прямой выход которого соединен с вторыми входами схем И 12, 22, выход последней соединен с первым входом установки блока 16 индикации, а инверсный выход триггера 21 связан с третьим входом схемы ИЛИ 10 и вторыми входами схем И 4, 14 и 15, причем выход последней соединен со вторым входом установки блока 16 индикации. Входы схемы ИЛИ 13 соединены с выходами схем И 12 и 14„а выход — с вторым входом схемы И 7.

Емкость счетчиков 3, 19 условно принята равной 2 .

857879

15 го г5

Формула изобретения

Ы тельный потенциал прямого выхода триггера 8 запускает реле 9 времени и дает команду на блок 16 индикации для индицирования результата измерения. По окончании времени индикации на выходе реле 9 появляется импульс, который, пройдя через схему ИЛИ 10, запускает формирователь

11, и цикл измерения повторяется.

Так как время запуска устройства привязано к импульсу сравниваемой скорости с точностью не хуже +. 0,5 Тэт, а остановка счета так же производится передним фрон-, том импульса сравниваемой скорости, т. е. фактически интервал времени, кратный периоду следования импульсов сравниваемой скорости, заполняется некоторым числом п импульсов эталонной скорости. При этом N ò — "2 — к ь

tl гэт

Ь в этом случае всегда меньше Тэт, т. е. меньше единицы младшего разряда счетчика импульсов эталонной скорости.

Если частота следования импульсов сравниваемой скорости выше частоты импульсов эталонной скорости (фиг. 3) то первым заполняется счетчик 19, при этом на выходе схемы И 20 появляется сигнал, который переводит триггер 21 непосредственно, а триггер 6 через схему ИЛИ 5 из состояния

«О» в состояние «1». Сигнал с прямого выхода триггера 6 открывает схему И 7, проходит через открытую схему И 22 на второй вход установки блока 16 индикации. Сигнал с прямого выхода триггера 21 открывает схемы И 12, 22, а с инверсного — закрывает схемы И 14, 15. Первый импульс эталонной скорости, приходящий после заполнения счетчика 19, с выхода схемы И 2 проходит через схемы И 12, ИЛИ 13, И 7 на прямой вход триггера 8, Триггер 8 своим инверсным выходом закрывает схемы

И 2, 18 и прямым выходом запускает реле

9 времени и блок 16 индикации.

По окончании времени индикации цикл измерения повторяется. В этом случае так же временной интервал отсчитанный импульсами сравниваемой скорости заполняется импульсами эталонной скорости, и поэтому ошибка так же меньше единицы младшего разряда счетчика импульсов эталонной скорости. Если сравниваемая скорость меньше минимальной скорости умеряемого диапазона, т. е. fcp

Если fcp )1срмакс (фиг. 5), то два цикла счета делает счетчик 19, и при приходе второго импульса с выхода счетчика 19 через схему И 20 на счетный вход триггера

21, последний переходит из состояния «1» в состояние «О» и положительный потенциал с инверсного выхода триггера 21 через схему ИЛИ 10 запускает формирователь 11, цикл измерения повторится.

Так как счетчики 3, 19 могут в цикле измерения заполнятся два раза, то полный цикл измерения равен 2 Тэт п Ис .миq = — =

Тср.макс, — = — —, т. е, fcp в два ра1 тэфи

ЯЪм h h за ниже, чем в устройстве аналога эм 2 ср мю п Тср и

Тэн .

<с .надю — — = = 1зн 2п.

1 2

Р-н Tcp.HNH Тэм т. е. максимальная частота следования импульсов сравниваемой скорости в два раза выше, чем у известного устройства.

Следовательно диапазон измерения предлагаемого устройства в четыре раза шире диапазона измерения известного устройства.

Цифровой измеритель скорости и соотношения скоростей вращения, содержащий датчики импульсов эталонной и сравниваемой частоты, выходы которых через первую и вторую двухвходовые схемы И подключены к счетчикам импульсов, формирователь импульсов установки нуля, выход которого соединен со входами установки счетчиков и триггеров запоминания и подготовки схемы, причем счетный вход триггера запоминания подключен к выходу третьей схемы И, прямой выход триггера подготовки схемы соединен с первым входом четвертой схемы И, триггер разрушения счета, пятую схему И, выходы которой подключены к инверсным выходам счетчика импульсов эталонной частоты, блок индикации, соединенный с прямыми выходами счетчика импульсов эталонной частоты и реле времени, отличающийся тем, что, с целью повышения точности измерения во всем диапазоне частот и расширения диапазона измерения, в него введены три схемы

ИЛИ, две схемы И коммутации и две схеИ установки, причем выход пятой. схемы И подключен к первому входу первой схемы

ИЛИ, второй вход которой соединен с выходом третьей схемы И, а выход — со счетным входом триггера подготовки схемы, прямой выход которого подключен к первым входам двух схем И установки, а инверсный — к первому входу второй схемы

ИЛИ, второй вход которой соединен с выходом реле времени, третий вход подключен ко второму входу пятой схемы И, к инверсному выходу триггера запоминания и ко вто85?879 рым входам второй схемы И коммутации и первой схемы И установки, а выход — ко .второму входу формирователя импульсов установки, первый вход которого соединен с выходом датчика импульсов эталонной час- > тоты, а третий — с выходом датчика импульсов сравниваемой частоты, выход первой схемы И подключен к первому входу первой схемы И коммутации, второй вход которой подключен к прямому выходу триггера запоминания и ко второму входу второй схемы И 10 установки, а выход — ко второму входу третьей схемы ИЛИ, первый вход которой соединен с выходом второй схемы И коммутации, а выход — со вторым входом четвертой схемы И, выход которой подключен к счетному входу триггера разрешения счета, вход установки которого соединен с выходом формирователя импульсов установки нуля, прямой выход подключен ко входу реле времени и ко второму входу блока индикации, а инверсный выход — ко вторым входам первой и второй схем И, выход второй схемы И соединен с первым входом второй схемы И коммутации, инверсные выходы счетчика импульсов сравниваемой частоты подключены ко входам третьей схемы

И, а прямые выходы — к третьим входам блока индикации, четвертый и пятый входы которого соединены с выходами первой и второй схемы И установки соответственно.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 515996, кл. G 01 P 348, 1974.

2. Авторское свидетельство СССР № 388229, кл. G 01 P 3/б0, 1973 (прототип).

857879

PS 9 дыл 111 дых7ТВ дых. Иг

Вых. И 18

Вььх И4 дых.ТГб

И ЦИЛР13, Сч.3

Сч.!9

Фиг.2

Йзи

Вых.Ф11

Вых. тlд

Вых Н2

Вых И18

Вых. И4

Вых.7Тб

Н12, ИАИ13, Н7

Вых. 28 дыл7Г21

CY. 3 гр

1р

857879

1ихм

Вык. Ф11

Вых: 7ГВ

Вык. Иг

Sblx. ulS

Вых. И4

Бых, ТГб

1р г

Фиг 4 .тзт

Уихм

PB9

Вых.Ф11

Вых тГВ

Вых. HZ

Вых HlS

В х.ига

Вых,ТГб

Jp

Сч. 19 гр

Фиг.5

Составитель М. Хаустов

Редактор О. Малец Техред А. Ьойкас Корректор М. Шароши

Заказ х234/74 Тираж 907 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4