Многоканальное устройство для функционального контроля интегральных схем

Иллюстрации

Показать всеРеферат

Сомз Советсник

Социалистическик

Республик

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 30.07.79 (21) 2787302/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

G01 R31/28

Гасударственные комитет

Опубликовано 23.08.81. Бюллетень № 31

Дата опубликования описания 03.09.81 (53) УДК 681.3 (088.8) па делам изобретений и открытий (72) Авторы изобретения

А. А. Амбарцумян, Н. В. Андрунакиевич, О. П.

Л. А. Ивченков, А. И. Потехин, А. П. Рыдныч, В. Г и Н. А. Угнивенко (71) Заявитель (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО

КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ

Изобретение относится к вычислительной технике и предназначено для осуществления функционального контроля БИС и логических блоков ЭВМ.

Известны специальные логические вычислительные устройства для функционального

5 контроля, содержащие входнои регистр, блок памяти, блок сравнения и выходной регистр (1).

Недостатком известного устройства является низкая достоверность контроля, обусловленная частотой выдачи управляющих сигналов на объект контроля, ниже по сравнению с рабочей частотой функционирования объекта.

Наиболее близким к предлагаемому техническим решением является специальное логическое вычислительное устройство для функционального контроля, содержащее входной регистр, управляющий элемент И, генератор, триггер запуска, группа элементов ИЛИ, а в каждом канале блок сравнения,, блок памяти и выходной регистр (2).

Недостатком данного устройства является низкая достоверность контроля, обусловленная низкой частотой выдачи контрольных сигналов на объект и обработки сигналов реакции объекта контроля по сравнению с рабочей частотой функционирования объекта.

Цель изобретения — повышение достоверности.

Указанная цель достигается за счет того, что в устройство для функционального контроля интегральных схем, содержащее многоканальное устройство для функционального контроля интегральных схем, содержащее входной регистр, информационные входы которого соединены с группой входов устройства, а управляющий вход подключен к выходу управляющего элемента И, входы которого соединены соответственно с выходами генератора и триггера запуска, единичный вход которого соединен с запускающим входом устройства, группу элементов ИЛИ, выходы которых соединены с группой выходов устройства, а каждый канал содержит блок сравнения, памяти и выходной регистр, причем первая группа входов блока сравнения данного канала соединена с выходами входного регистра, вторая группа входов блока сравнения подключена

857890 к первой группе выходов памяти этого же канала, вторая группа выходов которой соединена с информационными входами выходного регистра этого канала, одноименные выходы выходных регистров всех каналов подключены ко входам соответствующего элемента ИЛИ группы, введены элемент

ИЛИ и распределитель, а в каждый канал введены три элемента И, триггер, причем, выход элемента ИЛИ соединен с нулевым входом триггера запуска, а вход распреде- >о лителя подключен к выходу управляющего элемента И, в каждом канале первый вход первого элемента И соединен с выходом блока сравнения этого же канала, второй вход первого элемента И каждого канала

15 соединен с соответствующим выходом распределителя, выход первого элемента И каждого канала подключен к единичному входу триггера этого же канала, нулевой вход которого соединен с соответствующим выходом распределителя, единичный и нулевой 20 выходы триггера каждого канала подключены к первым входам соответственно второго и третьего элементов И этого же канала, вторые входы которых объединены и подключены к соответствующему выходу распределителя, выход второго элемента И каж25 дого канала соединен с управляющими входами блока сравнения и выходного регистра этого же канала, а выход третьего элемента И подключен к соответствующему входу элемента ИЛИ, управляющий вход па- зр мяти и вход считывания выходного регистра соединены с соответствующими выходами распределителя.

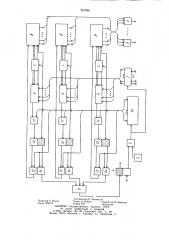

На чертеже представлена блок-схема устройства для функционального контроля. . Устройство содержит входной регистр 1, З5 управляющий элемент И 2, генератор 3, триггер 4 запуска, группу элементов ИЛИ 5, блок сравнения 6 и памяти 7, выходные регистры 8, элемент ИЛИ 9, распределитель

10, элементы И 11, триггеры 12, элементы

И 13 и элементы И 14. Блок 6 сравнения, 40 блок памяти 7, выходной регистр 8, элементы И 11 — 14 и триггер 12 составляют один канал.

Функционирование специального логического вычислительного устройства для 4 функционального контроля осуществляется следующим образом.

В блок 7 памяти i-го канала, где 1 (((1 записаны наборы управляющих и контрольных сигналов теста с номерами i, N+ i, 2N+i и т. д. Предварительно, в блок 7 памяти каждого канала выбраны первые наборы управляющих и контрольных сигналов. Далее, во всех каналах, кроме N-го осуществляется запись выбранных наборов управляющих и контрольных сигналов в соответствующие выходные регистры 8 и регистры блоков 6 сравнения. После этого, во всех блоках 7 памяти, кроме (N — 1)-го и N-го каналов, выбираются вторые наборы управляющих и контрольных сигналов.

Затем, из выходного регистра 8 первого канала через элементы ИЛИ 5 на объект контроля подается первый набор управляющих сигналов, п триггер 5 запуска устанавливается в единичное состояние, вследствие чего снимается блокировка с управляющего элемента И 2 и выход генератора 4 подключается ко входу распределителя 10 и входного регистра 1. При этом, входной регистр

1 функционирует по переднему фронту единичного логического уровня, вырабатываемого генератором 4, а распределитель 10— по заднему фронту указанного единичного логического уровня. Вследствие этого, в первом такте осуществляется запись во входной регистр 1 первого набора выходных сигналов объекта контроля, который сравнивается в блоке 6 первого канала с первым набором контрольных сигналов, поданных с выходов соответствующего блока 7 памяти и хранимых в регистре указанного блока

6 сравнения. По первому сигналу распределителя 10 результат сравнения через элемент И 11 первого канала запоминается на соответствующем триггере 12, предварительно установленном в нулевое состояние. Одновременно с этим осуществляется запись в выходной регистр 8 N-ro канала набора управляющих сигналов и выборка очередного набора управляющих и контрольных сигналов в блоке 7 памяти (Nl — 1)-го канала, а также подача из выходного регистра 8 второго канала через элементы ИЛИ

5 на объект контроля второго набора управляющих сигналов. Во втором такте осуществляется запись во входной регистр 1 второго набора выходных сигналов объекта контроля, который сравнивается в блоке 6 второго канала с вторым набором контрольных сигналов поданных с выходов соответствующего блока 7 памяти и хранимых в регистре указанного блока 6 сравнения. По второму сигналу распределителя 10 результат сравнения через элемент И 11 второго канала запоминается на соответствующем триггере 12, предварительно установленном в нулевое состояние. Одновременно с этим осуществляется анализ содержимого триггера 12 первого канала с помощью разблокировки элемента И 13 и элемента И 14 этого же канала. При совпадении первых наборов выходных сигналов объекта контроля и контрольных сигналов на блоке 6 сравнения первого канала, т. е. при правильном функционировании объекта контроля триггер 12 первого канала будет находиться в единичном состоянии, в результате чего при помощи единичного логического уровня с выхода соответствующего выходного элемента И 13 будет осуществлена запись очередного набора управляющих и контрольных сигналов в выходной регистр 8 и в регистр

857ЫУО

Формула изобретения

Многоканальное устройство для функциозо

35 блока 6 сравнения этого канала. Одновременно, по второму сигналу распределителя

10, осуществляется выборка очередного набора управляющих и контрольных сигналов в блоке 7 памяти N-го канала, а также подача из выходного регистра 8 третьего канала через элементы ИЛИ 5 на объект контроля третьего набора управляющих сигналов. При неправильном функционировании объекта контроля триггер 12 первого канала будет находиться в нулевом состоянии, в результате чего при помощи единичного логического уровня с выхода соответствующего элемента И 14 через элемент ИЛИ 9 триггер 5 запуска будет переведен в нулевое состояние. Вследствие этого генератор 4 будет отключен от распределителя 10. Дальнейшее функционирование специального логического вычислительного устройства для функционального контроля осуществляется аналогично. При этом, каждый i-тый сигнал распределителя 10 устанавливает триггер 12 (i — 2)-го канала в исходное нулевое состояние. нального контроля интегральных схем, содер жащее входной регистр, информационные входы которого соединены с группой входов устройства, а управляющий вход подключен к выходу управляющего элемента И, входы которого соединены соответственно с выходами генератора и триггера запуска, единичный вход которого соединен с запускающим входом устройства, группу элементов ИЛИ, выходы которых соединены с груп пой выходов устройства, а каждый канал содержит блок сравнения, памяти и выходной регистр, причем первая группа входов блока сравнения данного канала соединена с выходами входного регистра, вторая группа входов блока сравнения подключена к

1О

15 яо первой группе выходов памяти этого же канала, вторая группа выходов которой соединена с информационными входами выходного регистра этого канала, одноименные выходы выходных регистров всех каналов подключены ко входам соответствующего элемента ИЛИ группы, отличающееся тем, что, с целью повышения достоверности, в него введены элемент ИЛИ и распределитель, а в каждый канал введены три элемента И, триггер, причем выход элемента

ИЛИ соединен с нулевым входом триггера запуска, а вход распределителя подключен к выходу управляющего элемента И, в каждом канале первый вход первого элемента

И соединен с выходом блока сравнения этого же канала, второй вход первого элемента и каждого канала соединен с соответствующим выходом распределителя, выход первого элемента И каждого канала подключен к единичному входу триггера этого же канала, нулевой вход которого соединен с соответствующим выходом распределителя, единичный и нулевой выходы триггера каждого канала подключены к первым входам соответственно второго и третьего элементов И этого же канала, вторые входы которых объединены и подключены к соответствующему выходу распределителя, выход второго элемента И каждого канала соединен с управляющими входами блока сравнения и выходного регистра этого же канала, а выход третьего элемента И подключен к соответствующему входу элемента ИЛИ, управляющий вход памяти и вход считывания выходного регистра соединены с соответствующими выходами распределителя.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 390526, кл. G 06 F 11/00, 19.05.70.

2. Березенко А. И. и др. Система функционального контроля БИС. «Электронная промышленность». Вып. 6(66), 1978, с. 64, рис. 3 (прототип).

857890

Составитель В. Чачанидзе

Педактор О.Малец Техред А. Бойкас Корректор М. Шароши

Заказ 7235/74 Тираж 732 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4