Магнитный накопитель

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОВРЕТЕН ИЯ

К AQTOPCKOAAV СВИДЕтаЛЬСтвЮ

Сатана Соеетсинк

Сецманистичесник

Ресттубпте (и! 858096 (6l ) Дополнительное к авт. свнд-ву (22) Заявлено 21. 11. 77 (21) 2544747/18-24 с присоединением заявки М (23) Приоритет— (51)M. Кл.

G ll С 11/02

Ьу1РрвтвнвЫ1 квинтет

CCCP ав двлзи кмбрвтвкк11 я еткрмткя

Онублнковано 23.08.81. Бюллетень М 31

Дата опубликования описания 23,08.81 (53) УДК 681.327 . 66 (088. 8) 1

М,М.Рудник, Л.А.Колосков и Ю.Л."cocoa

1 (72) Авторы изобретения

I !

f (71) Заявитель (54) МАГНИТНЫЙ НАКОПИТЕЛЬ

Изобретение относится к вычисли тельной технике, в частности к устройствам хранения дискретной информации, и может быть использовано при проек тировании магнитных оперативных sanoминающих устройств на интегральных магнитных носителях инФормации.

Известны магнитные накопители,выполненные на многоотверстных ферритовых пластинах, состоящие иэ кассет, образующих модули, в середине каждой иэ которых размещена коммутационная плата, к выводам которой присоединены концы разрядных обмоток (1 ).

Однако аанное устройство уменьшает взаимное влияние только двух рядом расположенных обмоток, но не обеспечивает устранения взаимного влияния обмоток, расположенных в различных группах, т.е. не обладает высокой помехоустойчивостью.

Наиболее близким к предлагаемому является магнитный накопитель, содержащий 1т модулей магнитных запоминающих элементов с адресными обмотками и с группами последовательно соединенных разрядных обмоток, в каждой из которых и/2 разрядных обмоток соединены согласно друг с другом и встречно по отношению к другим i!/2 разрядным обмоткам(22.

Данное техническое решение позволяет уменьшить взаимное влияние четырех разрядных обмоток., принадлежащих к одной группе, но не устраняеа взаимного влияния разрядных обмоток, принадлежащих к различным группам, что снижает помехоустойчивость устройства.

Цель изобретения — повышение помехоустойчивости магнитного накопителя.

Поставленная цель достиается тем, что в магнитном накопителе, содержащем И запойинающих модулей, где тт кратно 4, с адресными обмотками и с пт разрядными обмотками, где Щ> 2, И/2 разрядных обмоток накопителя соединены согласно друг с другом и встреч858096 где 4g и h .. — двоичные значения позиций ортогональной матрицы;

1, + i — номер строки;

5 j — номер столбца; для любых двух разрядных обмоток запоминающих модулей количество пар индуктивно связанных участков,направленных согласно друг другу рав9

10 но количеству пар участков, направленных друг другу навстречу, что, естественно, позволяет уменьшить взаимное влияние между ними, Применение изобретения позволяет увеличить информационную емкость запоминающего устройства эа счет наращивания числа разрядных обмоток, что в итоге приводит к снижению удельной стоимости запоминающей

20 ячейки.

Формула изобретения

40

Источники информации, принятые во внимание при экспертизе ю 1. Авторское свидетельство СССР

Ф 251003, кл. G 11 С 11/02, 1968.

2. Авторское свидетельство СССР

Ф 266852,кл. G 11 С 11/02, 1969 (прототип). но по отношению к другим разрядным обмоткам,для любых двух разрядных обмоток накопителя n/4 разрядных обмоток запоминающих модулей соединены согласно друг другу и однонаправлено, другие n/4 разрядных обмоток запоминающих модулей соединены согласно друг другу и встречно по отношению к первым n/4 ðàçðÿäным обмоткам запоминающих модулей, третьи n/4 разрядных обмоток запоминающих модулей соединены встреч-но друг другу и встречно по отношению к четвертым и/4 разрядным обмоткам запоминающих модулей.

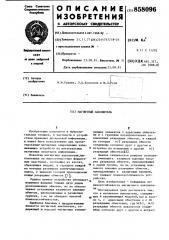

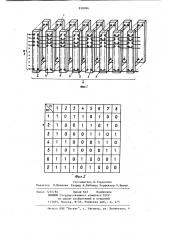

На фиг.1 представлена структурная схема магнитного накопителя;на фиг.2» ортогональная матрица для m=7 и

n = 8.

Устройство содержит и запоминаюших модулей 1 с адресной обмоткой

2, ш разрядными обмотками 3, каждая из которых прошивает соответствующие запоминающие модули. 1 и разделена на и участков. Номеру каждого запоми25 нающего модуля 1 соответствует определенный (n-ый) столбец ортогональной двоичной матрицы (фиг.2), а номеру каждой разрядной обмотки соответствует номер строки ортогональной матрицы. Свободные одноименные

30 выводы 1,начала 4,концы 5 ) двух соседних участков разрядных обмоток, каждо. му из которых соответствуют противоположные значения их позиций в ортогональной матрице, соединены межпу собой, а свободные разноименные выводы двух соседних участков, каждому из которых соответствуют одинаковые значения их позиций в ортогональной матрице, также соединены между собой. Причем это правило соединения распространяется как на отдельные участки (модули), так и на группу последовательно соединенных запоминающих модулей, которая в этом слу- 45 чае рассматривается как один участок, Как следует из схемы соединения разрядных обмоток запоминающих модулей (фиг.1), выполненной по правилу ортогональной матрицы (фиг.2), для которой справедливо соотношение л

Магнитный накопитель, содержащий и запоминающих модулей, где и кратно

4, с адресными обмотками и с m разрядными обмотками, где m ф 2, n/2 разрядных обмоток накопителя соединены согласно друг с другом и встречно по отношению к другим разрядным обмоткам, о т л и,ч а ю шийся тем, что, с целью повышения помехоустойчивости накопителя,в нем для любых двух разрядных обмоток накопителя n/4 разрядных обмоток запоминающих модулей соединены согласно друг другу и однонаправленно, другие и /4 разрядных обмоток запоминающих модулей соединены согласно друг другу и встречно по отношению к первым и /4 разрядным обмоткам запоминающих модулей, третьи n/4 разрядных обмоток запоминающих модулей соединены встречно друг другу и встречно по отношению к четвертым n/4 разрядным обмоткам запоминающих модулеи.

858096

4 4 к s s

Фиа!

Составитель В. Гордонова

Редактор В.Иванова Техред А.Бабинец Корректор О.Билак

Заказ 7255/84 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Фи.стипл ППП "Патент", r. Ужгород, ул. Проектная, 4