Устройство управления преобразователем аналог-код последовательного приближения

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<щ858206

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 030779 (21) 2788841/18-21 с присоединением заявки HP (23) Приоритет—

Опубликовано 2308.81. Бюллетень NP 31

Дата опубликования описания 23.0881 (gg) К 3

H 03 K 13/00

Государственный комитет

СССР по делам изобретений н открытий (53) УДК 681.325 (08e.8) (72) Авторы изобретения

A. В. Тамошюнас и В. В. Смирнов (73) Заявитель (54 ) УСТРОЙСТВО УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЕМ

АНАЛОГ-КОД ПОСЛЕДОВАТЕЛЬНОГО ПРИБЛИЖЕНИЯ

Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано, в частности в преобразователях аналоговых сиг- > налов в цифровой код.

Известно устройство управления преобразователем, сбдержащее триггер запуска, формирователь задержанных импульсов, элементы И,. И-НЕ, схему стробирования выходного сигнала элемента сравнения, регистр, каждый разряд которого содержит управляющий элемент И-НЕ и два триггера, состоящие из одного элемента И-ИЛИ-НЕ с входами триггерной связи и установки, 15 элемента И-НЕ для первого триггера и элемента НЕ для второго триггера, шину тактирующих импульсов и шину начальной установки (1).

Недостатком данной схемы является низкая надежность и малое быстродействие преобразования.

Цель изобретения — повышение надежности и увеличение быстродействия при сохранении точности преобразования.

Поставленная цель достигается тем, что в известном устройстве управления преобразователем аналог-код после. довательного приближения, содержащее 30 блок управления, выполненный на уйрав ляющем элементе И-HE и триггере на элементах И-HE выход которого соединен с первыми входами счетчика, выполненного на делителях частоты, выходы которого соединены со входом дешифратора, блок позирования из в-ячеек сохранения-сброса, каждая из которых выполнена на двух элементах И-НЕ, и m-разрядных триггеров, выполненных на двух элементах И-НЕ для каждого разряда, при этом дополнительный устанавливающий вход каждого из них соединен с выходом соответствующей ячейки сохранения-сброса, шину "Пуск", соединенную с первым входом блока управления и вторыми входами счетчика, шину "Тактовая частота", „соединенную со вторым входом блока управления, первый выход дешифратора подключен к устанавливающему входу разрядного триггера старшего значению разряда и к дополнительным сбрасывающим входам разрядных триггеров последующих разрядов до младшего значения разряда включительно, а также и первым входам ячеек сохранения-сброса всех разрядов, каждый иэ последующих m-выходов дешифратора подключены к сбрасывающему входу разрядного триггера предыдуще858206 го значащего разряда, и к устананливающ ему входу разрядного триггера данного разряда, а также ко второму . входу ячейки сохранения-сброса данного значащего разряда, последний выход дешифратора подключен к сбрасынающему входу разрядного триггера младшего значащего разряда и к третьему нходу блока управления, неинвертирующие выходы разрядных триггеров подклнчены к третьим входам ячеек сохранения сброса соответствующих разоярядов, инвертирующие выходы разрядных триггеров,,начиная с триггера следующего эа триггером старшего значащего разряда подключены к пятым входам ячеек сохранения-сброса предыдущих I5 разрядов, а выход компаратора подключен к четвертым выхоцам ячеек сохранения-сброса всех разрядов.

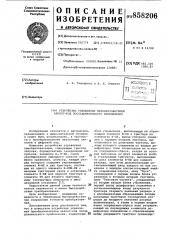

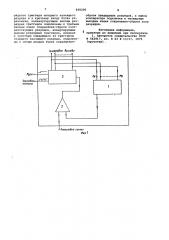

На фиг. 1 представлена блок-схема аналого-цифрового преобразователя О (АЦП) последовательного прибли>кения; на фиг. 2 — устройство управления

m-разрядного АЦП последовательного приближения; на фиг. 3 — временная диаграмма к примеру 1; на фиг. 4 временная диаграмма к примеру 2.

Схема приводимого аналого-цифрового преобразователя (АЦП) поразрядного взвешивания включает в себя цифроаналоговый преобразователь 1 (ЦАП), ком-. паратор 2 и устройство управления 3 (фиг. 1)

Структурная схема устройства управления содержйт блок 4 управления, счетчик 5,дешифратор б с выходами б-1... б (m+

+3 ), блок 7 кодирования, шину 8 тактовой З частоты, шину 9 "Пуск", шину 10 компаратора.

Шина 9 "Пуск" соединена с первым входом блока 4 управления и вторым входом счетчика 5, выходы которых со- 40 единены со входами дешифратора б, шина 8 тактовой частоты соединена со вторым входом блока 4 управления, выход которого соединен с первыми входами счетчика 5. 45

Блок управления состоит из управляющего элемента И-HE и триггера, построенного на элементах И-НЕ, выход которого связан со входом управляющего элемента И-НЕ. Счетчик 5 состоит из делителей на два, так что выход предыдущего связан со входом последующего.

Блок 7 кодирования состоит иэ я-ячеек 11 сохранения-сброса, построен ных на двух элементах И-НЕ,и m-разряд- ных триггеров 12, построенных на двух элементах И-HE.

Перный выход 6-1 дешифратора подключен к устанавливающему входу S-разрядного триггера старшего энач-щего @) разряда и к допОлнительным сбрасывающим входам R-разрядных триггеров 12 последующих разрядов до лладшего значащего разряда включительно, а также к первым входам ячеек сохранения- у сброса всех разрядов, второй выход

6-2 дешифратора подключен к сбрасывающему входу R-разрядного триггера 12 старшего значащего разряда и к устанавливающему входу 5-разрядного триггера 12, следующего за старшим значащим разрядом, а также ко второму входу ячейки сохранения-сброса следующей за ячейкой старшего значащего разряда, аналогичным образом соединенные последующие выходы дешифратора 6-3-6-(m+1) с разрядными триггерами и ячей ка сохранения †сбро блока 7 кодирования,при этом последний выход 6-(m+1) дешифратора соединен с третьим входом блока 4 уПравления, выходы ячеек сохранения-сброса соединены с дополнительными устанавливающими входами

S< -разрядных триггеров тех же разрядов, неинвертирующие выходы разрядных триггеров 12-1Р-12-m подключены к третьим входам ячеек сохранения-сброса соответствующих разрядов, инвертирующие выходы 12-2....12-m-разрядных триггеров 12, начиная с триггера, следующего эа триггером старшего значащего разряда, подключены к пятым входам ячеек сохранения-сброса предыдущих разрядов, а шина компаратара подключена к четвертым входам ячеек сохранения-сброса всех разрядов.

Преобразователь аналог-код и устройство управления работают следующим образом.

При подаче сигналов "Пуск" и "Тактовая частота" на блок 4 управления, а также сигнала "Пуск". на первый вход счетчика 5 на выходах дешифратора 6 (фиг. 2) последовательно набираются комбинации (01...1), (101...1), (1101...1),... (11...10) (фиг. 3 и 4)

При соответствующем аналоговом напряжении на входе АЦП на выходах

12-1-12-m АЦП (фиг. 2) набирается цифровая комбинация 111...., при этом компаратор в течение цикла преобразования находится н состоянии логическоro нуля (фиг. 3, линия К), что является признаком сохранения раэрядон во включенном состоянии.

Комбинация (01...1) на выходах дешифратора 6 вызывает, комбинацию (110...) на входах й., S<, 5-разрядного триггера старшего разряда, что приводит к единичному логическому уровню на выходе 12 1, т. е. к включению старшего значащего разряда (СР)

ЦАП; при этом на нходах R<,R, S<„ Sразрядных триггеров млатцаего разряда возникает цифровая комбинация 0111, что приводит к нулевому логическому уровню на выходах 12-2-12-m, т. е. к выключению остальных разрядов IJAII (фиг. 2, 3 и 4), Последующая комбинация 101...1 на выходах дешифратора вызывает комбинацию 001 на входах R, 5, S-разрядного триггера старшего разряда, что сохраняет предыдущее состояние логической

858206 единицы на выходе 12-1, а на входах

Rz, R, S, S-разрядного триггера 12, следующего за старшим значащим разрядом возникает цифровая комбинация

1110, что приводит к единичному логи- ческому уровню на выходе 12-2, при этом на входах остальных Во, R, S<, S-разрядйых триггеров вознйкает цифровая комбинация 1111, которая сохраняет нулевые логические уровни на

1 выходах 12-3-12-m (фиг. 2 и 3), !

О

Аналогичным образом происходит . включение последующих разрядов и сохранение их во включенном состоянии.

При появлении комбинации 11...10 на выходах 6-1...6-(m+1) дешифратора, нулевой логический уровень с выхода ! б-(в+1) поступает на блок 4 управления и останавливает счет (фиг. 2) .

При подаче на аналоговый вход АЦП напряжения, которое эквивалентно цифровому коду 010... на выходе АЦП . 20 (фиг. 4) и при возникновении дешифрирующей комбинации 01...1 на выходах дешифратора 6-1-б-(m+1) на выходах

12-1-12-я возникает цифровой код

10.... Так как аналоговый сигнал, снимаемый с выхода ЦАП,превышает текущее значение аналогового сигнала на входе АЦП, компаратор устанавливает логический уровень "1" на входах

"4" ячеек сохранения-сброса младшего разряда (фиг. 2 и 4) . Логический уровень "1" на входе "4" ячейки сохранения-сброса старшего разряда не способен установить разрядный триггер старшего разряда в состояние логиеского нуля на выходе 12-1, так как состояние триггера фиксируется комбинацией (10) на его RS-входах посредством комбинации (01) на выходах 6-1—

6-2 дешифратора; при этом состояние выходов 12 — 2-12-m не изменяются в свя40 зи с тем, что на входах R, R, 5<, 5-разрядных триггеров 12 остальных разрядов сохраняется комбинация 0111 (фиг. 2 и 4) .

При возникновений последующей .дешифрирующей комбинации 101...1 на выходах дешифратора логический уровень

"0" с выхода 6-2 подается на R-вход разрядного триггера старшего разряда, 5,) а на S-вход подается логическая "1" с выхода 6-1 (фиг. 2, 4) . В связи с логической задержкой распространения цифровых сигналов, логический уровень

"1" некоторое время сохраняется на

S -входе разрядного триггера старше4 го разряда (Фиг. 2) . Таким образом, на RS< S-входах разрядного триггера с .аршего разряда Набирается комбина,ция (011), переустананливающая выход 12-1 в состояние логического "0" 6Q (что соответствует выключению старшего разряда ЦАП) . Значение логического уровня сигнала комларатора в дальнейшем не оказывает,.влияния на состояние разрядного триггера старшего 65 разряда, так как логический "0", сни" маемый с выхода 12-1 удерживает вход

S в состоянии логической "1". На вйходах 12-2-12-m-разрядных триггеров остальных разрядов возникает комбинация 10...0 (фиг. 2 и 4) .

Аналогичным образом происходит включение последующих разрядов а также их: выключение в зависимости от

° соотношения между величинами аналоговых сигналов на входе АЦП и выходе

РАП.

Рассмотренные принципы построения устройства управления позволяют на

К-блоках делителей частоты реализовать в ц„ = 2К-1-разрядный АЦП. При этом полный цикл работы АЦП составля-. ет 2К периодов тактовой частоты (фиг. 1 и 2) .

Предлагаемый преобразователь может найти широкое применение в электромузыкальных инструментах.

Формула изобретения

Устройство управления преобразователем аналог-код последовательного приближения, содержащее блок управления, выполненный на управляющем элементе И-НЕ и триггере на элементах .

И-НЕ, выход .которого соединен с первыми входами счетчика, выполненного на делителях частоты, выходы котэрого . соединены со входом дешифратора, блок кодирования из m-ячеек сохранениясброса, каждая из которых выполнена на двух элементах И-НЕ, и m-разрядных триггеров, выполненных на двух элемента И-НЕ для каждого разряда, при этом дополнительный устанавливающий вход каждого иэ них соединен с выходом соответствующей ячейки сохранения-сброса, шину "Пуск", соединенную с первым входом блока управления и вторыми входами счетчика, шину "Тактовая частбта", соединенную со вторым входом блока управления, о т л и— ч а ю щ е е с я тем, что, с целью повышения надежности и увеличения быстродействия при сохранении точности преобразования, первый выход дешифратора подключен к устанавливающему входу разрядного триггера старшего значащего разряда и к дополнительным сбрасывающим входам разрядных триггеров последующих разрядов до младшего значащего разряда включительно, а также к первым входам ячеек сохранения-сброса всех разрядов, каждый из последующих а-выходов дешифратора подключены..к сбрасывающему входу разрядного.триггера предыдущего значащего разряда и к устанавливакицему входу разрядного триггера данного разряда, а также ко второму входу ячейки сохранения-сброса данного значащего разряда, последний выход дешифратора подключен к сбрасывающему входу раз858206

7аттюдая

voemoma рядного триггера младшего значащего разряда и к третьему входу блока уп" равления, неинвертирующие выходы разрядных триггеров подключены к третьим входам ячеек сохранения-сброса соответствующих разрядов, инвертирующие выходы разрядных TpHrrepoB, начиная 5 с триггера следующего за триггером старшего значащего разряда, подключены к пятым входам ячеек сохранения".сброса предыдущих разрядов, а выход комиаратора подключен к четвертым выходам ячеек сохранения-сброса всех разрядов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 562917, кл. Н 03 К 13/17, 1975 (прототип) .

858206

Ь-2 йитФм чвееатю

ЯНОмгобай сигнал

12-2

Составитель А. Кузыецов

Редактор Н. Хончвцкая Техред М. Рейвес; Корректор С, щщмар

Заказ 7265/90

ФЯ

Алмемйв гикал

Ч. нраж 988 Подннсное

ВНИИПИ,.Государственного комитета СССР по,делам изобретений и открытий

113035, Москва, %-35, Рауыска» наб., д. 4/5

° ВЮ I

Филиал НПП "Патент", г. Уагород, ул. Проектная, 4