Многоканальный преобразователь частоты в код

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистичеснмх

Республик

ОП ИКАНИЕ

ИЗОБPETE Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii) 859944 (61) Дополнительное н авт. свид-ву— (51)М. К.л. (22) Заявлено 09.12.77 (21) 2554335/18-21 с присоединением заявки ¹â€” (23) Приоригет— 6 01 R 23/02

И 03 К 13/20

5ееуаарстеенаы6 комитет

СССР ао делам изобретений и етерытнй

{ З) УДК 621.317. .7б1 (088.8}

Опублнновано 30.08.81.. Бюллетень № 32

Дата опубликования опксания 30.08.81 (72) Авторы изобретения

В. П, Жабеев, В. И. Королькевнч и В. А. Кротев

Киевское проектно-конструкторское бюро автома систем унравления (73) Заявитель (54} МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

ЧАСТОТЫ В КОД

Изобретение относится к преобразованию и кодированию информации и может быть использовано в многоканальных нйформационноизмерительных системах с автоматической обработкой данных на ЦВМ.

Известен преобразователь частоты в код, содержащий входной блок, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом автогенератора, первый выход — со входом первого

1О счетчика, а второй выход — со входом морого счетчика, выход которого через узел для формирования системы команд соединен со входом автогенератора, а выход первого счетчи; ка подключен ко входу выходного блока и перво. .му входу блока сравнения, второй вход которого

15 соединен с выходом блока памяти,а выход — со входом блока памяти н входом блока для формирования системы команд Я

Известен другои преобразователь частоты в код, содержащий элемент И, первый вход которого сое. динен с источником входного сигнала, второй входе первым входом счтетчика импульсов, второй вход которого соединен со вторым выходом программирующего устройства, первый выход — со входом буферного регистра, а второй выход с первым входом блока сравнения, второй вход которой подключен к первому выходу буферного регистра, а выход — к первому входу блокирующего устройства, второй вход которого соединен с третьим выходом программирующего устройства, а выход — со вторым входом буферного регистра, второй выход которого подключен к цифровому индикатору (2).

Недостатком та нного устройства также является большое количество оборудования при многоканальном преобразовании частоты в код.

Наиболее близким о технической сущности н достигаемому результату к предлагаемому изобретению является многоканальный преобразователь частоты в код, содержащий блок памяти, первые входы которого соединены с выходами элементов И, первые входы которых соединены с первым выходом генератора калиброванной частоты и с первым входом измерительного счетчика, а вторые входы — с

i соответствующими выходами измерительного

;счетчика, второй вход которого соединен с

859944 первым выходом блока управления, вход которого подключен к выходу дополнительного элемента И, а второй выход — в каждом канале с R-входом триггера и первым входом счетчика импульсов, второй вход которого соединен с выходом блока установки коэффициента пересчета, а выход — с соответствующим входом дополнительного элемента И, первым входом первого генератора одиночных импульсов и первым входом элемента ЗАПРЕТ второй вход которого подключен к соответствующему источнику входных сигналов, а выход — к третьему входу счетчика импульсов и S-входу триггера, выход которого соединен с первым входом второго генератора одиночных импульсов, причем вторые входы первого и второго генераторов одиночных импульсов в каждом канале подключены ко второму выходу генератора калиброванной частоты, а вы.ходы — ко вторым входам блока памяти (31.

Недостатком данного устройства является

его сложность.

Цель изобретения — упрощение устройства.

Указанная цель достигается тем, что, в многоканальном преобразователе частоты в код, содержащем измерительный счетчик, первый вход которого соединен с первым выходом генератора калиброванной частоты, а второй вход — с выходом блока управления, вход ко. торого соединен с выходом элемента И, и в каждом канале — триггер, выход которого соединен с первым входом генератора одино щых импульсов, S-вход — с выходом элемента ЗА-

ПРЕТ и с первым входом счетчика импульсов, второй вход которого соединен с выходом блока установки коэффициента пересчета, а выход — с соответствующим входом элемента И и первым входом элемента ЗАПРЕТ, второй вход которого соединен со входом преобразуемого сигнала, причем R-вход триггеров и третий вход счетчиков импульсов всех каналов соединентл с выходом блока управления, вторые входы генераторов одиночных импульсов— со вторым выходом генератора калиброванной частоты, а выходы генераторов одиночных импульсов — с первыми входами блока памяти, выходы генераторов одиночных импульсов через элемент ИЛИ подключены к дополнительному входу блока памяти и входу счетчика адреса, выходы которого соединены со вторыми входами блока памяти, третьи входы которого соединены с выходами измерительного счетчика, а дополнительный выход счетчика импульсов в каждом канале соединен с дополнительныМ R-входом триггера.

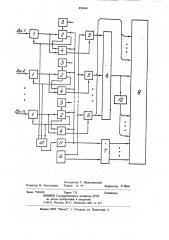

На чертеже приведена блок-схема многоканального преобразователя частоты в код.

Устройство содержит в каждом из каналов 1 элемент ЗАПРЕТ 1, счетчик 2 импульсов, блок

3 установки коэффициента пересчета, триггер 4 и генератор 5 одиночных импульсов. Общими узлами для всех каналов преобразователя являются генератор 6 калиброванной частоты, измерительный счетчик 7, элемент ИЛИ 8, блок

9 памяти, элемент И 10, блок l l управлелия и счетчик 12 адреса.

ro Устройство работает следующим образом.

Перед началом измерений в зависимости от диапазона входных сигналов и требуемой точности преобразования в каждом канале с помощью блоков 3 установки коэфф»ц»ента пересчета задаются соответствующие коэффициенты для счетчиков 2 импульсов.

Пр» каждом ц»кле»змсрений блок 11 управления формирует сигнал для установки в исходное состоян»с счетчиков 2»мпульсов и триггеров 4. При этом измер»тельный счетчик 7 наг»пает отсчитывать импульсы генератора 6 калиброванной частоты. Триггер 4 фиксирует момент появления первого импульса па выходе элемента ЗАПРЕТ 1» уста»авливастся в единичное состояние, разрешая прохождение импульсов генератора 6, сдвинутых по фазе относительно импульсов отсчета, через генератор 5 одиночных импульсов на соответствующий первый вход блока 9 памяти (каждому входу капала соответствует олин разряд блока памяти), а через элемент ИЛИ вЂ” на дополнительный вход блока 9 памяти (вход записи), Кроме записи разряда соответствующего капала импульсом с генератора 5 в блок 9 памя35 ти записывается код измерительного счетчика 7 по третьим входам блока 9.

Таким образом, при появлении импульса в любом канале измерения или в нескольких каналах в блок 9 памяти записывается код»з4О мерительного счетчика 7 и код признаков канала или нескольких ка»алов.

После поступления и — 1 импульса в счетчик 2 импульсов триггер 4 вновь устанавливается в исходное нулевое состояние. После поступления

45 n — 1 импульса в счетчик 2 импульсов триггер 4 вновь устанавливается в единичное состояние и соответствующий этому моменту, времени код измерительного счетчика 7 записывается в блок 9 памяти. Счетчик 2 импульсов при

5О эТом запрещает прохождение импульсов через элемент ЗАПРЕТ 1 соответствующего канала.

В режиме считывания информации из блока 9 памяти по кодам признаков каналов определяются коды измерительного счетчика 7 соответsS ствующего канала на момент прихода первого и и-го импульсов счета.

Момент окончания счета на счетчиках 2 импульсов во всех каналах формируется сигналом

859944 окончания измерений на выходе элемента И 10, поступающим на вход блока 11 управления, Вычисление .измеренных значений частоты производится по формуле

1 Fy. И

Н11 80

Формула изобретения 30

Многоканальный преобразователь частоты в код, содержащий измерительный счетчик, первый вход которого соединен с первым выходом генератора калиброванной частоты, а вто-Зч.а де f — результат измерения в i-ом канале;

F — калиброванная частота, к п — коэффициент пересчета в .i-ом

1 канале;

Й - — код измерительного счетчика

01 в момент начала отсчета в 15

i-ом канале, М вЂ” код измерительного счетчика

41 после заполнения пересчетной схемы в i-ом канале.

Экономическая эффективность предлагаемого 20 устройства заключается в значительном упрощении его по сравнению с известными устройствами.

Анализ предлагаемого устройства показывает, что его аппаратурные затраты на 10 — 15% . 25 меньше аппаратурных затрат на известные устройства. рой вход. — с выходом блок управления, вход которого соединен с выходом элемента И, и в каждом канале — триггер, выход которого соединен с первым входом генератора одиночных импульсов, S-вход — с выходом элемента

ЗАПРЕТ и с первым входом счетчика импульсов, второй вход которого соединен с выходом блока установки коэффициента пересчета, а выход — с соответствукнцим входсм элемента И и первым входом элемента ЗАПРЕТ, второй вход которого соединен со уходом преобразуемого сигнала, причем Я-вход триггеров и третий вход счетчиков импульсов всех каналов соединены с выходом блока управяеиия, вторые входы генераторов одиночных импульсов— со вторым выходом генератора калиброванной частоты, а выходы генераторов одиночных импульсов — с первыми входами блока памяти, о т л и ч а -ю шийся тем, что, с целью упрощения, выходы генераторов одиночных импульсов через элемент ИЛИ подключены к дополнительному входу блока памяти ы входу счетчика адреса, выходы которого соединены со вторыми входами блока ламяш, третьи входы которого соединены с выходами измерительного счетчика, а дополнительный выход счетчика импульсов в каждом канале соединен с дополнительным R-входом триггера.

Источники информации. принятые во внимание при экспертизе

1. Патент США У 4025868, кл. 324 — 78, 1977.

2. Патент С111А Р 3909716, кл. 324 — 78 О, 1975.

3. Авторское свидетельство СССР Н4 598237, кл. Н 03 К 13/24, 1975 (прототип).

859944

Корректор Л. Иван

Заказ 7540/68 Тираж 732

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель Г. Милославский

Редактор М. Лысогорова Техред А. Ач