Источник калиброванных напряжений

Иллюстрации

Показать всеРеферат

Союз Советски к

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву № 758095 (22) Заявлено 04.09.79 (21) 2816637/24-07 с присоединением заявки №вЂ” (23) Приоритет—

Опубликовано 30.08.81. Бюллетень №32

Дата опубликования описания 31.08.81 (51) М.К .

G 05 F 1/00

Гооударстееннмй комитет ло делам нзооретеннй н открытий (53) УДК 621.316. .722.1 (088.8) (72) Авторы изобретения

А. Е. Волынский, P Э. Капиев, С. А. Рачий и A. А.Схгирнов1 (71) Заявитель (54) ИСТОЧНИК КАЛИБРОВАННЫХ НАПРЯЖЕНИЙ

Изобретение относится к электротехнике, в частности к источникам калиброванных напряжений.

По основному авт. св. № 758095 известен источник калиброванных напряжений, содержащий блок опорного напряжения, коммутатор, первый блок интегрирования, регистр памяти, преобразователь кода во временной интервал и блок управления, причем выход блока опорного напряжения соединен с первым входом коммутатора, выход которого подключен ко входу первого блока интегрирования, вход регистра памяти соединен с входной клеммой, выход подключен ко входу преобразователя кода во временной интервал, а вход сигнализации регистра памяти соединен с соответствующим выхоооом блока управления, при этом выход преобразователя кода во временной интервал через блок управления подключен к первому и второму управляющим входам коммутатора, а также преобразователь «код-напряжение», второй блок интегрирования и аналоговый сумматор, первый блок интегрирования дополнительно снабжен входом сброса, причем вход преобразователя «коднапряжение» соединен с дополнительным входом регистра памяти, выход данного преобразователя подключен к первому входу аналогового сумматора, выход первого блока интегрирования соединен со входом второго блока интегрирования, выход которого подключен ко второму входу аналогового сумматора, выходом соединенного с выходной клеммой и вторым входом коммутатора, а вход сброса первого блока интегрирования и вход управления второго блока интегрирования соединены с соответствующими выходами блока управления.

Выходное напряжение данного устройства достигает в. течение п циклов установившегося значения. где Š— опорное напряжение;

Т вЂ” постоянный временной интервал;

T> — временной интервал, пропорциональный входному коду N, Тх = ;

f — тактовая частота на входе пересчетного устройства, входящего в состав преобразователя кода во временной интервал, причем fT = q = const (1).

860021

1.т (4 1

Однако для заданной величины Тх пка разрешающая способность преобразователя кода во временной интервал и всего устройства в целом определяется допустимой величиной f. Последняя ограничивается возможностями формирующих схем и цифровых элементов, входящих в состав пересчетного устройства. Так, при разрешающей способности устройства 10 и Txm« — — 20 мс необходимо обеспечить f = 500 МГц, что не реализуется на интегральных элементах.

В свою очередь уменьшение данной частоты сопряжено с увеличением длительности итерационного цикла и, следовательно, приводит к снижению быстродействия источника калиброванных напряжений.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в источник калиброванных напряжений введены источник опорного тока и ключ, причем выход источника опорного тока через ключ связан с дополнительным входом первого блока интегрирования, а дополнительный выход преобразователя кода во временной интервал через блок управления связан с управляющим входом ключа.

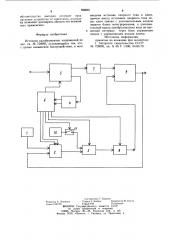

На чертеже представлена структурная схема предлагаемого устройства.

Источник калиброванных напряжений содержит блок 1 опорного напряжения, коммутатор 2, первый блок 3 интегрирования, преобразователь 4 кода во временной интервал, регистр 5 памяти, блок 6 управления, преобразователь 7 «код-напряжение», второй блок 8 интегрирования, аналоговый сумматор 9, источник 10 опорного тока и ключ 11.

Устройство работает следующим образом, По команде блока 6 управления входной код N переписывается в регистр 5, при этом на выходе преобразователя 7 «код-напряжение» устанавливается пропорциональное данному коду напряжение Е!, а выходное напряжение сумматора 9 определяется выражением

1- вых (t) = — 4 iE> — 1!а Uy(t) г (I) где u,(t) — напряжение на выходе блоке 8; — коэффициенты передачи сумматора 9 по соответствующим входам.

Итерационный процесс установления выходного напряжения устройства осуществляется за п циклов. В начале очередного

i-го цикла блоком 6 производится сброс первого блока 3 интегрмрования, по окончании сброса выход блока 1 опорного напряжения через коммутатор 2 подключается ко входу блока 3, и опорное напряжение E интегрируется в течение интервала времени

Тх! . Этот интервал, пропорциональный числу

N!, представляющему К старших разрядов

5-разрядного кода N = Nq+ 1 1г (c основанием 1, вырабатывается преобразователем 4 и через блок 6 подается на первый

5 !

0 !

Зо

55 управляющий вход коммутатора 2. Одновременно на дополнительном выходе преобразователя 4 формируется временной интервал Ъг, длительность которого пропорциональна числу Хг, представляющему

S-К младших разрядов кода. Этот интервал через блок 6 подается на управляющий вход ключа 11, и в течение его выходной ток источника 10 1 = —, (1 + Я), где R — масЯ К штабное сопротивление по основному входу блока 3, а б — относительное отклонение величины 1 от номинального значения, поступает на дополнительный вход блока 3 и интегрируется. По окончании данной части цикла, длительность которой составляет

max(Tx, T ), вход блока 3 через коммутатор подключается к выходу сумматора 9, и производится интегрирование выходного напряжения последнего U (i — 11 в течение постоянного временного интервала Т.

По окончании данного интервала напряжение на выходе блока 3 имеет вид

Ц(1= i«,, (

= fF„(T <+Тхг (. (1,Х.))U х1!-!)ТI >

Т, где Т» = RC — постоянная времени по основному входу блока 3. Данное напряжение подается на вход блока 8 и интегрируется в течение постоянного временного интервала Т . На выходе блока 8 по окончании этой операции формируется напряжение

u;(i)=u (i-Ö-=„,u, Ит„=u,(о)-=, Z u, fm), ОЭ = 1

® где 1!г (i — 1) — выходное напряжение блока 8 в соответствующий момент i — 1-ro цикла; !.г — постоянная времени блока 8.

Аналогично основному устройству можно показать, что установившееся значение выходного напряжения сумматора 9, формируемого в соответствии с (1), принимает вид (""-. 3 5 5 я/вых.уст.= 1- =-Е ! х! -к и (М где Т = —, j =1,2. и .

Из выражения (4) следует, что влияние величины <5 на выходной сигнал источника калиброванных напряжений ослабляется в

J. раз.

Таким образом, предлагаемое устройство практически не снижает точность известного и обеспечивает требуемый динамический дна пазон выходных сигналов. Однако в отличие от известного устройства разбиение входного кода на старшие и младшие разряды и разделение операций интегрирования соответствующих опорных сигналов позволяет на нескол ько порядков уменьшить тактовую частоту преобразователя кода во временной интервал, и обеспечивая при заданной разрешающей способности существенное повышение быстродействия источника калиброванных напряжений. Последнее

860021

Формула изобретения

Составитель Т. Ершова

Редактор А. Лежнина Техред А. Бойкас Корректор М. Коста

Заказ 7547/32 Тираж 940 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 обстоятельство выгодно отличает предлагаемое устройство от известного, поскольку позволяет расширить область его возможного применения.

Источник калиброванных напряжений по авт. св. № 758095, отличающийся тем, что, с целью повышения быстродействия, в него введены источник опорного тока и ключ, причем выход источника опорного тока через ключ связан с дополнительным входом первого блока интегрирования, а дополнительный выход преобразователя кода во временной интервал через блок управления связан с управляюшим входом ключа.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 758095, кл. G 05 F 1/100, 04.04.79.