Источник калиброванных напряжений

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсних

Социалистичесник

Республик

«ii860025 (61) Дополнительное к авт. свид-ву № 758095 (22) Заявлено 13.09.79 (21) 2819032/24-07 с присоединением заявки №вЂ” (51) М К

G 05F 1(56

Государственный комитет (53) УДК 621.316. .722.1 (088.8) Опубликовано 30.08.81. Бюллетень № 32

Дата опубликования описания 31.08.81 по делам изобретений и открытий (72) Авторы изобретения

А. Е. Волынский, P. Э. Капиев, В. И. Полствин,.

С. А. Рачин и А. А. Смирнов

/ с

I (71) Заявитель (54) ИСТОЧНИК КАЛИБРОВАННЫХ НАПРЯЖЕНИЙ

Изобретение относится к электротехнике, в частности к источникам калиброванных напряжений.

По основному авт. св. № 758095 известен источник калиброванных напряжений, содержащий блок опорного напряжения, коммутатор, два блока интегрирования, преобразователь кода во временной интервал, регистр памяти, преобразователь код-напряжение, аналоговый сумматор и блок управления, причем первый и второй входы коммутатора соответственно связаны с выходами блока опорного напряжения и аналогового сумматора, выход коммутатора через последовательно включенные блоки интегрирования связан со вторым входом аналогового сумматора, а первый и второй входы управления коммутатора через блок управления связаны с выходом преобразователя кода во временной интервал, вход регистра памяти соединен со входной клеммой, а его соответствующие выходы подключены ко входам преобразователя кода во временной интервал и преобразователя <код-напряжение», выход преобразователя «коднапряжение» соединен с первым входом аналогового сумматора, выход последнего связан с выходной клеммой, а вход сброса первого блока интегрирования, вход управления второго блока интегрирования и вход синхронизации регистра памяти соединены с соответствующими выходами блока управления(11.

Устройство работает следующим образом.

Текущее значение сигнала на выходе аналогового сумматора U<>„(t) является взвешенной суммой выходного сигнала пре10 образователя <код-напряжение» Е1 и выходного напряжения второго блока интегрирования Ug(t) и устанавливается за несколько циклов. В течение каждого i-го цикла производится начальный сброс первого блока интегрирования и на его выходе формируется функция поправки в виде напряжения

11 (1) = — ф (ЕТ„+ U„« t — 11т +

+ е (Т„1- fj}", (1) 20 гдеТ1 — постоянная времени данного блока; е — напряжение смещения блока;

Š— опорное напряжение;

860025

5 lO г Тх

1- вых.уст= - 1(3), (т„. .g Я

1 ГЕТХ

u,(ii) =- =„, «0 (6) 50

Т и Тх — постоянный и переменный временные интервалы, причем по:ледний вырабатывается пропорционально коду «11» регистра памяти преобразователем кода во временной интервал.

Полученная таким путем функция поправки интегрируется далее в течение постоянного временного интервала То вторым блоком интегрирования с постоянной времени Т2, а результат интегрирования суммируется в данном устройстве с величиной

1- 2 (1) °

U2 (i) = =U (i) + U> (i — 1) °, (2) Данное напряжение воздействует с весом 2 на выходное напряжение устройства, которое при выполнении условия (1 — — Б) <<

7 2

C(1 и при е= 0 быстро сходится к установившемуся значению

Однако с учетом напряжения смещения первого блока интегрирования (е О) в последнее выражение вносится погрешность. относительная величина которой 0 = — (1 +

+ — ) зависит от нестабильного параметра е

Т т„ и, следовательно, не может быть устранена одноразовой настройкой первого блока интегрирования.

Цель изобретения — повышение точности источника калиброванных напряжений.

Поставленная цель достигается тем, что в источник калиброванных напряжений введен второй коммутатор, первый блок интегрирования дополнительно снабжен инверсным входом, второй блок интегрирования дополнительно снабжен вторым входом управления, а блок управления — тремя дополнительными выходами, причем первый и второй входы второго коммутатора соединены с соответствующими входами первого коммутатора, выход второго коммутатора подключен к инверсному входу первого блока интегрирования, а три дополнительных выхода блока управления соответственно связаны с первым и вторым управляющими входами второго коммутатора и вторым входом управления второго блока интегрирования.

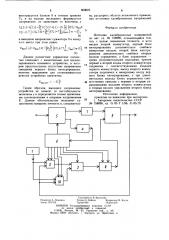

На чертеже приведена структурная схема предлагаемого устройства.

Источник калиброванных напряжений содержит блок 1 опорного напряжения, коммутатор 2, первый блок 3 интегрирования, преобразователь 4 кода во временной интегвал, регистр 5 памяти, блок 6 управления, преобразователь 7 «код-напряжение>, второй блок 8 интегрирования, аналоговый сумматор 9, второй коммутатор 10.

Устройство работает следующим образом.

По команде управления блока 6 входной код «11» переписывается в регистр 5 памяти, при этом на выходе преобразователя 7 «коднапряжение» устанавливается пропорциональное данному коду напряжение Е, а выходное напряжение сумматора 9 определяется выражением

U t) = ) 1E1 1 21 2 (t) (4) где v,() — напряжение на выходе блока 8, — коэффициенты передачи сумматора 9 по соответствующим входам.

Итерационный процесс установления выходного напряжения подобно основному устройству осуществляется в течение п циклов, однако в каждом i-ом цикле процесс интегрирования соответствующих сигналов блоками 3 и 8 занимает два равных по длительности такта. В начале первого такта производится сброс первого блока 3 интегрирования, а по окончании сброса выход блока 1 опорного напряжения через коммутатор 2 подключается ко входу блока 3, и опорное напряжение Е интегрируется в течение интервала времени Тх /2. Данный интервал, пропорциональный коду N, вырабатывается как и в основном устройстве преобразователем 4 и подается на соответствующий управляющий вход коммутатора 2. По окончании данной части такта вход блока 3 через коммутатор 2 подключается к выходу сумматора 9 и производится интегрирование выходного напряжения последнего Us (i — 1) в течение постоянного временного интервала Т/2. К концу данного интервала напряжение на выходе блока 3 имеет вид

Данное напряжение поступает на вход блока 8 и интегрируется в течение времени То, на выходе последнего при этом формируется напряжение

1./, l .1)=U,Li-1)-=ДU, И, To I

Далее начинается второй такт, в начале которого производится сброс блока 3, направление интегрирования блока 8 по сравнению с первым тактом меняется блоком 6 на противоположное и выход блока 1 через второй коммутатор 10 в течение интервала

Тх/2 подключается к инверсному входу блока 3, а в оставшейся части такта инверсный вход блока 3 через коммутатор 10 в течение интервала Т/2 подключается к выходу сумматора 9. Полученное в результате данных операций выходное напряжение блока 3 и - l l Е 1х 1./ьых (1-1)Т (Тх +Т) (7) 860025

Формула изобретения т.

1-1вых. уст. т

Составитель В. Круглова

Редактор А. Лежнииа Техред А. Бойкас Корректор М. Коста

Заказ 7547/32 Тираж 940 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, % — 35, Раун)скан наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4 интегрируется блоком 8 в течение времени

T)) и на выходе последнего формируется напряжение, не зависящее от величины е

U, (i) )), ()) =, U," ()) -

U»y (n)=U»>(o) - ет„п тх Uz,„(rn.l))

8)

Данное разностное управление полностью совпадает с аналогичным для идеализированного основного устройства, в кото15 ром предполагалось отсутствие напряжения смещения первого блока интегрирования, поэтому выражения для установившегося режима устройства идентичны

Таким образом, выходное напряжение устройства не зависит от нестабильности величины е и определяется только временными соотношениями и опорным напряжением

Е. Данное обстоятельство позволяет существенно повысить точность и, следовательно, расширить область возможного применения источника калиброванных напряжений.

Источник калиброванных напряжений по авт. св. Юе 758095, отличающийся тем, что, с целью повышения точности, в него введен второй коммутатор, первый блок интегрирования дополнительно снабжен инверсным входом, второй блок интегрирования дополнительно снабжен вторым входом управления, а блок управления— тремя дополнительными выходами, причем первый и второй входы второго коммутатора соединены с соответствующими входами первого коммутатора, выход второго коммутатора подключен к инверсному входу первого блока интегрирования, а три дополнительных выхода блока управления соответственно связаны с первым и вторым управляющими входами второго коммутатора и вторым входом управления второго блока интегрирования.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ж 758095, кл. G 05 F 1/56, 31.05.79.