Стабилизатор постоянного напряжения с защитой от перегрузок по току

Иллюстрации

Показать всеРеферат

Союз Советсккк

Социалксткческмк

Республик

ОП ИСАНИЕ

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИ4ЕТ ЕЛЬ СТВУ

„, 860029 (61) Дополнительное к авт. свид-ву— (22) Заявлено 09.01.79 (2! ) 2708875/24-07 с присоединением заявки ¹вЂ” (23) Приоритет— (51) М. К, G 05 F 1)58

Гоеударствеииый комитет па делам изобретеиий и открытий (53) УДК 621.316. . 722. 1 (088.8) Опубликовано 30.08.81. Бюллетень №32

Дата опубликования описания 31.08.81

С. И. Реморов и A. В. Геркин: (72) Авторы изобретения (71) Заявитель (54) СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

С ЗАЩИТОЛ ОТ ПЕРЕГРУЗОК ПО ТОКУ

Изобретение относится к электротехнике и предназначено для надежного обеспечения электропитанием устройств связи, вычислительной техники и автоматики.

Известен стабилизатор постоянного напряжения, содержащий последовательный регулирующий транзистор, блок управления и каскад защиты, состоящий из резистивного датчика тока, включенного в силовую цепь передачи электроэнергии на входе стабилизатора, входного транзистора каскада защиты, эмиттер которого соединен с одним из выводов резистивного датчика тока, а база через ограничивающее сопротивление-с другим выводом резистивного датчика тока (1).

Однако в данном стабилизаторе входная цепь каскада защиты обладает значительной температурной нестабильностью порога срабатывания.

Наиболее близким к изобретению является стабилизатор постоянного напряжения с защитой от перегрузок по току, содержащий последовательный регулирующий транзистор, блок управления, подключенный к управляющему входу регулирующего транзистора, и каскад защиты, в котором для компенсации температурного дрейфа входной транзистор включен переходом эмиттербаза в диагональ моста, питающегося от параметрического стабилизатора на стабилитроне и балластном резисторе, при этом

5 общая точка одной пары плеч, образованной резистивным делителем, подключена к эмиттеру входного транзистора, а общая точка другой пары .плеч, образованной резистивным датчиком тока, диодом и резистором, через ограничивающий резистор подключена

1О к базе упомянутого входного транзистора каскада зашиты (2).

Недостатком известного стабилизатора является наличие в каскаде зашиты параметрического стабилизатора на стабилитро15 не, которое приводит к значительным потерям мощности в каскаде защиты, что особенно характерно при больших колебаниях напряжения на входе стабилизатора или при высоких напряжениях стабилизации.

Цель изобретения — снижение потерь в каскаде зашиты, повышение КПД стабилизатора и обеспечение универсальности каскада защиты независимо от величины входного напряжения.

860029

5 0 !

5 го

Формула изобретения

Зо

Поставленная цель достигается тем, что в стабилизатор постоянного напряжения с защитой от перегрузок по току, содержащий последовательный регулирующий транзистор, блок управления, подключенный к управляющему входу регулирующего транзистора, и каскад защиты, входной транзистор которого переходом эмиттер-база включен в диагональ моста, верхние плечи которого образованы резистором и резистивным датчиком тока нагрузки, включенным в коллекторную цепь регулирующего транзистора, и последовательно соединенными резистором и диодом, введены два транзистора, образующие нижние плечи моста, причем коллектор одного из транзисторов соединен с эмиттером, а коллектор другого — с базой входного транзистора, эмиттеры через токозадающие резисторы — с общей шиной стабилизатора, базы — с одним из выходных выводов стабилизатора.

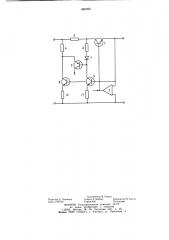

На чертеже представлена принципиальная электрическая схема стабилизатора постоянного напряжения с защитой от перегрузок по току.

Стабилизатор содержит последовательный регулирующий транзистор 1, блок 2 управления, подключенный к управляющему входу регулирующего транзистора 1, и каскад защиты, входной транзистор 3 которого переходом эмиттер-база включен в диагональ моста, верхние плечи которого образованы резистором 4 и резистивным датчиком 5 нагрузки тока, резистором 6 и термокомпенсирующим диодом 7, а нижние плечи — источниками стабильного тока на транзисторах 8 и 9, коллектор транзистора 8 соединен с эмиттером входного транзистора 3, коллектор транзистора 9 — с базой транзистора 3, эмиттеры через токозадающие резисторы 10 и 11 — с общей шиной стабилизатора, базы — с одним из выходных выводов стабилизатора.

Стабилизатор работает следующим образом.

При установившемся режиме на выходе стабилизатора имеется неизменное напряжение, которое, питая базовые цепи транзисторов 8 и 9, обеспечивает протекание в их коллекторных цепях неизменных значений токов, величины которых задаются резисторами 10 и 11. Таки(м образом, на резисторе 4 образуется опорное запирающее смещение для входного транзистора 3 каскада защиты, а на последовательно включенных резисторе 6 и диоде 7 — отпирающее термокомпенсирующее напряжение. При этом величины токов выбираются такими, чтобы при номинальном токе нагрузки транзистор 3 был заперт, т. е. 1/, = U4— — Ug — Ug — Up = R т1по/ /с(., где 4 . =

Д

= Unppll g — коэффициент допустимой токовой перегрузки; Inop — допустимое пороговое значение тока перегрузки. Для обеспечения термокомпенсации порога срабатывания ток через диод 7 выбирается таким образом, чтобы его температурный коэффициент напряжения был равен или близок температурному коэффициенту перехода эмиттер-база входного транзистора 3 каскада защиты.

Наличие стабильных источников тока делает независимой входную цепь каскада защиты от величины напряжения стабилизации, т. е. позволяет создать универсальную унифицированную схему каскада защиты.

Потери во входной цепи каскада защиты с источниками стабильного тока в широком диапазоне питающих напряжений значительно меньше, чем потери в схеме с параметрическим стабилизатором на резисторе и стабилитроне.

Стабилизатор постоянного напряжения с защитой от перегрузок по току, содержащий последовательный регулирующий транзистор, блок управления, подключенный к управляющему входу регулирующего транзистора, и каскад защиты, входной транзистор которого переходом эмиттер-база включен в диагональ моста, верхние плечи которого образованы резистором и резистивным датчиком тока нагрузки, включенным в коллекторную цепь регулирующего транзистора, и последовательно соединенными резистором и диодом, отличающийся тем, что, с целью снижения потерь в каскаде защиты, повышения КПД стабилизатора и обеспечения универсальности каскада защиты независимо от величины входного напряжения, в него введены два транзистора образующие нижние плечи моста, причем коллектор одного из транзисторов соединен с эмиттером, а коллектор другого — с базой входного транзистора, эмиттеры через токозадающие резисторы — с общей шиной стабилизатора, базы — с одним из выходных выводов стабилизатора.

Источники информации, принятые во внимание при экспертизе

1. Авто р с кое с в идетел ь ство С СС Р № 493775, кл. G 05 F 1/58, 1973.

2. Авторское свидетельство СССР № 535562, кл. G 05 F 1/58, 1972.

860029

Составитель В. Панов

Редактор А. Лежнина Техред А. Бойкас Корректор М. Коста

Заказ 7547/32 Тираж 940 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4