Устройство для воспроизведения квадратичной зависимости

Иллюстрации

Показать всеРеферат

Союз Соеетскнх

Социалистических

Республик

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 1 86ОО6О (61) Дополнительное к авт. свид-ву(22) Заявлено 230779 (21)2799915/18-24 с присоединением заявки Нов (23) Приоритет—

Опубликовано 300881. Бюллетень М 32

Дата опубликования описания 30.08.81 (51)М. Кл.

G 06 F 7/38

Госуаарствеииый комитет

СССР ио аелам изобретеиий и открытий (53) УДК 681 ° 325 (088. 8 ) (72) А изо (71) Заявитель

Ордена Трудового Красного Знамени институт кибернетики с вычислительным центром AH узбекской CCP (54) УСТРОИСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ КВАДРАТИЧНОИ

ЗАВИСИМОСТИ

Изобретение относится к вычислительной технике и может быть исполь— зовано в системах с аппаратурной реализацией функции, Известно устройство для воспроизведения квадратичнои зависимости (1)

Однако оно отличается сложностью и невысоким быстродействием.

Наиболее близким к предлагаемому является устройство для воспроизведения квадратичной зависимости, содержаыее задающий генератор, счетчик, сумматор, старт-стопную систему, элементы i И, HE (2 1.

Недостатком данного устройства является то, что формирование кода на выходе счетчика-сумматора реаЛизуется в несколько тактов с помощью старт-стопной схемы. Кроме того, присутствует операция сдвига на один 20 разряд, что оказывает влияние на быстродействие схемы. Наличие стартстопной схемы и громоздкость выходного счетчика-сумматора также усложняют устройство.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в устройство для воспроиэведения квадратичной зависимости, со- 30 держащее задающий генератор, счетчик, сумматор, вв дены буферный регистр, элемент задержки, причем выход задающего генератора соединен со входом счетчика, прямые разрядные выходы которого, кроме младшего разряда, подключены;: соответствующим входам первого слагаемого сумматора, прямой и инверсный выходы младшего разряда счетчика через элемент ИЛИ подключены ко входу первого слагаемого младшего разряда сумматора, разрядные выходы которого подключены к соответствующим входам буферного регистра, синхронизирующий вход которого соединен через элемент задержки с выходом задающего генератора, разрядные выходы буферного регистра подключены к соответствующим входам второго слагаемого сумматора.

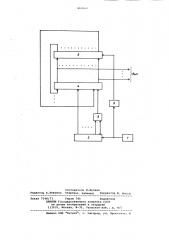

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит задающий генератор 1, выход которого соединен со входом счетчика 2. Прямой и инверсный выход младшего разряда счетчика через элемент ИЛИ 3 подключены ко входу первого слагаемого младшего разряда сумматора 4, а прямыа выходы

860060

Вход I КС4 Вход II КС4 Выход КС4

Счетчик

00000001

00000111

00010001

00011111

00101000

0001

00000001

00000011

00000011

00000101

00000101

00000111

00000111

00001001

00001001

00001011

00000001

00000111

00010001

00011111

0010

0011

0100

0101

0110

0111

1000

0010100 О 00110001

1001

00111100

00110001

1010 остальных разрядов счетчика до п-го разряда подключены ко входам первого слагаемого соответствующих разрядов

2п-разрядного. комбинационного сумматора 4. Выходы комбинационного сумматора 4 подключены ко входам 2п-разрядного буферного регистра 5, выходы которого подключены ко входам второго слагаемого соответствующих разрядов комбинационного сумматора 4.

Синхронизация записи в буферный регистр 5 осуществляется от элемента 6 задержки, вход которого подключен к выходу задающего генератора.

Устройство работает следующим образом.

Импульсы задающего генератора 1 поступают на вход счетчика 2, который формирует в зависимости от количества поступивших импульсов двоичный код аргумента воспроизводимой квадратичной функции. Каждое состо якие счетчика поступает в виде перного слагаемого на входы комбинационного сумматора 4, Благодаря наличию элемента ИЛИ 3, любое состояние младшего разряда счетчика 2 передается в младший разряд комбинационного сумматора 4, поэтому ко всем четным числам на выходе счетчика 2 добавляется "1". В каждом такте воспроиз— ведения код с выхода счетчика 2 складывается на комбинационном сумматоре 4 с кодом на выходе буферного регистра 5. Полученная сумма в виде кода вновь поступает для промежуточного хранения на вход буферного регистра 5 и одновременно на выходные клеммы устроиства.

Для временного согласования передачи кода с выхода 2п-разрядного комбинационного сумматора 4 на вход

2п-разрядного буферного регистра 5 используется элемент 6 задержки, параметры которого выбираются в зависимости от задержки на переходные процессы комбинационного сумматора 4.

В таблице приведены значения двоичных кодов состояний узлов схемы. В первой графе дано количество импульсов с задающего генератора, во второй — состояние выходов счетчика 2 в каждом такте воспроизведения, в третьей — коды на входах !

5 разрядов первого слагаемого комбинационного сумматора 4, в четвертой — коды на входах разрядов второго слагаемого комбинационного сумматора 4 и в пятой графе показаны коды на выходе комбинационного суммато20 ра 4, т.е. на выходе всего устройства.

Таким образом, время воспроизведения,т.е. формирования одного эначения квадратичной функции, опреде2.э ляется только временем срабатывания элементов счетчика 2, элемента ИЛИ 3 и комбинационного сумматора 4, поэтому предлагаемое устройство может работать с очень высо3Q кой тактовой частотой. Упрощение схемы осуществляется за счет уменьшения количества тактов работы, применения комбинационного сумматора и исключения тактирующих схем. Уст35 ройство может использоваться в системах ввода-вывода графической информации на экране ЭЛТ и системах нелинейной обработки сигналов.

860060

Продолжение таблицы

Счетчик

Вход I КС4 Вход II КС4 Выход КС4

00111100 01000111

01000111 01010100

1011

1100

01100001

01110000

01100001

1101

1110

01110000 01111111

Вход ИКС4

Выход КС4

Устройство для воспроизведения квадратичной зависимости, содержащее задающий генератор, счетчик, сумматор, о т л и ч а ю щ е е с я 30 тем, что, с целью повышения быстродействия, в него введены буферный регистр, элемент задержки, причем выход задающего генератора соединен со входом счетчика, прямые разряд-35 ные выходы которого, кроме младшего разряда, подключены к соответствующим входам первого слагаемого сумматора, прямой и инверсный выходы младшего разряда счетчика через элемент ИЛИ 4О подключены ко входу первого слага00001011

00001101.

00001101

00001111

00001111

П р и м е ч а н и е. Счетчик 2

Вход IKC4

Формула изобретения состояние счетчика; вход первого слагаемого комбинационного сумматора 4; вход второго слагаемого комбинационного сумматора 4; выход комбинационного сумма-,ора ° емого младшего разряда сумматора, разрядные. выходы которого подключены к соответствующим входам буферного регистра, синхронизирующий вход которого соединен через элемент задержки с выходам задающего генератОра, разрядные выходы буферного регистра подключены к соответству -щим входам второго слагаемого сумматора.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 432492, кл. G 06 F 7/38, 1972.

2. Авторское свидетельство СССР р 419889, кл. 6 06 Г 7/38, 1972 (прототип )..

Составитель М. Мусаев

Редактор A.Лежнина Техред А, Бабинец Корректор М. Коста

Заказ 7548/73 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытия

113035, Москва, Ж-35, Раушская наб., д. 4/5

Ф филиал ППП "Патент", г. Ужгород, ул. Проектная, 4