Арифметическое устройство

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистически я

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ С ЕТЕЛЬСТВУ

<в860065 (61) Дополнительное к авт. свид-ву— (22) Заявлено 301179 (21) 2845914/18-24 с присоединением заявки Ио (23) Приоритет—

Опубликовано 300881.бюллетень Но 32

Дата опубликования описания 300881

{53)М. Кл.

G 06 F 7/52

Государственный комитет

СССР но делам изобретений н открытиЯ

{53) УДК б21. 325 (088. 8) Ю. М. Ачк асов, A. П. Рубанов, С.С. Крыкин, и Л.И.Ухан в:";в;,:., в

:1i с

i Qtjir..с специальное конструкторско>-техт1тъяЖ лческое бюро геофизической техники---(72) Авторы изобретения ев (71) Заявитель (54 ) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано при создании цифровых вычислительных устройств.

Известно устройство для умножения и извлечения квадратного корня, содержащее регистры операндов и результата, схему анализа кодов, сумматоры, генератор тактов (1 ).

t0

Наиболее близким к предлагаемому является арифметическое устройство, содержащее регистры множимого, множителя, группу элементов И, ИЛИ,И-НЕ, и групп сумматоров, группы элементов

2И-ИЛИ (2 ). 15

Недостатком известных устройств является невысокое быстродействие при извлечении квадратного корня. .Цель изобретения — повышение быстродействия устройства при выполнении 2© операции вычисления квадратного корня.

Поставленная цель достигается тем, что в арифметическом устройстве, содержащем регистры множимого и множителя, группу элементов И, группу эле- 25 ментов ИЛИ, элементы И, ИЛИ, И-НЕ, и групп сумматоров, причем выходы сумматоров и-ой (где n — разрядность результата) группы соединены со входами регистра произведения, инверс- ЗО ные выходы разрядов которого (со второго по л-ый} соединены с первая входами соответствукщих элементов

2И-ИЛИ первой группы, вторые входы которых соединены с выходами регистра множимого, третьи входы — с входом разрешения записи произведения, а выходы подключены к первым входам сумматоров и-ой группы, вторые входы которых соединены с выходами сумматоров (n-1)-ой группы и разрядными входами регистра сумная, вторую группу элементов 2И-ИЛИ, выход 1-rо (где

i 1, 2..., n) разряда регистра множителя соединен с .первым входом i-го элемента И группы, выход которого подключен ко входу (21 1)-го разряда регистра множимого, выход i-ro элемента ИЛИ группы подключен к первому входу (21- 1}-го элемента 2И-ИЛИ второй группы, а первый вход i-го элемента ИЛИ группы соединен с выходом

1-го разряда регистра множителя, первый вход 21-го элежнта 2И-ИЛИ второй группы соединен с пряьым выходом (21+1)-го разряда регистра суммы,вторые входы элементов 2И-ИЛИ второй группы подсоединены к выходам сумматоров (n-2}-ой группы управляющие входы элементов 2И-ИЛЙ второй группы

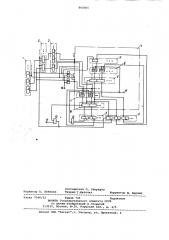

860065 поцключены к входу разрешения записи произведения, а выходы — ко вторым входам сумматоров (и-1)-ой группы, инверсный выход переноса и-ой группы сумматоров соединен с первым входом первого элемента И, второй вход которого соединен со входом разрешения записи в регистр, а выход подключен к управляющим входам элементов И групустройство содержит регистр 1 множителя, группу элементов И 2, регистр

3 множимого, матрицу 4 умножения на сумматорах, регистр 5 произведения, регистр 6 суммы, первую группу эле40 ментов И-ИЛИ 7, вторую группу элементов И-ИЛИ 8 (и-l)-ую строку сумматоров 9 матрицы, последнюю строку сумматоров 10 матрицы, группу элементов ИЛИ 11, элемент И-НЕ 12, первый элемент И 13, второй элемент И 14, элемент ИЛИ 15, первую шину 16 управления, вторую шину 17 управления.

Элементы 7-11 объединены в матрицу 4 умножения, Устройство работает следующим образом.

При умножении и квадратировании в регистры 1 и 3 заносятся сомножители, на шины 16 и 17 управления подается "0", результат произведения с выхода матрицы 4 записывается в регистр 5. Вычисление квадратного корня выполняется методом обратного поиска эа и тактов (где n - разрядность результата), т.е. производится последовательный подбор цифр результата, квадрат которого сравнивается с подкоренным выражением. Вычисление квадрата результата в i-ом приближении (шаге) выполняется с использо. ЬО пы и входам синхронизации регистра суммы, инверсный выход первого разряда которого соединен с первым входом элемента И-НЕ, второй вход которого подключен к прямому выходу первого разряда регистра произведения, а выход " к первому входу первого элемента И-ИЛИ первой группы, второй и третий входы которого подключены соответственно к выходу первого разряда регистра множимого и входу разрешения записи произведения, выход первого разряда регистра множителя 20 соединен с первым вхоцом второго эле мента И, выход которого соединен с четвертым входом элемента 2И-ИЛИ первой группы, а выход второго разряда регистра множителя соединен с д первым входом элемента ИЛИ, выход которого соединен с соответствуюицлм входом матрицы умножения, вторые входы второго элемента И и элемента

ИЛИ соединены с входом разрешения записи произведения, второй вход

i-ro элемента ИЛИ группы соединей с прямым выходом 2i-го разряда регистра суммы.

На чертеже изображена функциональная схема предлагаемого устройства. ванием значения результата а „. < (i-1)ro шага и приращения Ь., задаваемого в i-ом шаге.

Ы а =(а.+ Ь ) = а,;.,+2а,, Ь„ - b„

В исходном состоянии регистры 1, 3 и 6 очищены, на шину 16 подан разрешающий сигнал, в регистре 5 записано подкоренное выражение. В первом такте в регистре 1 производится первый сдвиг и в старший разряд заносится

"1", которая является пробным приращением (b ) для первого шага вычислений. Эа счет того, что выходы регистра 1 подключены через группу элементов ИЛИ 11 и группу элементов

И-ИЛИ 8 к входам ряда сумматоров 9 со сдвигом (i ûé разряд регистра 1 к (2i-1)-му разряду ряда сумматоров

9), то на вторые входы ряда.сумматоров 9 подается число равное b„. Через

Я эти же группы элементов на вторые входы ряда сумматоров 9 с регистра 6, в котором хранится квадрат результата (i-1)-ro шага, поступает число а „- „а о = О. На первые входы ряда

Z сумматоров 9 через открытые ключи, управляемые сигналом шины 16 через элемент ИЛИ 15, со входов матрицы поступает результат произведения

2a„„b„ 2aО Ь О, который формируется на регистре 3. На ряде сумматоров 10 производится сравнение квадХ и рата результата первого шага а„а +

+ 2a < Ь + Ь = b„c подкоренным выР. и ражейием А, хранящимся в регистре 5.

В конце первого такта при наличии переноса с„<- >

i 1) разряд регистра 3 переписывается "1" с первого разряда регистра 1.

Если сд,="0" (при à „> А), то содержимое регистров 3 и 6 не изменится.

Второй и последующие такты начинаются с импульса, по которому содержимое регистров 1 и 3 сдвигается на разряд вправо. Описанный процесс повторяется с учетом того, что при вычислении квадрата результата g i-ом приближении (шаге) на ряд сумматоров

9 кроме слагаемого Ь. поступают слаk

Я 1 гаемые а„„и 2 а„,Ь;, которые равны или больше нуля в зависимости от результата а„. < предыдущего шага. Ввиду того, что у слагаемых а„и b в

i-ом шаге не перекрывается диапазон их возможных численных значений, то они поступают на одни и те же входы ряда сумматоров 9 через группу элементов ИЛИ 11. Слагаемое 2а„ Ь„ формируется на регистре 3 после установки "1" (или "0") в (2i-1)-ом разряде в конце (i- 1)-ro такта и последующего сдвига содержимого регистра 3 в начале 1-го такта.

860065

Модуль разности старшего разряда регистра 5 и старшего разряда регистра 6 формируется на элементе И-НЕ 12, . что не требует установки дополнительного разряда сумматора в ряде сумматоров 9 матрицы 4.

Таким образом, после и тактов и-разрядный результат вычисления квад! ратного корня, сдвйнутый íà и разрядов вправо, находится в регистре 3.

Как видно из описания, сущность улучшения по сравнению с известным устройством заключается в повышении быстродействия устройства при выполнении операции вычисления квадратного корня за счет уменьшения .периода каждого из п вычислительных тактов. Время выполнения операции вычисления квадратного корня известного устройства для и разрядов результата определяется из соотношения

20 е И п (2п Г„,+ и Г ) ап (2 п т,„+2п С„,)

„а. где 0и — задержка распространения переноса на один разряд сумматор໠à — задержка распространения сигнала суммы на один разряд сумматора.

Время выполнения операции вычисления квадратного корня предлагаемого З0 устройства для и разрядов результата и

n(2n S„) = 2п С„. »

Ускорение, получаемое при вычи слении квадратного корня на нем, k =t„(6p2. 35

Таким образом, расчеты показывают, что быстродействие предлагаемого устройства по сравнению с известным вдвое больше.

Формула изобретения

Арифметическое устройст во, содержащее регистры множимого и множителя, группу элементов И, группу элементов

ИЛИ, элементы И, ИЛИ, И-НЕ, и групп сумматоров, причем выходы сумматоров и-ой (где и — разрядность результата) группы соединены со входами регистра произведения, инверсные выходы разрядов которого (co второго по и-ый) 0 соединены с первыми входами соответствующих элементов ?H-ИЛИ первой группы, вторые входы которых соединены с выходами регистра множимого, третьи входы - с входом: разрешения И записи произведения, а выходы подключены к первым входам сумматоров,п-ой группы, вторые входы которых соединены с выходами сумматоров (п-1)-ой группы и разрядными входами регистра суммы, вторую группу элементов

2И-ИЛИ,отличающееcй тем, что, с целью повьыения быстродействия, в устройстве выход i -го (где

i =1,2...,n) разряда регистра множителя соединен с первым входом i-го элемента И группы, выход которого подключен ко входу (2 i -1)-го разряда регистра множимого, выход i ão элемента ИЛИ группы подключен к первому входу (2i-1)-го элемента 2И-ИЛИ второй группы, а первый вход i ãî элемента

ИЛИ группы соединен с выходом i-ro

I разряда регистра множителя, первый вход 21-го элемента 2И-ИЛИ второй группы соединен с прямым выходом (2i+1)-ro разряда регистра суммы, вторые входы элементов 2И-ИЛИ второй группы подсоединены к выходам сумматоров (n-2)-ой группы, управляющие входы элементов 2И-ИЛИ второй группы подключены к входу разрешения записи произведения, а выходы - ко вторым входам сумматоров (и-1)-ой. группы, инверсный выход переноса и-ой группы сумматоров соединен с первым входом первого элемента И, второй вход которого соединен со входом разрешения записи в регистр, а выход подключен к управлякицим входам элементов И группы и входам синхронизации регистра сумы, инверсный выход первого разряда которого соединен с первым входом элемента И-НЕ, второй вход которого подключен к прямому выходу первого разряда регистра произведения„ а выход — к первому входу первого элемен та И-ИЛИ первой группы, второй и третий входы которого подключены соответственно к выходу первого разряда регистра множимого и входу разрешения записи произведения, выход первого разряда регистра множителя соединен с первым входом второго элемента

И, выход которого соединен с четвертым входом элемента 2И-ИЛИ первой группы, а выход второго разряда регистра множителя соединен с первым входом элемента ИЛИ, выход которого соединен с соответствующим входом матрицы умножения, вторые входы второго элемента И и элемента ИЛИ соединены с входом разрешения записи произведения, второй вход i-го элемента

ИЛИ группы соединен с прямым выходом

2i-го разряда регистра суммы.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 657434, кл G 06 F 7/38, 1977.

2. Авторсков свидетельство СССР

9 542993, кл G 06 F 7/38, 1977.

860065

Составитель О. Свиридов

Техред Т.Маточка Корректор N, Шароши

Редактор A. Лежнина

Филиал ППП "Патент",г. Ужгород, ул.. Проектная, 4

Заказ 7549/32 Тираж 745 Подпи си се

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5