Устройство асинхронного сопряжения цифровых сигналов

Иллюстрации

Показать всеРеферат

Союз Соаетсккн

Социалистических

Республик

ОПИСЛНИЕ

ИЗОБРЕТЕН ИЯ

1 186О326

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву (22) Заявлено 28.03.79 (21) 2748039/18-09 с присоединением заявки М (23) Приоритет (51)М. Кл.

Н 04 J 3/00

Н 04 J 3/06

Гнеударетевнный некнтет

СССР

an делан нзабретеиий н аткритнй

Опубликовано 30.08.81. Бюллетень ЭЙ 32

Дата опубликования описания 30,08.81 (5З) УДК б21 .395.5 (088.8) (72) Автори изобретения

А. Н. Глухов, О. С. Когновицкий н 10. В.: JIapm1

1 (7l ) Заявитель

Ленийградский электротехническ нм. проф. М. А. Бонч-Бр (54) УСТРОЙСТВО АСИНХРОННОГО СОПРЯЖЕНИЯ ЦИФРОВЫХ

СИГНАЛОВ

Изобретение относится к электросвязи н может быть использовано для асинхронного ввода — вывода сштхронной двоичной ннфор. мации в цифровые такты с импульсно-кодовой модуляцией и дельта-модуляцией.

Известно устройство асштхронного сопряжения стптхронных двоичных цифровых сигналов, содержащее на передающей стороне фазовый компаратор, первым своим выходом соединенный с кодером фазы, а вторым выходом— с управляющим входом управляемого распределителя, датчик фазирующей комбинации, выход которого подключен к одному из входов блока памяти, а выходы кодера фазы и управляемого распределителя подсоединены соответственно к остальным входам блока па15 мяти, а на приемной стороне содержит коммутатор, блок фазирования по циклам, вход которого подключен к фазирующему выходу коммутатора, а управляющий выход — к сдвигающему входу коммутатора, декодер фа- О зы, информационные входы которого соединены с выходами служебных сигналов коммутатора, а управляющий вход — с выходом

2 опорных сигналов блока фазирования по циклам, управляемый распределитель, управляющий вход которого соедтп1ен с выходом декодера фазы, а выходы — со входами считывания блока памяти, ко входам записи информации которого подключены информационные выходы коммутатора 11) .

Недостатком известного устройства является полное отсутствие помехозащищенности передаваемой по каналу связи информации и, 1 как следствие, недостаточно высокая достоверность ас1птхротптого сопряжения синхронных цифровых сигналов.

Цель изобретения — повышение помехозащн, щеш1ости передаваемой информации. ,11ля достттжения цели в устройство асинхронного сопряжения цифровых сигналов, содержащее на передающей стороне блок формирования опорных импульсов и последовательно соединенные управляемый распределитель и блок памяти, причем первые управляющие входы управляемого распределителя и блока памятФ . соединены с первым выходом формирователя опорных импульсов, а па приемной стороне

8603 2б

15

55 последовательно соединенные блок формирования тактовых импульсов, управляемый распределитель и блок памяти, введены на передающей стороне кодер стаффинговых интервалов и последовательно соединенные счетчик, дешифратор и формирователь псевдослучайных сигналов, причем второй управляющий вход управляемого распределителя соединен с первым входом блока формирования опорйых импульсов, информационный выход управляемого распределителя подключен к первому входу кодера стаффинговых интервалов, второй вход которого соединен со вторым выходом форми* рователя опорных импульсов, первый и второй выходы кодера стаффинговых интервалов подключены соответственно ко второму и третьему управляющим входам блока памяти, информационные выходы которого подключены к информационным входам счетчика, при зтом вторые входы формирователя опорных импульсов и дешифратора соединены между собой, причем второй выход дешифратора подключен к управляющему входу счетчика, а иа приемной стороне введены декодер стаффинговых интервалов, регистр сдвига, блок сравнения, формирователь псевдослучайных сигналов, блок управления, счет шк и последовательно соединенные блок запуска и блок задержки, причем первый и второй входы регистра сдвига соединень1 соответственно с первым и вторым входами блока запуска, выход которого подключен к первым управляющим входам блока сравнения и формирователя псевдослучайных сигналов, выходы которого подключены к первым информационным входам блока сравнения, вторые информационные входы которого соединены с выходами регистра сдвига, первый выход блока сравнения подключен ко входу блока управления, выход которого соединен со вторым управляющим входом формирователя псевдослучайных сигналов и с первым входом счетчика, выходы которого подключены к информационным входам блока памяти, первый и второй выходы которого подключены соответственно к первому и второму входам декодера стаффинтовых интервалов, первый и второй выходы которого соединены соответственно с управляющими входами блока памяти и блока формирования тактовых импульсов, при зтом выход блока задержки подключен ко вторым входам управляемого распределителя и счетчика, третий управляющий вход формирователя псевдослучайных сигналов соединен с третьим входом счетчика, четвертый вход которого соединен со вторым выходом блока сравнения.

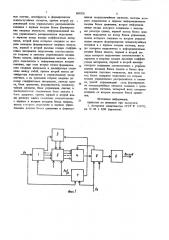

На чертежах приведена структурная злектрическая схема устройства.

На фиг. 1 показано устройство, передающая сторона; на фит. 2 — то же, приемная сторона..4

Устройство содержит на передающей стороне управляемый распределитель 1, блок 2 памяти, кодер 3 стаффинговых интервалов, счетчик 4, дешифратор 5, формирователь 6 псевдослучайных сигналов, блок 7 формирования опорных импульсов, на приемной стороне регистр 8 сдвига, блок 9 сравнения, регистр 10 сдвига, блок 11 управления, счетчик 12, декодер 13 стаффинговых интервалов, блок 14 памяти, управляемый распределитель IS, блок 1б формирования тактовых импульсов, блок 17 запуска и блок 18 задержки.

Устройство работает следующим образом.

Для сопряжения синхронных двоичных сигналов, следующих с тактовой частотой, и сигналов цифрового канала связи, следующих с частотой, несущей последовательность, на передающей стороне устройства в блоке 7 формируются опорные импульсы с частотой

f>JN. Синхронные двоичные сигналы, соответствующие тактовым импульсам, поступают на блок 2 памяти, Эти сигналы, появляющиеся в интервале от одного опорного импульса до другого, образуют информационный цикл, который подлежит передаче по цифровому каналу. Опорными импульсами частотой j>(gaaпускается управляемый распределитель 1, представляющий регистр сдвига. Разряды регистра, за исключением первого, обнуляются опорными импульсами. В первый разряд регистра записывается "!", которая продвигается по разрядам импульсами тактовой частоты о до тех пор, пока не появляется следующий опорный импульс.

Зались синхронных двоичных сигналов в блок 2 памяти осуществляется на частоте У тактовыми импульсами, поступающими с выходов управляемого распределителя 1. Сигналы информационного цикла анализируются затем в кодере 3 стаффинговых интервалов.

По сигналам из кодера 3 информационный цикл переменной длины в блоке 2 памяти трансформируется в цикл постоянной длины, содержащий (n + 2) единичных двоичных интервала. Кодер 3 стаффинговых интервалов управляется сигналами из блока 7.

Считывание информации цикла постоянной длины из ячеек блока 2 памяти производится на частоте опорных импульсов f tN, Считанная информация в параллельном коде поступает на соответствующие входы счетчика 4 и затем на вход дешифратора S. Если нолученная комбинация отличается от "нулевой", то дешифратор выдает сигнал, по которому быстрые тактовые импульсы (БТИ) поступают на счетный вход счетчика 4. Эти импульсы подаются до тех пор, пока счетчик не устанавливается в нулевое положение. Одновременно с

860326

30 подачей БТИ на счетчик 4 эти импульсы поступают на вход формирователя 6 с логической обратной связью. При этом формируемая псевдослучайная последовательность сигналов изменяет начальную фазу на число элементарных шагов, равное десятичному числу, соответствующему двоичной кодируемой комбинации, С установкой счетчика 4 в нулевое положение дешифратор 5 прекращает подачу БТИ в счетчик 4 и в формирователь б. С этого момента в формирователь б через дешифратор 5 начинают поступать импульсы с частотой 1 несущей последовательности. С их помощью производится считывание информации из формирователя 6 в канал связи. Блок 7 служит для осуществления запуска и работы устройства по циклам.

На приемной стороне после осуществления запуска (начального фазирования, при котором блок 17 запуска, получая из канала наго чальную фазнрующую комбинацию, выдает первый опорный (импульс) происходит запись информации, поступающей из канала на частоте 11 в регистр 8 сдвига. После заполнения регистра, имеющего М выходов, соединен25 ных блоком 9 сравнения, в последнем происходит логическое сложение по модулю два поступившей из канала N элементной комбинации с такими же N элементами, формируемыми в регистре 10 сдвига со схемой логической обратной связи. Если эти комбинации (представляющие собой фазы псевдослучайной последовательности) отличаются более, чем в одном элементе, то на выходе схемы сравнения появляется сигнал, который воздействует на блок управления 11, с выхода последнего на вход счетчика 12 поступают БТИ. Одновременно БТИ поступают на вход регистра 10, причем с приходом очередного БТИ фаза формируемой в этом регистре псевдослучайной последовательности изменяется на один шаг и 4о сравнивается с фазой поступившей из канала комбинации. Процесс происходит таким образом до тех пор пока фазы не сравняются илн будут отличаться лишь одним элементом. Тогда с выхода блока 9 сравнения поступит сиг- 4s нал на блок 11 управления, который прекратит подачу БТИ в счетчик 12, на выходах которого двоичная кодовая комбинация соответствует числу поступивших БТИ.

Формирование псевдослучайной последовательности в регистре 10 осуществляется эа время одного единичного интервала, т.е. за. время длительности каждого опорного импульса поступающего в блок 11 управления, причем за это время фаза псевдослучайной последовательности принимает все возможные значения иэ

2 и возвращается в исходное "нулевое" состояние.

Двоичная кодовая комбйнация, соответствующая числу БТИ поступивших на вход счетчика 12 параллельным кодом считывается за. держанным опорным импульсом, прн этом два последних элемента поступают в декодер

13 стаффинтовых интервалов, а остальные— в блок 14 памяти. В декодере 13 двухэлементная комбинация преобразуется в сигналы управления схемой ФАПЧ блока 16 формирования тактовых импульсов, а также в сигнал информации, который поступает в блок 14 и соответствует действительному (и+1)-ому единичному интервалу.

Блок 14 памяти, находящийся на выходе приемной части устройства сопряжения, позволяет считывать информацию на тактовой частоте $<, вырабатываемой блоком 16 и корректируемой по сигналам декодера 13 в зависимости от числа единичных информационных интервалов в цикле (и — 1 или и+1), при помощи схемы ФАПЧ, входящей в состав блока 16.

Считывание информации цикла из блока 14 памяти производится при помощи управляемого распределителя 15, который представляет собой регистр сдвига с (n+1) выходом.

Этот регистр тактируется скорректированной

Ъ тактовой частогой с, а управляется задержанными опорными импульсами с частотой p(,N.

Двоичная информация, считанная из блока

14 памяти образует информационный цикл и в виде непрерывной последовательности поступает в абонентскую линию.

Блок 17 запуска, блок 18 задержки служат для запуска приемной части устройства и осуществления последующей работы по циклам.

Таким образом, введение ряда новых блоков позволяет повысить помехозащищенность устройства асинхронного сопряжения цифровых сигналов и тем самым увеличить достоверность передаваемой информации по цифровым каналам связи.

Формула изобретения

Устройство асинхронного сопряжения цифровых сигналов, содержащее на передающей стороне блок формирования опорных импульсов и последовательно соединенные управляемый распределитель и блок памяти, причем первые управляющие входы управляемого распределителя и блока памяти соединены с первым выходом формирователя опорных импульсов, а на приемной стороне последовательно соединенные блок формирования тактовых импульсов, управляемый распределитель и блок памяти, о т л н ч а ю щ е е с я тем, что с целью tloBhIIIIOIGBI помехозащищенности, вве дены на передающей стороне кодер стаффинговых интервалов и последовательно соединен7 8 ные счетчик, дешифратор и формирователь псевдослучайных сигналов, причем второй управляющий вход управляемого распределйтеля соединен с первым входом блока формирования опорных импульсов, информационный выход управляемого распределителя подключен к первому входу кодера стафф птговых интервалов, второй вход которого соединен со вторым выходом формирователя опорных импульсов, первый и второй выходы кодера стаффинговых интервалов подключены соответственно ко второму и третьему управляющим входам блока памяти, информационные выходы кото-, рого подключены к информационным входам счетчика, при этом вторые входы-формирователя опорных импульсов и дешифратора соединены между собой, причем второй выход дешифратора подключен к управляющему входу счетчика, а на приемной стороне введены декодер стаффинговых интервалов, реГистр сдвига, блок сравнения, формирователь псевдослучайных сигналов, блок управления, счетчик и последовательно соединенные блок запуска и блок задержки, причем первый и второй входы регистра сдвига соединены соответственно с первым и вторым входами блока запуска, выход которого подключен к первым управляющим входам блока сравнения и формиро60326 8 вателя псевдослучайных сигналов, выходы которого подключены к первым информационным входам блока сравнения, вторые информационные входы которого соединены с выходами регистра сдвига, первый выход блока сравнения подключен ко входу блока управления, выход которого соединен со вторым управляющим входом формирователя псевдослучайных сигналов и с первым входом счетчика, выходы которого подключены к информационным входам блока памяти, первый и второй выходы которого подключены соответственно к первому и второму входам декодера стаффинговых интервалов, первый и второй выходы которого соединены соответственно с управляющими входами блока памяти и блока формирования тактовых импульсов, при этом выход блока задержки подключен ко вторым входам управляемого распределителя и счетчи20. ка, третий управляющий . ьход формирователя псевдослучайных сигналов соединен с третьим входом счетчика, четвертый вход которого соединен со вторым выходом блока сравнеЕПТЯ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР N 510792, кл. Н 04 J 3/00 (прототип),