Устройство для формирования импульсных последовательностей с заданным законом изменения фазы

Иллюстрации

Показать всеРеферат

Союз Соаетсжнк

Сав иаактмчесвик

Ресеубюж

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Н АЮТОРСЖ©МУ ИИЛЬСТВУ

«ц862 1 34

{бЦ Дополнительное к.авт. саид-ву(51)М. КлЗ

Q 08 F 1/02

{22) Заявлено 251229 {23) 2870569/18-24 с присоединением заявки й9

Гесуяарствекяма кемктет

СССР яо дмаи изобретений к аткрытяй

{23) йриорнтетОпубликовано 070981.бюллетень Й9 ЗЗ (53) УДК 881 ЗЗ5 (088. 8) Дата опубликования описания 07.0931

Ь (54 ) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

С ЗАДАННЫМ ЗАКОНОМ ИЗМЕНЕНИЯ ФАЗЫ

Изобретение относится к вычислительной технике и может быть исполь. зовано в радиотехнике, технике связи и измерительной технике, где требуется формировать импульсные последовательности с заданным законом следо" вания импульсов.

Известно устройство p1) для формирования сигналов с изменением частоты по закону полинома, содержащее формирователь опорных последователь.ностей, селектор импульсов, делитель частоты, фильтр нижних частот, комму-таторы, счетчики, дешифраторы,триггеры, .схем сравнения, согласукщий делитель, Это устройство не позволяет формировать последовательности с заданным законом изменения фазы.

Иэ известных устройств наиболее близким по технической сущности к изобретению является устройство 52), содержащее последовательно соединенные блок установки параметров сиг-. налов, блок накопителей, блок деления, а также синхронизатор, регистр, генератор пилообразного напряжения, компаратор, первый и второй цифро.аналоговые преобразователи (цАП) и ,умножитель.

Недостатками устройства являются сложность, связанная с наличием ана= логовых блоков, невысокая точность формирования сигналов, являющаяся следствием неточного формирования пилообразного напряжения, и,ограниченный диапазон выходных частот изэа использования ЦАП, обладающего ограниченным быстродействием.

Целью изобретения является повышение тОчиости работы, расширение диапазона выходных частот и упрощение устройства.

Поставленная цель достигается тем, 1 что в устройство, содержащее блок памяти, информационные входы которого соединены соответственно с выходами ввсда параметров, а тактовые входы соединены соответственно с выходами

20 генератора синхросигнаЛов, выход блока памяти подключен к входу регистра, тактовый вход которого соединен с выходом генератора синхросигналов, 25 Введены элемент задержки мультиплексор и арифметический блок, входы которого соединены соответственно с выходами блока памяти. Входы мультиплексора подключены соответственно к выходам элемента задержки и к выходам

З0 арифметического блока. Выход мульти862134... )- ) )()) ) <<- ) (1)

Я-Ф . Ь.плексора является выходом устройства.

Вход элемента задержки соединен с,выходом регистра, тактовый вход.подключен к выходу генератора синхросигналов.

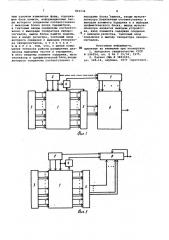

На фиг. 1 и .2 изображены варианты структурной схемы устройства на 5 фиг. 3 †. функциональная схема блока памяти; на фиг. 4 - графики, поясняющие принцип работы устройства При формировании прямоугольного сигнала с линейной частотной модуляцией. t0

Устройство содержит блок 1 памяти, генератор 2 синхросигналов,блок 3 ввода параметров, регистр 4, арифметический. блок 5, мультиплексор 6, элемент задержки 7 и делитель 8 с переменным коэффициентом деления.

Блок памяти содержит накопитель

9 кода частоты, накопитель 10 кода фазы и элемент ИЛИ 11.

В качестве арифметического блока может быть использован микропроцессор или делитель кодов.

Рассмотрим принцип работы устройства.

Пусть фаза Ч)(Ц идеального сигнала изменяется по закону

Ч(()=Ч) + (d tifh(t + улаф ) () о) ) Ж где Ч,),),)„, р, ...Чд — параметры модуля- З© ции сигнала;

Тс - длительность сигнала. Принцип работы устройства осно- ван на цифровом формировании кода фазы сигнала К Ч,, в фиксированныеЧ ) 1 Ф

1 тактовые моменты времени 1; -"1Т, где

=. 0,1,2..., которое реализуется с помощью последовательно соединенных накопителей и сумматоров. Выходной код последнего иэ них определяется следующим соотношением: 40

К .=МЧ, +К «K» 01 +...«K< 1", т=019... ):

Ч),1 Ч,0 „0 Р,О =0,1,2.... где КЧ,,а Ки о,КВo..- коды, соответствующие параметрам модуляции

Чо) ®о ba .Емкость последнего из накопителей, в котором. осуществляется накопление фазы ограничена некоторым значением.

) 2, которое соответствует Л рад.. «б

По. этой причине в моменты времени, соответствующие переполнению накопителя .фазы, на выходе его разряда переполнения появляется импульс, а его содержимое уменьшается до некоторого остаточного значения К Ч)„, ко11 торое в общем случае не равно нулю.

Отличие KЧ,; от нуля указывает на то, что импульс, переполнения формируется с некоторой временной погрешностью ;, являющейся следствием е0 дискретного накопления фазы. Уменьшить эту сшибку можно повышением тактовой частоты, но такое решение связано с увеличением потребляемой мощности я удорожанием устройства вслед- 6$ ствие применения более дорогих быстродействующих микросхем с высоким потреблением мощности.

Другой путь состоит в использовании накопителей с относительно невысокой тактовой частотой в сочетании с задержкой импульса переполнения на величину 1, определяемую. через зна-. чение к „,4 и параметры формируемого сигнала. В общем случае эту связь можно установить, воспользовавшись разложением функции Ч (+) в окрестности точки t;, соответствующей переполнению накопителя фазы, в ряд

Т.эйлор а

) и

Ч (1 Г ) Ч (+ )" Ч (t,.) «Ч) » )-4-+...

r) i Ì

" (- ) ))" Ь,ф, где Ч ) )М ) Ч и - первая, вторая, третья и т.д. производные функции

Y(t) в точке Ф; =3T

Раэ ность Ч (4 ) — Ч) (+„- ;), выраженная в кодах, есть: йи что иное, как

КЧ, „. Учитывая далее, что Ч) (tÄ),Ч "(Ц), Ч"Щ,... соответствует KopaMK „)Kg,„ подаваемым на входы г-го, (- ) -го, (г - 2)-ro, ... накопителей, получаем

К вЂ” +Ê

Ч))1™Щ4Ы P g) j i 3Г где 6„-= C (Т определяют относительную временную ошибку в появлении импуль- са переполнения. Поскольку в выраЖении, (2) коды Ку,.(., к („, известны, . величинад; сю-, жет быть вычислеяа. Это вычисление осуществляется в цифровом виде в арифметическом блоке 5. Полученный в результате вычислений код используется для коммутации с поьющью мультиплексора 6 отводов элемента задержки 7 с целью обеспечения задержки относительно импульса пе реполненияя на время Т-"С „., где „ =KT/Q -.. дискретиэированное значение Г;, где К=1,2,3.... Q (О количество отводов .элемента задерж- ки) .

Пользоваться точным выражением для вычисления 4„- не всегда обязательно. В случае, когда для любых значений выполняются условия

К „Ф K@(K,ypK, ., (3) и погреш- ность вычислений не превосходит ошибок квантования, являк)шихся следствием применения элемента задержки с конечным числом отводов Q, величину

862134

К можно рассчитывать по приблиа1 жейной формуле

/k®, (где Кд „- код чи.сла а „) . (4 )

Число разрядов L кода задержки Кд; связано с количеством отводов L .в делителе 8 следующим соотношением:

2 %

Входящий в устройство регистр 4 служит для задержки импульсов перепой нения. иа целое. число тактов(8=. Т,2Т, 3Т,...).Величина этой задержки определяется временем вычисления в блоке

5 и должна быть, по крайней мере, на один такт меньше минимального периода Формируемого сигнала. В том случае, когда время вычисления кода

К а меньше, чем Т/Q,, регистр 4 из устройства можно исключить, соединив выход разряда переполнения блока 1 непосредственно со входом элемента эа держки 7.

Выход мультиплексора б является . одновременно и выходом устройства..

При необходимости импульсные сигналы можно преобразовать в синусаидальные либо с помощью кольца фазовой автоподстройки частоты, либо посредством деления частоты вдвое и соответствующей фильтрации полученных после деления прямоугольных колебаний.

В качестве примера рассмотрим фор.мирование прямоугольного сигнала,с линейной частотной модуляцией (ЛЧ(с4) в предположении что Kyz= 0000001, К о -К,„„=Кс(= ООООООО..В этом случае блок 1 содержит последовательно соединенные .накопитель 9 кода частоты, накопитель 10 кода фа-зы и элемент ИЛи 11. C учетом того, что до начала ЛЧМ-сигнала все нако.пители обнулены и в каждом из них происходит: запаздывание на 1 такт, код фазы КЧ, сигнала меняется по с1 следующему алгоритму:

К„.= 0,5(1 -i), i.= О,!,2,3, Юс1

В случае ограниченной емкости накопителя 10 кода фазы (И=-128) закон изменения кода фазы К ; представлен на фиг. 4,а.

В моменты переполнения накопителя 10 кода фазы (i=17,24, 29, 33, 37, 40 н т.д. )на выходе разряда переполКения возникают импульсы, которые вместе с первым импульсом, поступающим от генератора 2 синхросигналов на элеМент ИЛИ 11, образуют последовательность, показанную на фиг. 4,б (здесь предполагается, что регистр 4 не вносит задержки).

Поскольку в данном примере для всех i, соответствующих моментам переполнения, условия (3) выполняются, вычисление К мажет вестись па при- ,1 ближенной формуле (4), что позволя ет использовать в качестве блока 5 делитель кодов. ВыходнЫе коды б ока

5 служат для выбора сигнала .с одного из отводов элемента задержки 7, При значений .управляющего кода

K ; = 00...0 на выход мультиплексора 6 проходит максимально задержан5,й сиги„, пер„ нения с последнего отвода элемента задержки 7, а при . Кg 4 = 11...1 - минимально задержанный сигнал переполнения с первого отвода элемента задержки 7. В результате та О кой задержки положение импульсов на выходе мультиплексора б оказывается более близклм к моМентам перехода через нуль идеального ЛЧИ сигнала (фиг. 4,в). Если на выходе мульти35 плексора б стоит- делитель частоты с коэффициентом деления, равным двум, то с последнего получают прямоуголь! ное ЛЧИ-колебание (фиг. 4, г).

Фаэовые ошибки Е; на выходе муль20 типлексора б становятся существенно меньше первоначальных ошибок, характерных для импульсов переполнения с выхода блока 1, вместо аналогового элемента задержки может ис25 пользоваться цифровой, выполненный в виде регистра сдвига. На тактовый вход регистра сдвига в этом случае подаются импульсы с частотой следования Q/Т.

ЗО Функции элемента задержки 7 к

Мультиплексора 6 могут быть совмещены в делителе 8 с переменным коэффициентом деления.

Тактовые импульсы с частотой

З Q/T проходят на вход делителя 8 лиШЬ при поступлении на него очередного .импульса с регистра 4. Коэффициент деления определяется кодом, поступающим от блока 5.

При коде 00...0 коэффициент деле40 ния максимален., при коде = 11... 1 коэффициент деления равен единице.

ЙМпульсы, прошедшие на выход делите.ля 8 поступают далее на вход установки нуля делителя.

45 ТВКН!4 o5pa3QMiËo прихода следующего импульса с выхода регистра 4 делитель снова оказывается откл!очен ным .

Устройство более просто по сравнению с известным устройством, поскольку не содержит аналоговых блоков, включая генератор пилообразного напряжения ЦАП и компаратор. Оно имеет более высокую точность работы которая определяется лишь числом отводов и точностью их расстановки в элементе задержки 7 или зависит только от тактовой частоты.

УстройСтво обладает более широким диапазоном выходных частот, поскольку в него не входит ЦАП, имеющий невысокое быстродействие..

Формула изобретения

Устройство для формирования им пульсных последовательностей с задан

862134 ным законом изменения фазы, содержащее блок памяти, информационные входы которого соединены соответственно с выходами блока ввода параметров, а тактовые входы соединены соответственно с выходами генератора синхросигналов, выход блока памяти подключен к входу регистра, тактовый вход которога соединен с выходом генератора синхросигналов, о т л и ч а юю щ е е с я, тем, что, с целью повышения точности работы расширения диапазона выходных частот и упрощения, в него введ ны элемент зацержки, муль .типлексор и арифметический блок, входы ,которого соединены соответственно с выходами блока памяти входы мультиплексора подключены "соответственно к выходам элемента задержки и к выходам: арифметического блока, выход мультиплексора является выходом устройства, вход элемента задержки соединен с выходом регистра, тактовый вход подключен к выходу генератора синхро сигналов.

Источники информации, принятые во внимание при экспертизе

1. авторское свидетельство СССР в 596954, .кл. 6 06 f 15/34, 1975.

2. Патент США В 3882403, кл. 328-14, опублик. 1975 (прототип).

862134. Epi

Х8 T

Составитель A. Жерейов

Редактор Л. Утехина Техред N. Голинка

Корректор О. Бил ак

Заказ 661 3/4 3 Тираж 745 : . Подписное

BHHHIIH Государственного комитета ссср по делам изобретений и открйтий .

113035, Москва, Ж-35, Рауюскай иаб., д 4/5

4 МФ Ь °

Филиал ППП "Патент", г. Ужгород, Ул, Проектная, 4