Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Сюе» Севетскмх

Социайистнчеавих

Ужеубав (п362141

В АМТ©УСЗЮМ31 ТЮЛИ:ФВУ (&1}Дополнительное кает,сеид-ау в 451080 (51 1 М. Кл.

6 06 F 9/22 (22} Заяалено 090130 (21 } 2871648/18-24 с присоединением заяекеййГбс)(д&Рстэ&йяыя яеият&т

СССР ао делан мзебретеякВ к открытк1 (23} ПриоритетOny6amesme 070981. бюллетень М ЗЗ (53) УДК 681. 325 (088 ° 8) Дата опубликования описания 070981 (T2} Автор изобретения

И. В. Шапиро (71} Эаяеитель (54) МИКРОПРОГРИЩНОЕ УСЙРОЙСТВО УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике и может быть исполь-. зовано в универсальных и специали зированных ЦВМ. По основному авт.св. 9 451080 известно микропрограммное устройство управления, содержащее два запоми» нающих блока, два регкстра адреса, два:коммутатора, две схемка& И к два триггера. Причем выход каждого коммутатора соединен с первым входом сосответствукщего регистра адреса.

Первый и второй входы каждого запоминающего блока соединены с выходамк соответствукщйх регистра адреса:и схеж И. Первые выходы первого и второго запоминающих блоков соедине. ны с вторыми входамй второго и пер ваго регистров адреса, вторые выходйпервого и второго запоминающих блоков соединены с входами второго и первого триггеров. Первые выходы каж» дога.триггера соединены. с первыми входаии соответствующих схем И. Вторые выходы первого к второго регист: .ров адреса соединены с первюею входаии второго и первого коммутаторов.

Вторые входы первой и второй схеме

И соединены с вторыми входами второ го и первого коммутаторов. Вторые.входы первого и второго триггеров соединены с третьими входами второго.. и первого комю» таторав!4 .

Недостатком известного микропрограммного устройства является низкое . быстродействие.

Цель изобретения — повышение быстродействия устройства..

1Е . Эта цель достигается тем, что в устРойство вФедены задающий генератор, распределитель импульсов, счет., чик, два дополнительных коммутатора, два дополнктельных элемента И, элемент ИЛИ. Информационные входы дополнительных коммутаторов соединены с соответствующими выходамн распределителя.импульсов, адресные входы с выходаии счетчика. Выход первого . дополнительного комчутатора соединен

2O со вторим входои первого элемента И . и:о первым:входом первого дополнительного элемента И. Выход второго дополнительного коммутатора соединенс вторим вмодои второго элемента И и с первым входом второго дополнительного .элемента й. Вторые входы пер-. вого к:второго дополнительных элементов:И соединены соответственно с нулевымй вйисодами второго к первого

30 триггеров. Выходы дополнительных

862141 блокирует прохождение тактового импульса через элемент И 6(5) и раз- . блокирует прохождение тактоного импульса через элемент И 12(11) и коммутатор 3(4). При этом адрес следующей микрокоманды, записанный адресной частью считанной микрокоманды s регистр адреса 8(7) первым тактовым импульсом, поступившим с выхода коммутатора 15(14), перезапи© сывается через коммутатор 3(4) в регистр адреса 7 (8). Таким образом, через время t< в регистре адреса

7(8) устанавливается адрес считываемой микрокоманды. Кроме того, первый тактовый импульс проходит через элеИ мент И 12(11) и элемент ИЛИ 13 на вход счетчика 18, находящегося н

1-м состоянии. По срезу этого импульса счетчик 18 переходит н (1+1)-е состояние. При этом второй тактовый

Щ импульс появляется на выходе коммутатора 14 (15) через Т = Т после . первого тактового импульса. С приходом этого импульса на элемент

И 5(.б) на выходе запоминающего блока д 9(10) через некоторое время появится считанная микрокоманда. Если после этой считываемой микрокоманды необходимо вновь перейти к четной (нечетной.1 микрокоманде, то в считываемой

ЗО микрокоманде появится сигнал, который по второму выходу 21(22) запоминающего блока 9(10) установит триггер

2(1) в противоположное, т.е. в единичное состояние. При этом элемент

И 12(11) заблокируется, состояние счетчика 18 с приходом следующего тактового импульса не изменится и полупериод следования тактовых импульсов будет Т »

Таким образом, предложенное уст о ройство позволяет в и раз сократить время задержки t g при переходе от нечетной (четной) микрокоманды к нечетной (четной) за счет сокращения полупериода следования тактовых

45 импульсов.

Формула изобретения элементов И соединены с соответствующими входами дополнительного .элемента ИЛИ, выход которого соединен с входом счетчика; Выход задающего генератора соединен с входом распределителя импульсов.

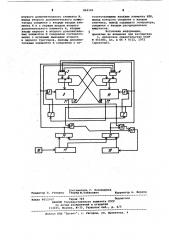

На чертеже приведена структурная схема устройства.

Микропрограммное устройство управления содержит триггеры 1 и 2, коммутаторы 3 и 4, элементы И 5 и 6, ре« гистры адреса 7 и 8, запоминающие блоки 9 и 10, дополнительные элементы И 11 и 12, элемент ИЛИ 13, дополнительные коммутаторы (мультиплексоры) 14 и 15, задающий генератор

1б, распределитель импульсов 17 и счетчик 18. Первые выходы 19 и 20 и вторые выходы 21 и 22 запоминающих блоков..

Принцип работы устройства заключается в сокращении полупериода следо.вания импульсов, снимаемых с выходов коммутаторов 14 и 15 при реализации перехода от нечетной (четной) микрокоманды к нечетной (четной).

Пусть счетчик 18 находится в

1-ом состоянии, которое определяет коммутацию 1-х информационных входов коммутаторов. При этом к выходу каждого коммутатора подключается его

1--е входы. йолупериод следования импульсов, снимаемых с выходом коммутаторов

14 и 15, определяется паузой между появлением импульсов на выходах распределителя импульсов 17, соединенных соответственно с 1-ми подключенными входами коммутаторов 14 и

15, По срезу приходящего на вход счетчика 18 импульса оН переходит н следующее (1+1)-е состояние.е. При этом к выходам коммутаторов подключаются (1+1)-е информационные входы, и следующий тактовый ймпульс появится через период следования импульсов задающего генератора.

Устройство работает следующим образом.

В том случае, когда отсутствует необходимость перехода от нечетной (четной) микрокоманды к нечетной (четной), триггеры 1 и 2 находятся в единичном состоянии. При этом раэблокированы элементы И 5 и 6, но заблокированы элементы И 11 и 12 и коммутаторы 3, 4 °

С выходов коммутаторов 14 и 15 поступают тактовые импульс@ с полупериодом, Устройство в этом случае работает аналогично устройству по авт. св.

Э 451080. При необходимости перехода от нечетной (четной) микрокоманды 46 к нечетной (четной) на втором выходе

21(22) запоминающего блока 9(10) считывается единица, которая устанавливает триггер 2(1) в нулевое состояние. При этом триггер 2(1) Микропрограммное устройство управления по ант. св. М 451080, о тл н ч а þ ù е е с ÿ тем, что, с целью повышения быстродействия, н устройство введены задающий генератор, распределитель импульсон, счетчик, два дополнительных коммутатора, дна дополнительных элемента И, элеМент ИЛИ, причем информационные входы дополнительных коммутаторон соединены с соответствующими выходами распределителя импульсов, адресные входы дополнительных коммутаторов соединены с выходами счетчика, выход первого дополнительного коммутатора соединен с вторым входом первого элемента И и с первым входом

8б2141

Составитель F. Пономарева

Редактор Л. Утехина Техред М.Табакович Корректор А. Ференц

Заказ 6613/43 Тираж 745 Подписное

Вниипи Государственного кожтета СССР по делам изобретений и Откр атей

113035, Москва, Ж-35, Раутская наб., д. 4/5

Филиал tItIII "Патент", r. ужгород, ул. Проектная, 4

;первого дополнительного элемента И, выход второго дополнительного коммутатора соединен с вторым входом эле-. мента И и с первым входом второго дополнительного элемента И, вторые входы первого и второго.дополнительных элементов.И соединены соответственно с нулевыми выходами второго и первого триггеров, .выходы дополнительных элементов И соединены с соответствующими входами элемента ИЛИ, выход которого соединен с входом счетчика,. выход задающего генератора, соединен с входом распределителя импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 451080. кл, в 06 F 9/12, 1972 (прототип).