Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 862237

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсник

Социалистичесник

Реслублин (61) Дополнительное к авт. свид-ву— (22) Заявлено 28.01.80 (21) 2873722/18-24 с присоединением заявки №вЂ” (51) М. Кл.

G 11 С 17/00

Гееударствеллмй кемитет (23) Приоритет 17.02.78 согласно заявке № 258721/18-24

Опубликовано 07.09.81. Бюллетень №33 (53) УДК 681.327..6 (088.8) ло делам изобретений и вткрмтий

Дата опубликования описания 12.09.81 (72) Авторы изобретения

Ю. А. Бузунов, И. Г. Буренков, И. Б. Шубинский и Н. П.,Чипчигин (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области цифровой вычислительной техники и может быть использовано в запоминающих устройствах

ЦВМ с хранением фиксированной информации, при построении процессов и управляющих вычислительных систем на постоянной памяти, а также в устройствах защиты, шифрования и передачи информации.

Известны постоянные запоминающие устройства (ПЗУ), содержащие входной (адресный) дешифратор, выходы которого соединены с соответствующими входными шинами .матричного накопителя, выходной дешифратор (разрядных шин), выходы которого соединены с управляющими входами элементов совпадения и элементов ИЛф

Недостатком этого устройства является наличие, в нем большого количества входных и разрядных шин, большого количества запоминающих элементов.

Наиболее близким техническим решением

К изобретению является ПЗУ (2), содержа åå матричный накопитель с 2я запоминаюшими элементами в каждой строке, раз- 20 рядными и адресными шинами, при этбм адресные шины соединены с соответствующими выходами первого дешифратора, а выходь второго дешифратора подключены к первым входам соответствуюших 2г элементов И, выходы которых соединены с соответствующими 2ъ. входами элемента ИЛИ.

Это устройство содержит большое количество адресных разрядных шин и запоми- ° наюших элементов, каждый из которых хранит только один бит информации. Это приводит к усложнению блоков памяти, увеличению габаритов ЗУ, его стоимости и к снижению надежности работы устройства.

Целью изобретения является повышение информационной емкости и надежности устройства.

Указанная цель достигается тем, что в ПЗУ, содержашем матричный накопитель с 2т запоминающими элементами в каждой строке, разрядными и адресными шинами, при этом адресные шины соединены с соответствующими выходами первого дешифратора, а выходы второго дешифратора подключены к первым входам соответствующих

2 ъ элементов И, выходы которых соединены с соответствующими 2 и входами элемента

ИЛИ, информационные входы элементов И соответственно соединены с (т + 1) разрядными шинами накопителя, начиная с первой, 862237 со сдвигом вправо на одну разрядную шину, а накопитель содержит дополнительные адресные шины, каждая из которых пропущена через вторые г запоминающих элементов предыдущей строки накопителя и первые т запоминающих элементов последующей строки, а дополнительная адресная шина, проходящая через вторые Ф1 запоминающих элементов последней нечетной строки, проходит через первые 71 запоминающих элементов первой нечетной строки.

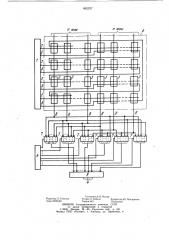

На чертеже представлена схема предлагаемого ПЗУ.

Оно содержит первый дешифратор 1, адресные шины 2, запоминающие элементы 3 накопителя 4, дополнительные адресные шины 5, второй дешифратор 6, элементы И 7, разрядные шины 8 и элемент ИЛИ 9.

Устройство работает следующим образом.

Первый дешифратор 1 после расшифровки старших разрядов адреса возбуждает соответствующую адресную шину 2 или 5, тем самым выбирается группа сжатых слов.

Так как количество запоминающих элементов 3 на каждой адресной шине (четной и нечетной) одинаково, то ширина выборки для каждой из них постоянна. Число выбираемых слов в группе определяется числом разрядных шин 8 накопителя 4 и равной.

Второй дешифратор 6 после расшифровки младших разрядов адреса открывает один из элементов И 7 и тем самым выбирает одно из слов группы. При возбуждении соответствующей адресной шины и выборе элемента И 7 считывается определенное (ф+ 1) разрядное слово, которое через выбранный элемент И 7 и элемент ИЛИ 9 поступает на выход устройства.

Технико-экономические преимущества предлагаемого устройства заключаются в повышении его надежности за счет уменьшения числа запоминающих элементов в накопителе при хранении в нем одного и того же объема информации. Количество

Ф запоминающих элементов Q) накопителя предложенного устройства и прототипа соответственно определяются выражениями:

371 = Ю тл Фа

Так, например, при емкости 1 = 512 9разрядных слов количество запоминающих элементов в накопителе для предложенного устройства равно 512, а для известного требуется 4608. Количество запоминающих элементов сокращается в и раз. В это же число раз может быть увеличена информационная емкость устройства. формула изобретения;

10 1. Постоянное запоминающее устройство, содержащее матричный накопитель с 2й запоминающими элементами в каждой строке, разрядными и адресными шинами, при этом адресные шины соединены с соответствующими выходами первого дешифратора, а выходы второго дешифратора подключены к первым входам соответствующих 2 элементов И, выходы которых соединены с соответствующими 2п входами элемента ИЛИ, отличающееся тем, что, с целью повышения

20 информационной емкости и надежности устройства, информационные входы элементов

И соответственно соединены с (f3+ 1)-разрядными шинами накопителя, начиная с первой, со сдвигом вправо на одну разряд25 ную шину.

2. Устройство по п. 1, отличающееся тем, что накопитель содержит дополнительные адресные шины, каждая из которых пропущена через вторые 13 запоминающих

30 элементов предыдущей строки наполнителя и первые tl запоминающих элементов последующей строки, а дополнительная адресная шина, проходящая через вторые g запоминающих элементов последней нечетной

35 строки, проходит через первые Ь заломинающих элементов первой нечетной строки.

Источники информации, принятые во внимание при экспертизе

1. Вопросы радиоэлектроники. Серия

«Электронная вычислительная техника», выпуск Хо 1, 1975, с. 14, рис. 6.

2. Брик Е. А. Техника ПЗУ. «Советское радио», 1973, с. 15, рис. 2.1. (прототип).

862237

Составитель В. Вакар

Редактор Л. Утехина Техред А. Бойкас Корректор 10.Макаренко

Заказ 6624/48 Тираж 645 Г1однисное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4