Цифровой корректор сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВХ

Союз Советскик

Социалистическик

Республик (Ä) 862366 (61) Дополнительное к авт. свид-ву— (22) Заявлено 14.03.79 (21) 2739358/18-09 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

Н 04 В 3/04

Гооударственнык комитет (53) УДК 621.395..664 (088. 8) Опубликовано 07.09.81. Бюллетень № 33

Дата опубликования описания 17.09.81 па делам изобретений и открытий (72) Авторы изобретения

С. В. Стукалов и Л. Г. Израильсон (71) Заявитель (54) ЦИФРОВОЙ КОРРЕКТОР СИГНАЛОВ

Изобретение относится к электросвязи и может использоваться для коррекции межсимвольной интерференции в модулированных сигналах.

Известен цифровой корректор сигналов, содержащий аналого-цифровой преобразователь, выходы которого подключены к первым входам блока памяти и программного блока, причем первый выход последнего подключен ко второму входу блока памяти, первым входам блока памяти коэффициентов и арифметического блока, выход которого является выходом устройства, а второй вход через блок памяти коэффициентов пддключен к выходу блока корреляции, второй выход блока памяти соединен с третьим входом арифметического блока, второй выход которого подключен к третьему входу блока памяти (11.

Однако у известного устройства наличие постоянной составляющей в сигнале на выходе корректора существенно снижает помехоустойчивость передачи.

Цель изобретения — повышение помехоустойчивости.

Для этого в известный цифровой корректор сигналов, содержащий аналого-цифровой преобразователь, выходы которого подключены к первым входам блока памяти и программного блока, первый выход последнего подключен ко второму входу блока памяти, первым входам блока памяти коэффициентов и арифметического блока, выход которого является выходом устройства, а второй вход через блок памяти коэффициентов подключен к выходу блока корреляции, второй выход блока памяти соединен с третьим входом арифметического блока, второ рой выход которого подключен к третьему входу блока памяти, введен блок управления. При этом выходы блока управления подключены к входам управления блока памяти, блока корреляции и программного блока соответственно. Первый выход последне1 го подключен к третьему входу блока корреляции, а второй выход — к входу блока управления.

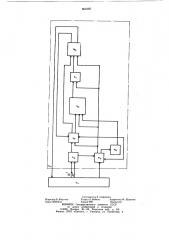

На чертеже представлена структурная электрическая схема предложенного устройства.

Цифровой корректор сигналов содержит приемник 1, цифровой корректор 2, аналогоцифровой преобразователь 3, блок 4 памяти, программный блок 5, блок 6 корреля862366 ции, блок 7 памяти коэффициентов, арифметический блок 8 и блок 9 управления.

Устройство работает следующим образом.

Аналоговые сигналы с выходов демодуляторов приемника 1 поступают на аналого-цифровой преобразователь 3, где производятся стробирование этих сигналов в отсчетные моменты времени, запоминание и хранение амплитуд полученных напряжений выборок и преобразование этих напряжений в п-разрядные кодовые числа.

Преобразование производится так, что сначала преобразуется сигнал с выхода первого демодулятора a.> а затем — сигнал с выхода второго демодулятора Ю; приемника 1. В такой же очередности производится запись в блок 4 памяти двух п-разрядных чисел выборок, полученных в результате преобразования. В тот же блок с выхода арифметического блока 8 записываются данные

1 Ю о полярности сигналов а; и а; на выходах цифрового ко ректора 2/Sgna, -, Sgna;"/ и сигналы Sgnl; и Ядп1;, отображающие знак отклонения откорректированных сиге В налов а- и а> от нормированного значения. и

На основании анализа этих сигналов, выводимых из блока 4 памяти по командам программного блока 5, и в соответствии с выбранным алгоритмом работы цифрового корректора 2 в блоке 6 корреляции вырабатываются сигналы о направлении изменения коэффициента передачи соответствующего отвода корректора 2, которые в виде и-разрядных чисел хранятся в блоке 7 памяти коэффициентов. В каждом такте работы программного блока 5 из блоков 4 и 7 в блок умножения арифметического блока 8 поступают два п-разрядных кодовых чисела, соответствующие модулям и полярностям кодов коэффициента передачи и выборки для соответствующего отвода корректора 2.

При этом сначала в арифметический блок 8 поступает код выборки первого демодулятора а;, а затем — код выборки второго демодулятора а; приемника 1 для умножения на один и тот же код коэффициента передачи регулятора. Полученные произведения двух пар чисел записываются по командам, поступающим из программного блока 5 в один из двух сумматоров арифметического блока 8 с целью сложения произведений раздельно для выборок сигнала с выходов двух демодуляторов.

В следующем такте работы программного блока 5 из блоков 4 и 7 на входы блока 8 будут поданы кодовые числа, соответствующие следующему отводу корректора 2.

Полученные произведения алгебраически складываются в соответствующих сумматорах блока 8 с числами, хранящимися в нем от предыдущего такта работы блока 5 для предшествующего отвода корректора 2.

Этот процесс будет продолжаться до тех пор, пока в сумматорах блока 8 не будут записаны суммы, полученные в результате сложения произведений кодов выборки и коэффициентов передачи для всех отводов корректора 2.

В процессе настройки корректора 2 в блоке 7 записываются такие числа коэффи15 циентов передачи для регуляторов отводов, при которых величина межсимвольных интервалов минимальна.

Таким образом, за счет введения блока управления в цифровой корректор компенсируется постоянная составляющая в сигналах, что повышает помехоустойчивость передачи сигналов данных.

Формула изобретения

Цифровой корректор сигналов, содержащий аналого-цифровой преобразователь, выходы которого подключены к первым входам блока памяти и программного блока, первый выход последнего подключен ко второму входу блока памяти, первым входом блока памяти коэффициентов и арифметического блока, выход которого является выходом устройства, а второй вход через блок памяти коэффициентов подключен к выходу блока корреляции, второй выход блока памяти соединен с третьим входом арифметического блока, второй выход которого подключен к третьему входу блока памяти, отличающийся тем, что, с целью повышения

4р помехоустойчивости, введен блок управления, при этом выходы блока управления подключены к входам управления блока памяти, блока корреляции и программного блока соответственно, первый выход последнего подключен к третьему входу блока корреля4 ции, а второй выход — к входу блока управления.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3633105, кл. 325-42, 1970 (прототип).

862366

Составитель Е. Смирнова

Редактор Б.Федотов Техред А. Бойкас Корректор М. Шароши

Заказ 6634/53а Тираж 698 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, . г. Ужгород, ул. Проектная, 4