Синтезатор сигналов для электромузыкального инструмента

Иллюстрации

Показать всеРеферат

А. N, Криштафор, В. А. Беляков, В. Н. Писарев и А. И. Каниболоцкий : .....,, 1

i (72) Авторы изобретения (7I) Заявитель (54) СИНТЕЗАТОР СИГНАЛОВ ДЛЯ ЭЛЕКТРОМУЗЫКАЛЬН ХО

ИНСТРУМЕНТА

Изобретение относится к электромузыкальным устройствам.

Известен синтезатор сигналов для электромузыкального инструмента (ЭМИ), содержаший тональные генераторы, ключевые модуляторы, смесители, фильтры, клаS виатуру (1).

Данный синтезатор не обеспечивает достаточного числа синтезируемых сиги лов.

Наиболее близким по технической сущ10 ности к предлагаемому является синтезатор сигналов, содержаший ТОН-генератор, блок клавиатуры, вход которого соединен с выходом источника постоянного напряжения, а выходы через диоды подключе15 ны к одному из контактов переключателя, второй контакт которого соединен с выходом генератора тактов, а третий контакт соединен с входом кольцевого счетчика, выходы разрядов которого соединены с входами управления блоков памяти, состояших иэ элемента И и последовательно соединенных ключей и конденсаторов, приЭ чем входы управления ключей соединены с вт.ходом элемента И, входы которого подключены к входам управления данного блока памяти (21.

Однако данный синтезатор характеризуется недостаточной точностью и стабильностью выходных сигналов.

Белью изобретения является увеличение точности и стабильности выходных сигналов.

Поставленная цель достигается тем, что в синтезатор сигналов для электромузыкального инструмента, содержащий TOHгенератор, блок клавиатуры, вход которого соединен с выходом источника стоянного напряжения, а выходы через диоды подключены к одному из контактов переключат ля, второй контакт которого соединен с выходом генератора тактов, а третий контакт соединен с входом кольцевого счетчика, выходы разрядов которого соединены с входами управления N блоков памяти, состояяцис иэ элемента И и последовательно соединенных ключей и конденсаторов, причем входы управления

8643 ключей соединены с выходом элемента И, входы которого подключены к входам управления данного блока памяти, введены N б лnоo1к1оoв n а др е с а1ц1иnиn, элемент ИЛИ, регистра сдвига и генератор импульсов, выход которого соединен с входом сброса регистра сдвига и первым входом каждого блока адресации, вторые входы которых подключены к выходам блока клавиатуры, третьи входы соединены с выходами ТОН-генератора, четвертые входы соединены с выходом кольцевого счетчика и одним входом элемента ИЛИ, пятые входы соединены с выходом последнего разряда регистра сдвига и вторыми входами управления чет15 ных блоков памяти, вторые входы управления нечетных блоков памяти соединены с выходом первого разряда регистра сдвига, информационный вход которого соединен с шестым входом первого блока адресации и выходом элемента ИЛИ, второй

20 вход которого соединен с первым контактом переключателя, причем шестой вход каждого последующего блока адресации соединен с выходом предыдущего блока

25 адресации, а адресные выходы всех блоков адресации соединены с вторыми входами ключ и всех 6,эков памяти.

Блок адресации содержит дешифратор, входь которого соединены с адресными выходами блока адресации и с выходами

30 шифратора, вход которого подключен к выходу первого элемента И, один вход которого соединен со вторым входом блока адресации,а второй вход с первым выходом

3К -триггера, второй выход которого че рез диод подключен к выходу второго элемента И и выходу блока адресации, первый вход 3k -триггера соединен с первым входом блока адресации, а второй вход подключен к выходу третьего элемента И, 40 один вход которого соединен с вторым входом блока адресации и через инвертор с первым входом второго элемента И, вторые входы второго и третьего элементов И подключены к шестому входу блока 4> адресации, причем выход дешифратора соединен с первым входом йб -триггера, второй вход которого подключен к четвертому блоку адресации, а выход соединен с одним входом ключа, второй вход кото- $0 рого соединен с третьим входом блока адрееации, пятый вход которого соединен с третьим входом 1К -триггера, при этом выходы ключей всех блоков адресации подключены к выходу синтезатора.

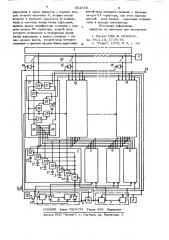

На чертеже приведена структурная электрическая схема описываемого синтезатора.

26 4

Синтезатор содержит TOH-генератор 1

1 блоки 2-э памяти, кольцевой счетчик 6, регистр 7 сдвига, генератор 8 импульсов, элемент ИЛИ 9, блок 10 клавиатуры, источник 1 1 постоянного напряжения, тактовый генератор 12, переключатель 13, диоды 14-16, блоки 17-19 адресации, каждый из которых состоит из дешифратора

20, R,G -триггера 21, ключа 22, элементов И 23-25, шифратора 26, инвертора

27, 3К -триггера 28, диода 29. Каждый блок памяти содержит ключи 30, конденсаторы 31, запоминающий элемент И 32.

Выходной сигнал снимается с выхода 33.

Синтезатор работает следующим образом.

При записи в память музыкальной линии переключат ль 13 подключает объединенные через диодьr выходы блока клавиатуры 10 к триггерам кольцевого счетчика 6. При этом один из триггеров счетчика 6 установлен в положение единицы на его выходе, которая поступает на и ервы и вход элемента 3 2, соответствующего этому триггеру блоков памяти 2 и 3, а также подается через элемент ИЛИ 9 на вход первого триггера регистра сдвига 7 и запускает последний.

Триггеры регистра сдвига 7 поочередно выдают на своих выходах логическую единицу, причем скорость переключений определяется частотой следовании импульссв генератора импульсов 8, которая выбирается достаточно высокой, с целью сделать незаметным неодновременное появление тонов аккорда на выходе синтезатора. циклы работы регистра сдвига повторяются каждый раз при очередном переключении кольцевого счетчика, а также при нажатии одной или нескольких клавишей блока клавиатуры. Каждое переключение очередного триггера регистра сдви« га сопровождается появлением логической единицы на втором входе элемента И соответствующего блока памяти. I аким образом, за один ход кольцевого счетчика производится быстрое (по сравнению с длительностью такта) поочередное открытие блоков памяти. Одновременно импульсы генератора 8 подаются на 3 -входы 3Утриггеров блоков адресации. В случае, когда некоторые клавиши блока клавиатуры нажаты, на первые входы элементов И

23 блоков 17-19 поступает логическая единица. Кроме того, логическая единица поступает на второй вход элементов И

24 блоков 17-19, а на вторых входах элементов И 25 этих блоков в связи с наличием инвертора 27 устанавливается изобретенйя

1. Синтезатор сигналов для электрому зыкального инструмента, содержащий

5 8643 логический ноль. В результате 3К -триггеры блоков 17-19 всех нажатых клавишей оказываются набранными в схему, аналогичную по структуре регистру сд- ига, который оказывается своим входом подключенным к входу первого триггера регистра сдвига 7, вследствие чего работа набранного из З -триггеров блоков 17-19 нажатых клавишей регистра сдвига и регистра сдвига 7, начинается одновременно и протекает синхронно. При этом каждый очередной -триггер, срабатывая, подает логическую единицу на второй вход элемента И 23, эта единица затем через шифратор 26 записывается в соответст-15 вуюшие установленному в данном шифраторе 26 коду запоминающие конденсаторы

31 открытому в это время блоку памяти.

Одновременно срабатывает дешифратор 20 этого же блока адресации и устанавливает

В% -триггер 21 в состояние единицы на его выходе, в результате чего открывается ключ 22, который подключает соответствующий нажатой клавише выход генератора 1 к выходу синтезатора, чем обеспечивает контроль записываемой программы. При срабатывании последнего триггера регистра сдвига 7 происходит установка в нулевое состояние BcBxD K -триггеров, а в момент отпускапия всех нажатых клавишей происходит сдвиг кольцевого счетчика 6 на один регистр, и установка в нулевое состояние всех ЙЬ -триггеров, что приводит к запнрапию ключей. Подготовленными к работе оказываются очередные блоки памяти, соответствующие очередному триггеру кольцевого счетчика G. При нажатии очередных клавишей процесс записи повторяется. Если нажата в данном такте только одна клавиша, то зались ее адресного кода произведется только в первый блок памяти очередной группы, а в остальные блоки данной группы запишутся нули.

При воспроизведении переключатель 13 соединяет триггеры кольцевого счетчика

6 с генератором 12. Тактовые импульсы управляют работой кольцевого счетчика

6, который совместно с регистром

7 сдвига,в описанном выше порядке, открывает ключи блоков памяти. При этом срабатывают соответствующие дешифраторы, триггеры и ключи, которые подключат к выходу синтезатора выходы генера тора 1 в соответствии с записанной программой.

Формула

26 6

ТОН-генератор, блок клавиатуры, вход которого соединен с выходом источника постоянного напряжения, а выходы нарез диоды подключены к одному из контактов переключателя, второй контакт которого соединен с выходом генератора тактов, а третий контакт соединен с входом кольцевого счетчика, выходы разрядов которого соединены с входами управления М блоков памяти, состоящих из элемента И и последовательно соединенных ключей .r кKо нHд еGнHс а т оoр ов, причем входы управления ключей соединены с выходом элемента И, входы которого подключены к входам управления данного блока памяти, о т л и ч а ю ш и )1 с я тем, что, с целью увеличения ч очности и стабильности выходных сигналов, в него введены

М блоков адресации, элемент ИЛИ, регистр сдвига и генератор импульсов, выход которого соединен с входом сброса регистра сдвига и первым входом каждого блока адресации, вторые входы которых подключены к выходам блока клавиатуры, третьи входы соединены с выходами ТОН-генератора, четвертые входы соединены с выходом кольцевого счетчика и одним входом элемента ИЛИ, пятые входы соединены с выходом последнего разряда регистра сдвига и вторыми входами управления четных блоков памяти, вторые входы управления нечетных блоков памяти соединены с выходом первого разряда регистра сдвига, информационный вход которого соединен с шестым входом первого блока адресации и выходом элемента

ИЛИ, второй вход которого соединен с первым контактом переключателя, причем шестой вход каждого цоследуюшего блока адресации соединен с выходом предыдущего блока адресации, а адресные выходы всех блоков адресации соединены с вторыми входами ключей всех блоков памяти.

2. Синтезатор по и. 1, о т л и ч аю ш и и с я тем; что блок адресации содержит дешифратор, входы которого соединены с адресными выходами блока адресации и с выходами шифратора, вход которого подключен к выходу первого элемента И, один вход которого соединен со вторым входом блока адресации, а второй вход г первым выходом к -триггера, второй выход которого через диод подключен к выходу второго элемента И и выходу блока адресации, первый вход. К-триггера соединен с первым входом блока адресации, а второй вход по,шслючен к выходу третьего элемента И, один вход ко торого соединен с вторым входом блока

8643 адресации и через инвертор с первым входом второго элемента И, вторые входы второго и третьего элементов И подключены к шестому входу блока адресации, нричем выход дешифратора соединен с первым входом -триггера, второй вход которого подключен к четвертому входу блока адресации, а выход соединен с одним входом ключа, второй вход которого соединен с третьим входом блока адресации, 26 8 пятый вход которого соединен с третьим входом J N. -триггера, при этом выходы ключей всех блоков адресации подключены к выходу синтезатора.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3836693, кл. 84-1.19, 17.09.74.

2. Радио", 1979, № 3, с. 19.

ВНИИПИ Заказ 7803/74 Тираж 409 Подписное филиал ППП Патент", г. Ужгород, ул. Проектная, 4