Программируемое логическое устройство

Иллюстрации

Показать всеРеферат

Б. И. Рувинский и С. A. Селютин (72) Авторы изобретения (7i) Заявитель (54) ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике.

Известны программируемые логические устройства в интегральном исполнении, состояшие из двух последователь- но включенных матриц, первая из которых является дешифратором входньж слов, а вторая - полем памяти, хранящим выходные слова. Каждая из матриц представляет собой набор вентилей HE-ИЛИ Ы.

Недостаток таких устройств - нали10 чие значительного числа общих шин.

Наиболее близким техническим .решением к изобретению является устройс во, состоящее из двух последовательно1Б включенных матриц, каждая иэ которых содержит нагрузочные МОПгранзисторы, подключенные между шиной питания и соответствуюшей.выходной шиной и столбцы, образованные МОП-транзисторами, 20

° затворы которых подключены к соответствующей входной шине, истоки - к обшей шине, стоки МОП-транзисторов каж дого столбца первой матрицы и стоки

МОП транзисторов первого и последне» го столбца второй матрицы - к соовветствующей выходной шине, стоки МОП .транзисторов остальных соседних столбцов второй матрицы подключены к одной соответствующей выходной шине (2 °

Однако известное устройство обладает наличием значительного числа общих шин, что приводит к усложнению устройства, увеличению занимаемой плошади, повышению стоимости, Цель изобретения - упрощение устройства, уменьшение занимаемой плоша» ди и снижение стоимости.

Поставленная цель достигается тем, что в программируемом логическом устройстве, состояшем из двух пос« ледовательно включенных матриц, каждая из которых содержит нагрузочные МОП« транзисторы, подключенные между шиной питания и соответствующей выходной шиной и столбцы, образованные МОП гранзисторами, затворы которых подключены к соответствующей входной шине, истоки

864338

МОП-транзисторов первого столбца первой матрицы и истоки МОП-транзисторов каждого столбца второй матрицык обшей шине, стоки МОП-транзисторов каждого столбца первой матрицы и первого и последнего столбца второй мач рицы подключены к соответствующей выходной шине, а стоки МОП-транзисторов остальных каждых двух соседних столбцов второй матрицы подключень к одной соответствующей выходной шине, в каждом из столбцов первой матрицы, кроме первого, истоки NOIl-транзисторов подключены к стокам МОП-транзисторов предыдущего столбца этой матрицы.

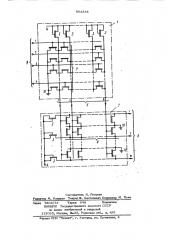

На чертеже представлена принципиа» льная электрическая схема программируемого логического устройства, Устройство содержит две последовательно включенные. матрицы 1 и 2, каждая иэ которых содержит нагруэочные МОП- транзисторы 3, подключенные между шинами 4 питания и одной из выходных шин 5 первой матрицы и, соответственно, одной из выходных шин 6 второй матрицы, и столбцы .7 и 8, образованные МОП- транзисторами 3 затворы кото,алых в матрице l подключены, соответственно, у первых

МОП-транзисторов 3 столбцов

7 к первой из входных шин 9 а в матрице 2 затворы МОП транзисторов 3 каждого столбца 8 подключены, соо ветственно, к одной из шин 5, которые являются выходными для матрицы 1 и входными для матрицы 2. Истоки МОПтранзисторов 3 первого из столбцов 7 матрицы 1 и истоки МОП-транзисторов

3 каждого из столбцов 8 подключены к общим шинам 10, стоки МОП-транзисторов 3 каждого столбца 7 матрицы

1 и первого и последнего иэ столбцов

8 матрицы 2 подключены, соответственно, к одной иэ выходных шин

5 или 6, а строки остальных каждых двух соседних столбцов 8 подключены, соответственно, к одной из выходных шин

6. В каждом иэ столбцов 7, кроме первого,, истоки МОП-транзисторов 3 подключены к стокам МОП-транзисто ров 3 предыдущего столбца.

Устройство работает следующим образом.

На входные шины 9 матрицы 1 пос тупает определенный набор двоичных сиг налов, который выбирает один иэ столбцов 7 МОП-транзисторов 3, т.е. запи рает все транзисторы этого столбца.

Нагрузочные МОП-транзисторы 3, находясь в открытом состоянии, обеспечивают прохождение высокого потенQBB JIG oT шины питания. 4 к одной иэ выходных шин 5. При этом связь указан» ной выходной шины с общей шиной 10 отсутствует, поскольку МОП-транзисторы 3 заперты. Лалее этот сигнал пос1О тупеет на одну из входных шин матрицы 2, попадая на затворы соответствующих МОП-транзисторов 3 в толбцах 8, этот сигнал отпирает их и приводит к появлению низкого уровня потенциала

)5 на соответствующих выходных шинах 6, поскольку указанные выходные шины подключаются к общим шипам 4, В тех же столбцах, где отсутствуют связи затворов МОП-транзисторов 3 с вход20 ной шиной, происходит появление высокого уровня потенциала на соответствующих выходных шинах 6, благодаря тому, что нагрузочные МОП-транзисторы 3 находятся в открытом состоянии и обес25 печивают поступление высокого уровня потенциала от шины питания 4 на соответствуюшую выходную шину 6.

На всех выходных шинах 5, расположенных дальше от общей шины 10, чем выбранная входами сигналом шина, также появляется высокий потенциал. Поэтому для правильной работы устройства необходимо, чтобы слова, выбираемые из матрицы 2 соседними выходными шинами 5, удовлетворяли определенному условию поглошетщя. Оно заключается в том, что слово, выбираемое первой из шин 5 (т. е. соседней с обшей шиной 10) поглощает все другие, сло4, во, выбираемое вторым иэ шин 5, поглощает вс<; последующие (кроме первого) и т.д.

Заметим, что удсвгетворить указанному условию в случае реальных дискрет45 ных устройств достаточно просто,для этого следует лишь расположить слова, хранимые в матрице 2, в надлежащем порядке. При необходимости выходные. слова могут быть также разбиты на со50 ответствующие группы, внутри каждой из которых указанный порядок соблюдается.

Предлагаемое устройство йозволяет иметь лишь одну общую шину, приходя-" щуюся на и столбцов первой матрйцы.

55 Это упрощает схему устройства, и, при значениях 7j 10 (которые являются характерными,для современного уровня развития интегральной технологии), 5 сокращает плошадь интегральной схемы примерно в 1,5 раза, что снижает ее стоимость.

Формула изобретения

Программируемое логическое устройство, состоящее иэ двух последователь но включенных матриц, каждая иэ которых содержит нагрузочные МОП-транзисторы, подключенные между шиной питания и соответствующей выходной ши ной и столбцы, образованные МОП.транзисторами, затворы которых подключены к соответствующей входной шине, истоки МОП-транзисторов первого столбца первой матрицы и истоки МОП-транзисторов каждого столбца второй матриш к обшей шине, стоки МОП-транзисторов каждого столбца первой матрицы и перво» го и последнего столбца второй матри4338 6 цы подключены к соответствуюшей выкодной шине, а стоки МОП-транзисторов остальных каждых двух соседних столбцов второй матрицы подключены к одной соответствующей выходной шине, о тлячаюшееся тем, что, с целью упрощения устройства, уменьшения занимаемой плошади и снижения стоимости, в каждом из столбцов первой матрицы, кроме первого, истоки МОП-транзисторов подключены к стокам МОПгранэисторов предыдущего столбца этой матрицы.

Источники информации, принятые во внимание при экспертизе

1. Рувинский Б. И. Реализация микропрограммного автсмата на БИС."Электронная техника", сер, Я "Мйкроэлектроника", вып. 5 (53), 1974, „c. 22-26.

2, Патент СЦ% ¹ 3702985, кл. 340-166, 1974.

864338

Составитель И. Петрова

Редактор М. Бандура ТехредЖ. Кастелевич Корректор М. Пожо

Заказ 7804/74 Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и otKpbITBk

113035, Москва, Ж -35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Пр>ектная, 4