Устройство для синхронизации импульсов

Иллюстрации

Показать всеРеферат

Союз Сеаетсник

Соцналнстнчесння

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ВТВЛЬСТВУ (6! ) Дополнительное к авт. свид-ву(22) Заявлено 1 у.1279 (Pf) 2853329/18-21 {51)М, Кл. с присоединением заявки М123) Г3риоритвт—

Н 03 К 5/13

Государственный комитет

СССР оо делам изобретений я открытий

Опубликовано 15.09.81. Бюллетень Йо 34

Дата опубликования описания 15.0981

{53) УДК 681. 326. . 35 (088. 8) (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ

Изобретение относится к импульсной технике, и может быть использовано в устройствах автоматики и вычислительной техники.

Известен синхронизатор импульсов, содержащий три RS-триггера, три элемента И-НЕ н два трехпоэиционных переключателя (1 ).

Известный синхронизатор является сложным и характеризуется узкими областью применения и диапазоном длительностей управляющего сигнала. Это связано с тем, что синхрониэатор позволяет формировать только на одном и том же выходе пачку импульсов при одной коммутации трехпозиционными переключателями входных цепей или одиночный импульс при другой коммутации трехпозицнонными переключателями входных цепей. Таким образом, синхронизатор не позволяет формировать по одному и тому же управляющему сигналу на разных выходах синхронизированные одиночный импульс н пачку нмпульcos. В то же время диапазон длительностей управляющего сигнала должен превышать по длительности период следования импульсов тактовой часто- ты. В противном случае при появлении управляющего сигнала, например, одновременно с паузой тактовой частоты управляющий сигнал может быть не воспринят синхронизатором либо произойдет искажение длительности выходного импульса.

Наиболее близким по технической сущности и достигаемому результату тт предлагаемому является устройство то для синхронизации, содержащее три триггера, элемент совпадения и инвертор, причем первый вход первого триггера соединен с первым входом элемен,та совпадения, второй вход которого соединен с выходом первого триггера, выход элемента совпадения соединен с первым входом второго триггера, первый вход третьего триггера подключеч к выходу первого триггера, второй вход которого соединен с выходом второго триггера, второй вход которого соединен со входом инвертора, выход которого соединен с третъйм входом элемента совпадения и со вторым входом третьего триггера. Данное устройство позволяет формировать од.новременно с одиночным импульсом пачку импульсов (2 J.

Недост ат ком устройств а является узкий диапазон длительностей управляющего сигнала, заключающийся в том, 864528 что управляющий сигнал для формирования неискаженных импульсов на обо-. их выходах должен перекрывать два импульса тактовой частоты. Это связано с тем, что процесс формирования пачки импульсов начинается после окончания одиночного импульса. Но если входной импульс окончится раньше одиночного импульса на выходе, синхронизатор вернется в исходное состояние и пачка импульсов окажется несформированной. В то же время при управляющих сигналах меньших периода тактовой частоты устройство может . вообще не воспринять управляющий сигнал, или одиночный импульс на выходе окажется искаженной длительности .

Цель изобретения — расширение функциональных возможностей устрой ства за счет расширения диапазона длительностей управляющего сигнала.

Поставленная цель достигается тем, что, в устройство для синхронизации импульсов, содержащее три триггера, элемент совпадения и инвертор, причем первый вход первого триггера соединен с первым входом элемента совпадения, второй вход которого соединен с первым выходом первого триггера, второй вход которого соединен с выходом второго триггера, первый вход которого соединен с выходом элемента совпадения, третий вход которого соединен с выходом инвертора, вход которого соединен со вторым входом второго триггера, дополнительно введен элемент совпадения, выход которого соединен с дополнительным входом первого триггера и со входом третьего триггера, выход которого подключен к первому входу первого триггера, второй выход которого соединен с первым входом дополнительного

--"элемента совпадения, второй вход которого соединен с выходом инвертора.

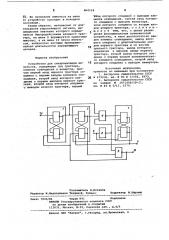

На чертеже приведена принципиальная электрическая схема устройства для синхронизации импульсов. устройство содержит триггеры 1-3, элементы 4 и 5 совпадения,,инвертор

6, шину 7 входного управляющего сигнала, шину 8 импульсов тактовой частоты, шину 9 одиночного импульса, шину 10 пачки импульсов. Триггеры 1-3 построены на двух элементах И-НЕ, элементы 4 и 5 совпадения являются элементами И-НЕ.

Первый вход триггера 2 соединен с первым входом элемента 4 совпадения. Второй вход элемента 4 совпадения соединен с выходом триггера 2.

Второй вход триггера 2 соединен с выходом триггера 3. Первый вход триг гера 3 соединен с- выходом элемента 4 совпадения. Третий вход элемента 4 совпадения соединен с выходом инвертора б. Вход инвертора 6 соединен со вторым входом триггера 3. Выход элемента 5 совпадения соединен с третьи входом триггера 2 и со входом триггера 1. Выход триггера 1 подключен к первому входу триггера 2. Второй выход триггера 2 соединен с первым входом элемента 5 совпадения. Второй вход элемента 5 совпадения соединен с выходом инвертора б.

Шина 7 подключена ко второму входу триггера 1. Шина 8 подключена но второму входу триггера 3. Шина 9 подключена к выходу триггера 3. Шина .;10 подключена к выходу элемента 5 совпадения. устройство для синхронизации работает следующим образом.

В исходном состоянии на шинах 7, 9 и 10, на первом выходе триггера 2 и выходе элемента 4 совпадения присутствует высокий потенциал, а на выходе триггера 1 и на втором выходе триггера 2 присутствует низкий зО потенциал. Импульсы тактовой частоты, поступающие на шину. 8, инвертируются инвертором б, Низкий потенциал, поступая на шину,8, переключает триггер 1. Высокий потенциал, установившийся на выходе триггера 1,. разрешает прохождение паузы тактовой частоты через элемент

4 совпадения. Возникающий при появлении паузы тактовой частоты низкий потенциал,на выходе элемента 4 совЗ® падения подготавливает триггер 3 к срабатыванию в момент появления на его втором входе импульса тактовой частоты. При появлении импульса тактовой частоты на шине 8 на выходе

И триггера 3 устанавливается низкий потенциал, поступающий на шину 9 .и на второй вход триггера 2. Триггер 2 переключается и на его втором выходе устанавливается высокий потенциал, ф) разрешающий прохождение паузы тактовой частоты при ее появлении на шине 8 через элемент 5 совпадения на шину 10. Появляющийся одновременно с этим нкзкий потенциал на первом выходе триггера 2 запрещает прохождение последующих пауз тактовой частоты на выход элемента 4 совпадения, тем самым запрещая прохождение последующих импульсов тактовой частоты на шину 9. IIo окончании импульса тактовой частоты на выходе триггера 2 устанавливается высокий потенциал.

В это же время проинвертированная пауза тактовой частоты поступает на второй вход элемента 5 совпадения. 5 Элемент 5 срвпадения переключается, и низкий потенциал cего выхода поступает на шину 10, на первый вход триггера 1 и третий вход триггера 2.

Если управляющий сигнал уже законщ чился, то триггер 1 переключается в исходное состояние. На первом выходе триггера 2 устанавливается высокий потенциал, но высокий потенциал на втором выходе триггера 2 сохраням ется до окончания импульса на шине

864528

Формула изобретения

Составитель B. Потапов

Редактор М. Недолуженко Техред М. Рейвес Корректор М Шароши

Заказ 7830/84 Тираж 991 Подписное. ВНИИПН Государственного .комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная, 4

10. По окончании импульса на шине

10 устройство приходит в исходное состояние.

Таким образом, независимо от длительности управляющего си "нала, минимальное значение которого определяется быстродействием входного -триггера, на шине 9 формируется одиночный импульс, а на шине 10 пачка импульсов, количество которых пропорцио нально длительности управляющего сигнала.

Устройство для синхронизации импульсов, содержащее три триггера, элемент совпадения и инвертор, причем первый вход первого триггера соединен с первым входом элемента совпадения, второй вход которого. соединен с первым выходом первого триггера, второй вход которого соединен с выходом второго триггера, первый вход которого соединек с выходом элемента совпадения, третий вход которого соединен с выходом инвертора, вход которого соединен со вторым входом второго триггера, о т л и ч а ю— щ е е с я тем, что, с целью расширения функциональных возможностей устройства, в него дополнительно введен элемент совпадения, выход которого соединен с дополнительным вхо © дом первого триггера и со вхо. ом третьего триггера, выход которого подключен к первому входу первого триггера,. второй выход которого сое.динен с первым -входом дополнительного элемента совпадения, второй вход

15 которого соединен с выходом инвертора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Щ 9 479236, кл. Н 03 К 5/156, 1973.

2. Авторское свидетельство СССР по заявке 9 2671408/18-21, кл. Н 03 К 5/13, 1978.