Цифроаналоговый преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Соцналнстнческннх

Реслублнк

Р1)М. Кл.

Н 03 К. 13/02

Государственный комнтет

СССР яо делам мзобретеннй н открытяй (23) Приоритет—

Опубликовано 15.0981. Бюллетень NP 34 (53j ПЖ 681. 325 (088.8) Дата опубликования описания 150981

A.Ï.Ñòàõoâ, A.Ä.Àçàðoâ, В.И.Моисеев и Ю.A. етрбсюк !! (72) Авторы изобретения

-, °

1 (71) Заявитель

Винницкий политехнический институт (54 ) ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования цифровых величин в аналоговые.

Известен цифроаналоговый преобразователь, содержащий регистр, блок эталонных величин, суммирующее устройство, блок выделения разности, блок управления и ключевые элементы, первые входы которых подключены к выходам блока эталонных величин, выходы ключевых элементов через устройство суммирования соединены сб входом блока выделения разности f1).

Недостатком такого цифроаналогового преобразователя является низкое качество метрологического контроля линейности .выходной характеристики, так как величины погрешности разрядов преобразователя неизвестны.

Цель изобретения - повьхаение качества контроля линейности преобра" зователя. это достигается тем, что в цифроаналоговый преобразователь, содержащий регистр, блок эталонных величин, суммирующее устройство, блок выделения разности, блок управления и ключевые элементы, первые входы которых подключены к выходу блока эталонных величин, выходы ключевых элементов через устройство суммирования соединены со входом блока выделения разности, введены блок развертки кода, блок свертки кода, блок логических элементов и цифровой коммутатор, выход которого соединен со вторыми входами ключевых элементов, первый вход цифрового коммутатора подключен к выходу регистра и к первому входу блока развертки кода, первый выход которого соединен со вторым входом цифрового коммутатора и первым входом блока логических элементов, второй выход блока развертки кодов через блок свертки кода подключен ко второму входу блока логических элементов, выход блока выделения раз20 ности соединен со входом блока управления, выходы которого подключены, соответственно, ко вторым входам блоков развертки кода и свертки кода, к управляющим входам регистра, а также к третьим входам цифрового ком-. мутатора и блока логических элементов.

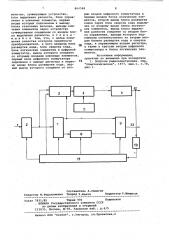

На чертеже представлена функциональная схема цифроаналогового преЗ0 образователя.

864548

Схема содержит вход 1 преобразователя, регистр 2, цифровой коммутатор 3, ключевые элементы 4, блок эталонных величин 5, суммирующее устройство б, блок развертки кода 7, блок свертки кода 8, блок логических элементов 9, блок выделения разности 10, блок управления 11, первый выход 12 цифроаналогового преобразователя, второй выход 13 цифроаналогового преобразователя.

Вход 1 цифроаналогового преобразователя соединен с первым входом регистра 2, выход регистра 2 соединен с первым входом блока развертки кода 7, осуществляющего операцию раз вертки кода и первым информационным 15 входом цифрового коммутатора 3, осуществляющего подключение ко входам ключевых элементов 4 выхода регистра

2 или первого выхода блока развертки кода 7. Выход цифрового коммутатора 20

3 соединен с управляющими входами ключевых элементов 4, информационные входы которых соединены с выходами блока эталонных величин 5. Выходы ключевых элементов 4 соединены со входами суммирующего устройства б, выход которого соединен со входом блока выделения разности 10, выраба,тывающего сигнал несоответствия весов разрядов требуемым значениям.

Первый выход блока развертки кода 7 соединен со вторым информационным входом цифрового коммутатора 3 и первым входом блока логических элементов 9, осуществляющего функцию выделения кода и знака погрешности.

Второй выход блока развертки кода 7 соединен с первым входом блока свертки кода 8, осуществляющего операцию свертки кода. Выход блока 8 соединен со вторым входом блока логических 40 элементов 9. Выход блока б является первым выходом цифроаналогового преобразователя. Выход блока логических элементов 9 является вторым выходом

13 цифроаналогового преобразователя. 45

Первый, второй, третий, четвертЫй и пятый выходы блока управления 11 соединены соответственно со вторым входом регистра 2, с управляющим третьим входом цифрового коммутатора 3, уО вторым входом блока развертки кода

7, вторым входом блока свертки кода

8 и третьим входом. блока логических элементов 9.

Работа цифроаналогового преобразователя происходит в двух режимах: режиме метрологического контроля линейности выходной характеристики и режиме непосред твенного преобразования входного кода в аналоговую ве" личину. 60

В режиме непосредственного преобразования цифрового кода в аналоговую величину участвуют .регистр .2, цифро" вой коммутатор 3, ключевые элементы

4, блок эталонных величин 5, устрой- g5 ство для суммирования эталонных величин б и блок управления 11 ° В режиме метрологического контроля линейности выходной характеристики участвуют все блоки учтройства.

В процессе метрологического контроля линейности выходной характеристики производится определение Вели-. чин отклонений весов разрядов от требуемых значений.

Цифроаналоговый преобразователь использует коды с иррациональными основаниями, к которым относятся р-коды Фибоначчи и коды "золотой" р-пропорции. В кодах золОтой" P-пропорции любое действительное число 9 может быть представлено в виде

КЮ е е=

r e с1Š— двоичная цифра в f-м разряде; с(.р — вес f-го разряда

О, 1, 2, 3,... !

aL — является действительным поР ложительным корнем управления

Х Х+ 1.

Отношение соседних р-чисел Фибоначчи с ростом их номеров также приближается Q . Для р -кодов существует единственйая минимальная форма пред ставлЕния числа D, в которой после каждой единицы следует не менее рнулей. Имеется также множество неминимальных представлений числа Э, в которых не выполняется указанное условие. Связь между весами р -кода определяется рекуррентным соотношением х (1) = x (f.-1)+ х (f р-1). р р „Р

На основании этого соотношения, над разрядами кода выполняютая операции, называемые сверткой и разверткой кода. Свертка заключается в замене нуля в Е-м разряде и единиц в (Ь1)-м и в (f-ð-1) -м разрядах их отрицаниями. Развертка является операцией обратной свертке ° Основная особенность этих операций состоит в том, что они не изменяют величины отображаемого кодом числа,. а изменяют лишь форму представления кода.

Метрологический контроль линейности выходной характеристики начинается с (р+2)-ro разряда при условии> что веса (р+1) младших разрядов преобразователя соответствуют требуемым значениям.

В процессе контроля веса любого

i-го разряда производится уравновешивание scca этого разряда набором весов 1-1 младших разрядов в течение

К циклов. Рассмотрим работу устройства для случая = 1. В первом цикле блок управления 11 производит запись в регистр 2 кодовой комбинации, ко» торая содержит значащую цифру толь864548 ко в проверяемом 1-м разряде. Этот код с выхода регистра 2 подается в блок развертки кода 7 и через цифровой коммутатор 3 на ключевые элементы 4, в результате чего на выходе цифроаналогового преобразователя 12 появляется аналоговый эквива,пент данного кода А . Затем в блоке развертки кода 7 производится развертка исходного кода и передача его через цифровой коммутатор 3 на входы ключевых элементов 4. На выходе суммирующего устройства б появляется аналоговый эквивалент Ag. Блок выделения разности 10 срабатывает при выполнении соотношения:/А, -A>I7 д, где

d — максимально допустимая величина расстройки разряда. Если А -А v Д, блок выделения разности 10 формирует сигнал первого типа, а при А -А„ К вырабатывает сигнал второго типа. При формировании блоком выполнения раз- 20 ности 10 сигнала первого типа блок управления 11 устанавливает в единичное состояние .(i-3)-й разряд блока развертки кода б, а при появлении на выходе блока 10 сигнала второго типа (i-3)-й разряд устанавливается в нулевое состояние, а (i-4)-й в единичное.

Во втором цикле коды, зафиксированные в регистре 2 и блоке свертки кода 7, через цифровой коммутатор 3 подаются на ключевые элементы 4, подавая соответствующие эталонные величины в суммирующее устройство 6;

Если блок выделения разности 10 вырабатывает сигнал первого -типа, то блок управления 11 устанавливает в единичное состояние (i-4)-й разряд блока развертки кода 7.. При появлении на выходе блока выделения разности 10, сигнала второго типа,(i- 3)-й 40 разряд блока развертки кода 7 устанавливается в нулевое состояние, а (i-4)-й разряд — в единичное состояние. Работа устройства в оставшихся (К-2) циклах аналогична работе во 4 втором цикле, причем если блок выделения разности 10 формирует сигнал первого типа, то (i-2-К)-й разряд блока развертки кода 7 устанавливается в единичное состояние. Если блок

10 формирует сигнал второго типа, то (i-1-К)-й разряд блока развертки кода 7 устанавливается в нулевое состояние, а (i-2-К) -й разряд — в единичное состояние.

Процесс уравновешивания i-ro проверяемого разряда продолжается до прекращения срабатывания блока 10 либо до включения в процессе уравновешивания младшего разряда цифроаналогового преобразователя.

Таким образом, по окончании К-го цикла в блойе развертки кода 7 и в регистре 2 зафиксированы кодовые ком-. бинации, аналогОвые эквиваленты.которых удовлетворяют неравенству 6

tA -А (< сР. Разность этих кодовых комбинаций представляет собой код погрешности i-го проверяемого разряда.

Определение знака кода погрешности этого разряда происходит следующим образом.

Если в первом цикле на выходе блока выделения разности 10 выработан сигнал первого типа, то после окончания К-го цикла под воздействием управляющего сигнала из блока управления 11 код, зафиксированный в блоке развертки кода 7, с его первого выхода поступает в блок логических элементов 9. На выходе блока логических элементов 9 по команде блока управления 11 выделен код с (i-3)-ro по 1-й разряды.- В данном случае на выходе

13 преобразователя получается код погрешности 1-го разряда, который имеет положительный знак.

Если в-первом цикле на выходе блока выделения разности 10 был выработан сигнал второго типа, то после окончания К-ro цикла по команде блока управления 11 оо второго выхода блока развертки кода 7 в блок свертки кода 8 заносится инверсный код, младший разряд которого устанавливается в единичное состояние. В блоке свертки кода 8 производится операция свертки кода с 1-ro по (i-3)-й разряды включительно. Под воздействием управляющего сигнала блока управления 11 с выхода блока свертки кода 8 код с (i-3)-го по 1-ый разряды передается через блок логических элементов 9 на выход 13 цифроаналогового преобразователя. Код погрешности i-ro разряда в этом случае отрицательный.

В режиме непосредственного преобразования цифрового кода в аналоговую величину входная цифровая величина подается на вход 1 цифроаналогового преобразователя. С выхода регистра 2 этот код подается через цифровой коммутатор 3 на ключевые элементы 4, подающие соответствующие эталонные величины из блока 5 в устройство суммирования б, с выхода которого снимается аналоговый эквивалент входного кода.

Введение новых блоков и связей обеспечивает повышение качества мет-. рологического контроля линейности выходной характеристики, йреобразователя, заключающееся в автоматизации определения величин и знаков расстройки разрядов цифроаналогового преобразователя, что позволяет сортировать по точности цифроаналоговые преобразователи при изготовлении их в виде больших интегральных схем, а также производить контроль погрешности цифроаналогового преобразователя s процессе эксплуатации.

Формула изобретения

Цифроаналоговый преобразователь, содержащий регистр, блок эталонных

864548

Составитель A.Ñèìàãèí

Редактор М.Недолуженко Техред З.Фанта Корректор Н.Швыдкая

Заказ 7831/85 Тираж 991

ВНИИПИ Государственного комитета СССРпо делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная,4 величин, суммирующее устройство, блок выделения разности, блок управления и ключевые элементы, первые входы которых подключены к выходу блока эталонных величин, выходы ключевых элементов через устройство суммирования соединены со входом блока выделения разности, о т л и ч а— ю шийся тем, что, с целью повышения качества контроля линейности преобразователя, в него введены блок развертки кода, блок свертки кода, блок логических элементов и цифровой коммутатор, выход которого соединен со вторыми входами ключевых элементов, первый вход цифрового коммутатора подключен к выходу регистра и перво- 15 му входу блока развертки кода, первый -выход которого соединен со вторым входом цифрового коммутатора и первым входом блока логических элементов, второй выход блока развертки кодов через блок свертки кода подключен ко второму входу блока логических элементов, выход блока выделения разиости соединен со входом блока управления, выходы которого подключены соответственно ко вторым входам блоков развертки кода и свертки кода, к управляющим входам регистра, а также к третьим входам цифрового коммутатора и блока. логических элементов.

Источники информации, принятые во внимание при экспертизе

1. Вопросы радиоэлектроники. Сер.

"Общетехническая", 1977, вып.1, с.78, рис.1.