Устройство для контроля двоичного счетчика

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Социалнстнческнз

РеспУбЛНК

< >%4580 (61) Дополнительное к авт. сеид-ву

{511М. К .з (22) Заявлено 201279 (21) 2856252/18-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано150981. Бюллетень N9 34

Дата опубликования описания 150981

Н 03 К 21/34

С 01 R 31/28

Государственный комитет

СССР по делам изобретений и открытий

{53) УДК 681.326.5 (088.8) (72) Авторы изобретения

Ф

Л.А, Осадчая, С.И. Петренко и А.И. Сахно (71) Заявитель (54) УСТРОЙСТВО КОНТРОЛЯ ДВОИЧНОГО СЧЕТЧИКА

Изобретение относится к контрольно-измерительной и вычислительной технике и может быть использовано дл>я контроля двоичных счетчиков в процессе их массового производства.

Известны устройства контроля счетчика, содержащие схемы совпадения. элемент задержки, триггеры (1), Недостатком таких устройств является большое время контроля, величина которого определяется разрядностью счетчика.

Наиболее близким по технической сущности к изобретению является уст»ройство контроля счетчика, содержа- тз щее триггеры, элементы И, ИЛИ, элементы задержки и элементарные счетчики (2 j.

Недостатком этого устройства является большое время, затрачиваемое 2О на контроль °

Цель изобретения — уменьшение времени контроля.

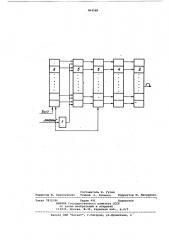

Эта цель достигается тем, что устройство для контроля двоичного счетчика, содержащее элемент задержки, входом соединенный со счетным входом контролируемого счетчика, и элемент И, введены дешифратор, блок вентилей и регистр, причем выходы блока ЗО вентилей соединены с соответствующими установочными входами контролируемого счетчика, управллощие входы блока вентилей соединены с соответствующими выходами разрядов регистра, вторые входы блока вентилей соединены с выходом элемента задержки вход которого соединен с клеммой

"Контроль" устройства и управляющим входом регистра, другой вход которого соединен с входной клеммой устройства, выход каждого разряда контролируемого счетчика соединен с входом каждого разряда дешифратора, выход каждого разряда дешифратора соединен с соответствующим входом элемента И.

На чертеже представлена функциональная схема устройства.

Устройство содержит элемент 1 задержки, элемент И 2, контролируемый счетчик 3, дешифратор 4, блок 5 вентилей, регистр 6.

Устройство работает следующим образом.

В исходном состоянии во всех разрядах счетчика Э, элементах памяти дешифратора 4, регистра 6 устанавливается "0" (цепи установки в "0" на чертеже не показаны). После поступле864580 ния на счетный вход счетчика 3 и управляющий вход регистра 6 первого импульса контроля на выходах счетчика

3 появляется равновесный код 000...

001 с одной единицей в младшем разряде. С выходов счетчика 3 образованный код поступает на входы дешифратора 4. Если на вход дешифратора 4 поступает контролируемый код с одной единицей„ на соответствующей выходной шине (a данном случае на шине, связанной с младшим разрядом дешифратора 4 появляется сигнал, фиксируемый соответствующим элементом памяти.

Одновременно с формированием кода в счетчике 3 по приходу первого импульса контроля происходит формирование установочного кода в регистре 6. Сформированный код 000...001 поступает на входы блока 5 вентилей но на его выходы не проходят, так щ() как по вторым входам блок 5 вентилей закрыт.

Первый импульс контроля поступает также и на вход элемента 1 задержки, на выход которого он поступает до при- 5 хода второго импульса контроля...

Задержанный импульс контроля открывает по вторым входам блок 5 вентилей, и код 000...001, записанный в регистре 6 переписывается в счетчик

3, подтверждая его состояние.

Под действием второго импульса контроля на выходе счетчика 3 вновь появляется равновесный код с одной единицей, но указанная единица уже сдвинута на один разряд в сторону старших разрядов счетчика. Образованный код (000...010.) также является равновесным и дешифрируется дешифратором 4, в результате чего на его втором выходе появляется сигнал, 40 зафиксированный соответствующим этому выходу элементом памяти. Следовательно, после поступления первых двух импульсов контроля два элемента памяти находятся в единичном состоянии. 4

В сдвигающем регистре 6 по описанному алгоритму вторым импульсом контроля устанавливается следующий текущий код 000...011, который вторым импульсом контроля, задержанным элементом 1 задержки, через блок 5 вентилей устанавливается в счетчике 3.

Записанный в счетчик 3 текущий установившийся код 000...011 не дешифрируется дешифратором 4, так как находится в области запрещенных комбинаций.

С приходом третьего импульса контроля, поступающего на счетный вход счетчика 3, происходит перенос единицы в третий разряд и на его выхо- 60 дах формируется равновесный код с

"1" в третьем разряде 00...0100.

На соответствующем выходе дешифратора 4 появляется сигнал, зафиксированный элементом памяти.

Под воздействием следующего j-ro импульса контроля описанный процесс контроля повторяется, т.е. на выходе дешифратора 4 результатов контроля контролируется равновесный код, зафиксированный соответствующим элементом памяти, а в паузе между

j".ì:è (j+1)-м импульсом контроля в счетчике 3 устанавливается код, у которого количество рядом располо женных единиц равно порядковому номеру j-го импульса контроля.

При отсутствии дефектов в контролируемом счетчике к концу контроля все элементы памяти должны находиться в единичном состоянии, в результате чего на выходе элемента И появляется импульс, свидетельствующий о правильной работе счетчика и об окончании его контроля.

Из изложенного следует, что для контроля и-разрядного счетчика с помощью предлагаемого устройства контроля требуется подать на его вход только (n+1) счетных импульсов что существенно уменьшает время контроля счетчика.

Формула изобретения

Устройство контроля двоичного счетчика, содержащее элемент задержки, входом соединенный со счетным входом контролируемого счетчика, и элемент И, о т л и ч а ю щ е е с я тем, что, с целью уменьшения времени контроля, в него введены дешифратор блок вентилей и регистр, причем выходы блока вентилей соединены с соответствующими установочными входами контролируемого счетчика, управляющие входы блока вентилей соединены с соответствующими выходами разрядов регистра, вторые входы блока вентилей соединены с выходом элемента задержки, вход которого соединен с входной клеммой "Контроль" устройства и управляющим входом регистра, другой вход которого соединен с входной клеммой устройства, выход каждого разряда контролируемого счетчика соединен со входом каждого разряда дешифратора, выход каждого разряда дешифратора соединен с coQTBGTствующим входом элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 392502, кл. J 06 F 11/00, 1971.

2. Авторское свидетельство СССР

Р 451198, кл. Н 03 К 21/34, 1975 (прототип).

Составитель В. Гусев

Редактор М. Недолуженко Техред A. Вабинец Корректор Ю. Макаренко

Заказ 7832/86 Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.ПроЕктная, 4