Устройство для фазирования синхронных источников импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ И П!ЛЬСТВУ

Союз Советскик

Социаиистическик

Республик н 864582 (61) Дополнительное к авт. свид-ву— (22) Заявлено 2609.79 (21) 2820221/18-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 150981 Бюллетень М 34

Дата опубликования описания 150981 5> < К„э

Н 03 К 23/00

Государственный комнтет

СССР ло делам изобретений н открытнй (Я) УДК 621 ° 374.

32 (088.8) (72) Автор изобретения

В.A.Òåðåíòüåâ (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ФАЗИРОВАНИЯ СИНХРОННЫХ

ИСТОЧНИКОВ ИМПУЛЬСОВ

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в устройствах формирования импульсных последователь-5 ностей.

Известно устройство, обеспечивающее возможность фазировки счетчиков, содержащее два синхронных источника импульсов, входы которых объединены, и блок фазировки, выполненный на счетном триггере, инверторе н двух логических элементах (1).

Недостатком его является высокое быстродействие.

Известно также устройство фазиров:— ки синхронных источников импульсов, содержащее генератор импульсов, выход которого соединей со входами деталей частоты, двухвходовые логичес- 20 кие элементы И и ИЛИ и счетчик, причем выходы деталей частоты соединены со входами элемента И, выход которого соединен со входом элемента ИЛИ, другой вход которого соединен с выходом 25 последнего разряда счетчика, счетный вход которого соединен с выходом одного из делителей частоты, вход сброса которого соединен с выходом последнего разряда счетчика. 30

При нормальной синхронной работе делителей частоты это устройство обеспечивает фазировку делителя частоты, имеющего меньший коэффициент деления от делителя частоты, имеющего больший коэффициент деления, а при расфазировке делителей частоты осуществляется фазирование делителя, имеющего меньший коэффициент деления с помощью дополнительного счетчика импульсов, сигнал с выхода которого выдается после поступления на счетчик определенного числа импульсов от делителя частоты, имеющего меньший коэффициент деления 2).

Однако это устройство не применимо для фазировки синхронных делителей частоты с произвольно изменяющимися в процессе работы кратными между собой коэффициентами деления, так как требуемое число разрядов счетчика зависит от соотношения частот выходных сигналов делителей частоты, а в тех случаях, когда коэффициент деления делителя частоты, связанного со счетчиком, оказывается больше, чем коэффициент деления делителя не связанного со счетчиком,, время входа в синхронизм значительйо возрастает.

864582

Целью изобретения является расширение функциональных возможностей за счет обеспечения воэможности произвольного изменения коэффициентов деления синхронных источников импульсов.

Для достижения этой цели в устройство, содержащее делители частоты, счетные входы которых объединены, и два двухвходовых логических элемента, введены два R-S-триггера, S-входы которых соединены с выходами делителей частоты, а выходы — co входами перво-< го двухвходового логического элемента

3--к-триггер первый вход которого соединен с выходом первого двухходового логического элемента, счетный вход со счетными входами делителей частоты, третий вход и прямой выход триггера объединены, а счетный вход и инверсный выход соединены со входами второго двухвходового логического 20 элемента, выход которого соединен со входами сброса делителей частоты и R-входами R-S-триггеров.

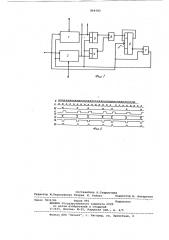

На фиг. 1 представлена функциональная схема устройства, на фиг. 2 — вре-25 менные диаграммы его работы.

Устройство фазировки синхронных источников импульсов содержит делители частоты 1 и 2 с переменными коэффиц>;ентами деления, R-S-триггеры 3 и

4, 3 -К-триггера, и двухвходовые логическйе элементы 6 и 7.

Ua счетные входы делителей 1 и 2 поступает сетка импульсов тактовой частоты от внешнего устройства. Делители 1 и 2 имеют переменные коэффициенты деления, значения которых задаются сигналами управления, поступающими от внешнего устройства.

С выходов делителей 1 и 2 частоты сигналы поступают на входы триггеров 40

3 и 4. Если делители 1 и 2 работают синхронно, то при прохождении более низкочастотного сигнала с выхода одного из делителей одновременно выда- ется импульс с выхода другого делителя и на входы логического элемента 6( поступают низкие уровни сигналов, а на S âõoä Y-К-триггера 5 поступает положительный импульс, устанавливающий триггер в состояние логической единицы. Сбрасывается триггер 5 в нулевое состояние по положительному фронту импульса, поступающего на его тактирующий вход.С выхода логического элемента 7 выдается импульс сброса в нулевое состояние делителей 1 и 2, а также триггеров 3 и 4. Длительность импульсов сброса равен интервалу между положительными импульсами входной сетки (fg ), поступающей на входы делителей частоты. Если в работе одного из делителей произошел сбой, то импульс формируется только после того, как оба триггера 3 и 4 установятся в единичное состояние импульсами с выходов делителей 1 и 2. Импульс сброса устанавливает оба делителя одновременно в нулевое состояние и их синхронная работа восстанавливается.

На временных диаграммах фиг. 2 показаны сигнал 8 на входах делителей 1, 2, сигнал 9 на выходе делителя 1, сигнал 10 на выходе делителя

2; сигнал 11 на выходе триггера 3; сигнал 12 на выходе триггера 4;сигнал

13 на выходе логического элемента 6; сигнал 14 на инверсном выходе триггера 5, сигнал 15 на выходе логического элемента 7 (сброс).

Использование в устройстве фазиро вания двух R-S-триггеров и J-K-триггера позволяет обеспечить возможность произвольного изменения кратных между собой коэффициентсв деления синхронно работающих делителей частоты.

Формула изобретения

Устройство для фазирования синхронных источников импульсов, содержащее делители частоты, счетные входы которых объединены и два двухвходовых логических элемента, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностей, за счет обеспечения возможности произвольного изменения коэффициентов деления, в него введены два В-S-триггера, S-входы которых соединены с выходами делителей частоты, а выходы со входами первого двухвходового логического элемента, 3 -L -триггера, первый вход которого соединен с выходом первого двухвходового логического элемента, второй вход со счетными входами делителей частоты, третий вход и прямой выход объединены, а инверсный выход — с первым входом второго двухвходового логического элемента, второй вход которого соединен со вторым входом.1-К-триггера, а выход — со входами сброса делителей частоты и R-входами R-5-триггеров.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

Р 539379,кл. Н 03 К 21/32, 1972.

2. Авторское свидетельство СССР

9 586568,кл. Н 03 К 23/00. 1973.

864582

0

1Д

1/ с

Ц и а

Фиг. Я

Составитель A.Ñòàðîñòèíà

Редактор М.Недолуженко Техред М. PeAsec Корректор JO. Макаренко

Заказ 7832/86 Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва- Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород. Ул. Проектная, 4