Спектроанализатор

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

В. А. Грачев н А. С. Зверев (7! ) Заявитель (54) СПЕКТРОАНАЛИЗАТОР

Изобретение относится к электроизмерительной технике и может быть использовано прн спектральном анализе электрических сигналов.

Наиболее близким по технической сущности к предлагаемому является анализа5 тор, содержащий параллельно включенные каналы обработки, элементы памяти в виде матрицы с ячейками, электроннолучевую трубку с модулятором яркости и бло-. то ком развертки, счетчик н блок управленя (Q.

Недостатком известного устройства является его сложность, что снижает надежность работы.

3%

Бель изобретения - повышение надежности устройства.

Эта цель достигается тем, что в спектроанализатор, содержащий М параллельно включенных каналов обработки, каждый о из которых состоит нз последовательно соединенных фильтра, детектора и интегратора, а также блок управления, подключенный ко входу счетчика, один выход которого через модулятор яркости, а другойчерез генератор развертки подключен ко входам электроннолучевой трубки, введены коммутатор, аналого-пнфровой преобразователь, мультиплексор, буферный регистр, оперативное запоминающее устройство, блок сравнения кодов, второй счетчик, цифроаналоговый преобразователь и формирователь адреса и команд, причем выходы интеграторов всех каналов обработки подключены ко входам коммутатора, управля» ющий вход которого соединен со вторым выходом блока управления, а выход коммутатора подключен через аналого-цифро вой преобразователь «о входу мультиплексора, второй вход которого подключен к выходу буферного регистра, соединенного также со входом блока сравнения кодов, выход которого через второй счетчик подключен. ко входу блока управления, выход мультиплексора соединен со входом оперативного запоминающего устройства, второй вход которого подключен через форми рователь адреса и команд к первому вы866494 4 декс — номер ячейки данного канада, втоа рой индекс - номер канала), записанный в 1-л -ом кадре. Затем происходит запись б- в ОЗУ 8 через мультиплексор 7 по адресуа,,„ текущей информации с выхода AIIII

6. В следующий момент времени из ОЗУ

8 считывается код U ° ", который посту>11 пает на блок 10 сравйения, где он сравнивается с кодом LI> > храняшемся в алл регистре 9. Результат сравнения поступает на управление выходами счетчика 11, ф- который определяет моменты времени перезаписи информации из ячейки с адресом т а,,1 в ячейку с адресом cl °, e (g = 1, 2 ... n ) со сравнением или без сравнения. ок Запись беэ сравнения в 1 -ую ячейку па-. а мяти каждого канала производится в моменты времени, в которые состояние счетчика 11 может быть представлено как

20 q4 ". Пр эм перезапись в ОЗУ 8 б з сравнения кода 0" " с регистра 9 через с5 1л м мультиплексор по адресу а ал происходит в кадрах 1 = 2, 4, 6, 8 ..., т.е. по

;четным кадрам. Запись со сравнением в

j -ую ячейку памяти каждого канала про

25 изводится в моменты времени, в которые состояние счетчика 11 может быть представлено как,й .„, При этом в кадрах

f-1 о- л = 1„3„5, ...„т.е. о нечетным кадрам, перезапись кода U по адрест

30 ам

СИл происходит в том случае, когда U "- 1 > d„g я О, „. B противном случае по адресус л сохранится старое значение U, В слеа 1 дующий момент времени произойдет запись в регистр 9 кода О ", Далее иэ ем З5 ОЗК 8 считывается код О " а 31

При этом запись беэ сравнения кода

1-л о- а, по agpecy Ой„происходит в кадрах = 4, 8, 12, 16 ..., в запись со сравнением - в кадрах 1 = 2, 6, 10" °

Далее, в регистр 9 перепишется значение.

1-л

О, и т.д. по и -ой ячейки памяти пер 1 ного канала. Аналогичная обработка происходит для каждого последующего канва ла в 1 -aM кадре. Таким образом, мак

45 симальный сигнал в каждом канале перемещается от кадра к кадру из первой ячейки памяти в и -ую, причем в каж дой последующей ячейке сигнал хранится в 2 раза больше времени, чем в предыду50 щей, а максимальное время хранения сиги . нала в ячейках памяти

1 „=т 2" ходу блока управления, а выход подключен одновременно ко второму входу блок сравнения кодов, ко входу буферного регистра и ко входу цифроаналогового прео разователя, выход которого соединен с третьим входом электроннолучевой трубки

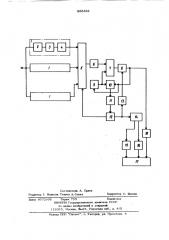

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит 14 параллельно включенных каналов 1 обработки, состоящих иэ фильтра 2, детектора 3 и интегратора 4, коммутатор 5, аналого-ци ровой преобразователь (А11П) 6, мульти плексор 7, оперативное запоминающее ус ройст ю (ОЗУ) 8, буферный регистр 9 блок 10 сравнения кодов, счетчик ll, бл

12 управления, формирователь 13 адрес и команд, счетчик 14, модулятор 15 яркости, генератор 16 развертки, электрон нолучевую трубку (ЭЛТ) 17 и цифроаналоговый преобразователь (ЦАП) 18.

Спектроанализатор работает следующи образом.

Сигнал, подлежащий анализу, поступа ет на входы каналов 1, где он фильтруе ся, детектируется и интегрируется, С вь ходов каналов 1 сигналы поступают на коммутатор 5, в котором с помощью блока 12 управления производи гся послед вательный опрос всех каналов. Опрос всех каналов 1 и считывание всей информации на ЭЛТ 17 производится-эа врем

Т, определяемое, исходя из необходимости поддержания на экране немигающего иэображения, и выбирается. не больше

20-30 мс. (В дальнейшем период Т буд называть кадром работы спектроанализа

pa). С выхода коммутатора 5 сигналы п ступают на вход АЦП 6, преобразующего напряжение с выхода коммутатора 5 в цифровой код. Вся дальнейшая обработка связанная с повышением временного разрешения сигнала, производится в цифрово виде. В ОЗУ 8 каждому каналу отводит ячеек памяти, соответствующих д гр дациям яркости при выводе информации каждого канала на ЭЛТ 17. Адрес при записи и считывании кодов на ОЗУ 8, а также команды управления ОЗУ 8 форми руются формирователем .13, работу ко рого определяет блок 12, осущ.ствпш щи скнхронный опрос всех каналов. Запись продвижение кодовой информации по яче кам памяти ОЗУ 8 в каждом канале прсьиэводится следующим образом. После подключения в 1 -ом кадре (1 = 1, 2, 3 ...) первого канала происхор т считывание иэ ОЗУ 8 на регистр 9 кода V 1 (где

И1л

0(м - адРес Ячейки ОЗУ 8, пеРвый инЭто время .полностью определяет время существованиия изображения сигнала на экране ЭЛТ 17. Изменения времени существования сигнала на экране и характера изображения можно добиться изменением

866404 6 выполнение устройства и повышает надеж ность его работы.

5 количества ступеней и коэффициента пересчета счетчика 1 1.

В каждом кадре в паузах между приемом, обработкой, записью и перезаписью сигналов всех каналов в ОЗУ 8 по коман- дам с формирователя 13 происходит последовательное считывание всей записанной в ОЗУ 8 информации на ЦАП 18, и после преобразования на сигнальный вход

ЭЛТ 17. Одновременно блок 12 формиру- 10 ет ю и импульсов. Импульсы с блока 12 поступают на формирователь 1Э, в котором формируется адрес при считывании информации иэ ОЗУ 8, команда управления считыванием из ОЗУ 8 и импульсы íà 15 счетчик 14. Счетчик 14 . подсчитывает номер ячейки памяги в каждом канале. Код с выхода счетчика 14 управляет работой модулятора 15 яркости, выполненного ввиде преобразователя код-напряжение, при- 2р чем сигнал, записанный в первую ячейку памяти, высвечивается с наибольшей яркостью, во вторую ячейку - с меньшей яркостью и т.д.

Сигнал одного канала выводится в од- 2s но место экрана в виде штрихов, наложенных один на другой, с амплитудой, соответствующей величине сигнала, и яркостью, соответствующей номеру ячейки памяти данного канала. Вследствие этого максимальный сигнал в каждом канале при отображении скачкообразно во времени уменьшает свою яркость. При достаточном наблюдается имитация эффекта после свечения сигнала на экране ЭЛТ. Один раэ эа д импульсов с блока 12 в счетчике 14 происходит переполнение. Импульс переполнения запускает генератор 16, который перемещает луч ЭЛТ 17. Генератор

16 представляет собой генератор ступенМ 9Tl чатого напряжения с числом значений -, где Г - число строк изображения. В случае развертки по одной строке чисЛо ступеней равно rn.

Таким образом, работа предлагаемого устройства практически не зависит от N и л так как в нем вся обработка, свя1 занная с повышением временного разре« шения сигнала, производится последовательно для всех каналов. Это упрощает

Формула изобретения

Спектроанализатор, содержащий И па раллельно включенных каналов обработки, каждый иэ которых состоит иэ последовательно соединенных фильтра, детектора и интегратора, а также блок управления, подключенный ко входу счетчика, один выход которого через модулятор яркости, а другой - через генератор развертки подключены ко входам электроннолучевой труб»ки,о тли ч&юшичсятемрчто,с целью повышения надежности устройст» ва, в него дополнительно введены комму татор, анаиого-цифровой преобразователь, мультиплексор, буферный регистр, оперативное запоминающее устройство, блок сравнения кодов, второй счетчик, цифроаналоговый преобразователь и формирова» тель адреСа и команд, причем выходы интеграторов всех каналов обработки подключены ко входам коммутатора, управ ляющий вход которого соединен со вторым выходом блока управле"ия, à выход коммутатора подключен через аналого-цифро вой преобразователь ко входу мультиплек сора, второй вход которого подключен к выходу буферного регистра, соединенного также со входом блока сравнения кодов, выход которого через второй счетчик подключен ко входу блока управления, выход мультиплексора соединен со входом опера тивного запоминающего устройства, вто рой вход которого подключен через формы рователь адреса и команд к первому вы» ходу блока управления, а выход подключен одновременно ко второму входу блока срав иения кодов, ко входу буферного регбист ра и ко входу цифроаналогового преобра эователя, выход которого соединен с третьим входом электроннолучевой трубки.

Источники информации, принятые во внимание при экспертизе;

1. Авторское свидетельство СССР

% 600466, кл. Ci Ol R 23/00, 1976.

В68494

Составитель А. Орлов

Редактор Г. Волкова Текред А.Савка

Корректор С. Шомак

Филиал ППП Патент, r, Ужгород, ул. Проектная, 4

Закаэ 8072/68 Тираж 735 Подписное

ИНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж 15,, Раушская наб„д. 4/5