Программируемый высоковольтный стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублим

|а866551

/ (51)M. Кл.

G 05 F 1/56 (53) УЛ К 621.316.722. .1 (088.8) (61) Дополнительное к авт. свмд-ву (22) Заявлено 06.№79 (21) 2790991/24-07 с присоединением заявки М!

Гесударствакаый камитет

СССР аа делам кзабратенкй и аткрытяя (23) П рмормтет—, Опубликовано 23.09.81. Бюллетень М 35

Дата опубликования описания 23.09.81

Г р (.

| :,- -я .:.„: .,: |г

° р

I (72) Авторы изобретения

О. А. Прудников и С. Ф. Полов (71) Заявитель (54) ПРОГРАММИРУЕМЫЙ ВЫСОКОВОЛЬТНЫЙ СТАБИЛИЗАТОР

ПОСТОЯННОГО НАПРЯЖЕНИЯ

Изобретение относится к электротехнике, в частности к стабилизированным источникам питания и может быть использовано в приборах для проверки цифровых вольтметров, а также в устройствах электропитания рациоаппаратуры.

Известны высоковольтные стабилизаторы напряжения на транзисторах, содержащие сравнивающий узел, усилитель ошибки в цепи обратной связи и регулирующий элемент из последовательно. включенных транзисторов.

Для обеспечения линейной работы всех транзисторов регулирующего элемента и равно-! мерного распределения на них входного напряжения, базы транзисторов подключены к делителю напряжения, включейному параллельно регулирук щего элементу. Делитель рассчитывается таким образом, чтобы в режиме минимального входного и максимального выходного напряжения стабилизатора ток, протекающий. через него, был намного больше максимального тока базы последовательно включенных регупирующих транзисторов (1). . Недостатками этих стабилизаторов являются низкий коэффициент полезного действия из-за работы последовательно включенных транэисто|ров регулирующего элемента в линейном режиме и большой мощности, рассеиваемой в делителе питания базовых цепей регулирующих транзисторов; низкая надежность мз-за большего количества транзисторов в регулирующем элементе и неравномерности распределения напряжения между ними при изменении в широком диапазоне токов нагрузки и выходного напряжения стабилизатора; узкий диапазон токов нагрузки из-за шунтирования регулирующего элемента целителем.

Известен стабилизатор напряжения на транзисторах, который содержит сравнивающий узел, усилитель ошибки в цепи обратной связи, регулирующий элемент из трех последовательно включенных транзисторов и дополнительный источник питания базовых цепей регулирующих транзисторов (2).

В этом стабилизаторе токи баэ регулирующих транзисторов протекают каждый по своей цепи и не влияют друг на друга, что позволяет более точно распределить.входное напряжение на регулирующих транзисторах. Кроме.

866551

45 того, подобная схема позволяет несколько уве- личить КПД стабилизатора при уменьшении входного напряжения, так как регулирующие транзисторы, начиная с первого от выпрямителя, будут по очереди входить в режим насыщения. При изменении выходного напряжения от нуля до максимального значения в широком диапазоне токов нагрузки коэффициент полезного действия стабилизатора будет низок из-за того, что величина напряжения дополнительного источника фактически будет равна величине основного источника и вся мощность, при минимальном выходном напряжении стабилизатора, будет рассеиваться на регулирующих транзисторах или стабилитронах; включенных параллельно им.

Наиболее близким по технической сущности к предлагаембму является программируемый высоковольтный стабилизатор постоянного напряжения, содержащий регулирующий транзистор, эмиттер которого подключен к одной из выходных клемм стабилизатора, и цепь обратной связи, состоящую из сравнивающего узла и усилителя сигнала рассогласования, причем вход сравнивающего узла подключен к выходным выводам стабилизатора, а выход - ко входу усилителя сигнала рассогласования, выходом соединенного с базой регулирующего транзистора (3).

Недостатками известного стабилизатора явля30 ются низкое быстродействие при переходе от максимального выходного напряжения стабилизатора к нулевому из-за разряда фильтрующей емкости через транзисторный регулирующий элемент, а точнее через защитный стабилитрон, обязательно включенный параллельно транзистору, и нагрузку. Таким образом, на нагрузке . будет присутствовать излишнее напряжение в течение времени разряда фильтрующего конденсатора через сопротивление нагрузки. При минимальном напряжении на выходе стабили- 40 затора, ток нагрузки от высоковольтного выпрямителя проходит через стабилитроньг и вся избыточная мощность рассеивается на всех стабилитронах и КПД устройства получается сравнительно низким.

Цель изобретения - увеличение быстродействия и повышение КПД программируемого высоковольтного стабилизатора постоянного напряжения.

Поставленная цель достигается тем, что в gp программируемый высоковольтный стабилизатор постоянного напряжения введено N послео довательно соединенных управляемых источииков напряжения, включенных между второй выходной клеммой стабилюатора и одним из выводов для подключения источника входного питающего напряжения, а другой вывод для подключения этого же источника соединен с коллектором регулирующего транзистора, при этом каждый из указанных управляемых источников напряжения состоит из параллельно включенных резистора, диода, включенного в прямом с током нагрузки направлении, и выпрямителя с последовательно соединенным транзистором, базой, подключенным через вновь введенный пороговый элемент к эмиттеру предыдущего транзистора, начиная с регулирующего.

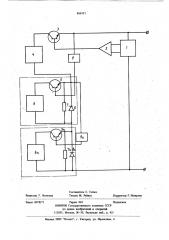

На чертеже представлена функциональная схема программируемого высоковольтного стабилизатора постоянного напряжения.

Стабилизатор содержит сравнивающий узел

1, состоящий из программируемого источника опорного напряжения и делителя напряжения.

Сравнивающий узел включен между выходными клеммами стабилизатора. Усилитель сигнала рассогласования 2 в цепи обратной связи, вход которого подключен к сравнивающему узлу 1, а выход - к базе регулирующего транзистора

3, эмиттер которого соединен с одной из выходных клемм стабилизатора. К коллектору регулирующего транзистора 3 подключен вывод для подключения источника 4 входного питающего напряжения, а между вторым его выводом и другой выходной клеммрй стабилюатора включено N последовательно соединенных управляемых источников напряжения, каждый ю которых состоит из параллельно включенных транзистора 5 ... 5 с последовательно включенным выпрямителем 6...6 4, резистора

7...7>, и диода 8...8N, включенного в прямом с током нагрузки направлении, а базы транзисторов 5...5ы через пороговый элемент 9...9 ч соединены с эмиттером предыдущего транзистора, начиная от регулирующего транзистора.

Стабилизатор работает следующим образом.

При увеличении сигнала с перестраиваемого источника опорного напряжения сравнивающего узла 1, усиливаемого усилителем 2, регулирую-, щий транзистор 3 открывается и выходное напряжение стабилизатора увеличивается. Ток нагрузки от положительного полюса источника

4 через регулирующий транзистор 3, нагрузку, подключаемую к выходным клеммам стабилюатора и диоды 8...81 замыкается на отрицательный полюс источника 4. При этом все транзисторы

5...5 закрыты. По мере открывания регулирующего транзистора 3 увеличивается напряжение на пороговом элементе 9. При достижении порога открытия, транзистор 5 открывается и к выходному напряжению стабилизатора добавляется напряжение от выпрямителя 6, при этом регулирующий транзистор 3 может быть полностью открыт, а регулировку и стабилизацию выходного напряжения осуществляет транзис тор 5. Таким образом, при регулировании уровня сигнала с перестраиваемого источника

8665 опорного напряжения меняется выходное напряжение стабилизатора путем последовательного подключения или отключения выпрямителей

6...6N, через транзисторы 5...51ч, один из которых находится в линейном регулирующем режиме, предыдущий в открытом состоянии, а последующий в закрытом.: Наибольшую мощность рассеивает только один нз всех К транзисторов, так как мощности на открытых и закрытых транзисторах незначительны, что позволяет увеличить КПД высоковольтного источника. Быстродействие подключения источников определяется временем включения и отключения транзисторов 5...5N. Резисторы 7...7ч служат для обеспечения активного режима транзисторов 5...5Ь1, что обеспечивает их работоспособность прн нулевой нагрузке.

Предлагаемая схема последовательного подключения нескольких источников напряжения выгодно отличает программируемый высоковольтный стабилизатор постоянного напряжения от известного резким увеличением быстродействия высоковольтного стабилизатора и повышением его КПД.

Перечисленные выше преимущества позво ляют расширить сферу применения высоковольтного стабилизатора и использовать его не только для программируемых приборов, но и для построения высоковольтных стабилизаторов с использованием низковольтных элемензо тов в различных областях электро- и радиотехники.

Формула изобретения

Программируемый высоковольтный стабили- З5 затор постоянного напряжения, содержащий реSl 6 гулирующий транзистор, эмиттер которого под- . ключен к одной нз выходных клемм стабилизатора, и цепь обратной связи, состоящую из сравнивающего узла и усилителя сигнала рассогласования, причем вход сравнивающего узла подключен к выходным выводам стабилизатора, а выход - ко входу усилителя сигнала рассогласования, выходом соединенного с базой регулирующего транзистора,.о т л и ч а юшийся тем, что, с целью повышения быстродействия и КПД стабилизатора, в него введено N последовательно соединенных управляемых источников напряжения, включенных между второй выходной клеммой стабилизатора и одним из выводов для подключения источника входного питающего напряжения, а другой вывод для подключения этого же источника соединен с коллектором регулирующего транзистора, при этом каждйй иэ указанных управляемых источников напряжения состоит из параллельно включенных резистора, диода, включенчого в прямом с током нагрузки направлении, и выпрямителя с последовательно соединенным транзистором, базой, подключенным через вновь введенный пороговый элемент к эмиттеру предыдущего транзистора, начиная с регулирующего.

Источники информации, принятые во внимание при экспертизе

1. Источники электропитания на полупроводниковых приборах. Проектирование и расчет. Под ред. Додика С. Д. и Гальперина Е. И.

М., "Сов.радио", 1969, с. 347.

2. "Обмен опытом в радиопромышленности", 1976, Н 1, с. 50.

3. Авторское свидетельство СССР Р 610090, кл. G 05 F 1/56, 1978, 866551

Составитель С. Ситко

Техред М. Рейвес, Корректор Г Назарова

Редактор Г. Волкова

Заказ 8078/71

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Тираж 943 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5