Импульсная линия задержки

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

О П И С А.Н И Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВКДЕТЕЛЬСТВУ (866724 (6! ) Дополнительное к авт, саид-ву (22) Заявлено 29,1 279 (2! ) 28б0278/18-21 с присоединением заявки Ме (23) Приоритет (51)М. Кл.

Н 03 К 5/13

ГоауднрстненныИ кемнтет

СССР до делам наобретеннй н отнрытнй

Опубликовано 230981, Бюллетень 1тЪ 35

Дата опубликования описания 250981 (53,! УДК 621. .318.5(088.8) (72) Авторы изобретения

В.А. Сагайдачный, М.К. Халикеев и К. (7!) Заявитель (54) ИМПУЛЬСНАЯ ЛИНИЯ ЗАДЕРЖКИ

Изобретейие относится к электронной импульсной технике,. а именно к дискретным устройствам задержки импульсных сигналов, и может найти применение в вычислительной технике, в средствах автоматики и связи.

Известны устройства задержки, содержащие реактивный элемент(КС- илн

LC-цепь), выходное фиксирующее устройство (1 ). то

Однако известные устройства имеют . недостаточную стабильность и значительное потребление энергии.

Наиболее близкими по технической сущности к предлагаемому изобретению т5 являются известные импульсные линии задержки,ячейки которых выполнены на основе времязадающей RC-цепи и последующего транзисторного ключа в качестве выходного устройства (2 ).

Однако известные импульсные линии задержки имеют такие недостатки, как максимальное потребление тока от источника в исходном состоянии из-за насыщенного режима всех транзисторов

1линии задержки и нестабильная работа

S линии при времени задержки T>ää ячейки, соизмеримом с временем переходных процессов.

Цель предлагаемого изобретения— увеличение длительности задержки ячейки при сохранении уровней ее нестабильности времени задержки и энергопотребления.

Указанная цель достигается тем, что в известной импульсной линии задержки, состоящей из входного каскада и однотипных задерживающих ячеек, соединенных последовательно и содержащих ключевой каскад, состоящий из транзистора, нагрузочного резистора и резистора в цепи смещения входа транзистора по питанию, и накопительного конденсатора, одна обкладка которого подсоединена к входу транзистора ключевого каскада, в ячейку введен каскад повторителя напряжения, состоящий из нагрузочного ре86672

20

35

45

Формула изобретения знстора и транзистора, вход которо го подсоединен между выходом транзистора и нагрузочного резистора ключевого каскада предыдущей ячейки, а между выходом транзистора и нагрузочным резистором повторителя подсоединена другая обкладка конденсатора.

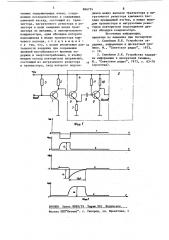

На фиг. 1 представлена принципиальная электрическая схема однотиповой ячейки импульсной линии задержки; на фиг. 2 " экспериментальные временные диаграммы, снятые с экрана двухлучевого осциллографа.

Импульсная линия задержки состоит из входного каскада, содержащего транзистор 1, нагрузочный. резистор

2 н резистор 3 в цепи смещения базы транзистора I по питанию +Е, несколь ких одн .типных задерживающих ячеек

4 и 5, каждая из которых состоит из каскада повторителя напряжения, содержащего транзистор 6 и нагрузочный резистор 7, накопительного конденсатора 8 и ключевого каскада, содержащего транзистор 9, нагрузочный резистор IO и резистор 11 в цепи смещения базы транзистора 9 по питанию. Линия задержки выполнена на биполярных тран эисторах и-р-и структуры,,так как в силу известных технологических особенностей транзисторы современных интегральных схем имеют, как правило, структуру и-р-и типа.

На фиг. 2 график l изображает временную диаграмму изменения напряжения U@(t) входного импульса, график 2 — временную диаграмму изменения напряжения 0 „(й) на выходе транзистора 1, график 3 — временную диаграмму изменения напряжения 0 (t) на базе транзистора 9, график 4 - временную диаграмму изменения напряже" ния Ок9(t) на выходе транзистора 9.

В исходном состоянии транзисторы 1 и 9 насыщены (открыты) за счет токов, протекающих в резисторах 3 и ll, тран зистор 6 закрыт н конденсатор 8 разряжен. Входной импульс отрицательной полярности закрывает транзистор 1, в результате чего на вход транзистора 6 поступает импульс положительной полярности с амплитудой Е . Транзистор 6 открывается и начинается заряд конденсатора 8 до напряжения Ем через вход насыщенного транзистора 9. При этом транзистор 9 еще больше насыщается, но состояние последующих кас кадов линии не изменяется. По окончании входного импульса транзистор 1 возвращается в открытое состояние, а транзистор 6 — в закрытое состояние и конденсатор 8 оказывается приложенным правой обкладкой, имеющей отрицательный потенциал, к входу транзистора 9. В результате этого транзистор 9 закрывается и начинается разряд конденсатора 8 через резисторы 7 и 11.

В течение времени разряда конденсатора 8 транзистор 9 закрыт, что приводит к открыванию каскада повторителя напряжения и к заряду конденсатора следующей ячейки 5 ° Как только напряжение 0, (график 3) станет положительным, открывается транзистор 9 и заряженный конденсатор ячейки 5 закроет каскад ключа этой ячейки. Далее процессы повторяются. В результате передний фронт входного импульса оказывается задержанным в каждой ячейке на время разряда конденсатора.

Введение в каждую времязадающую ячейку нового для ее схемы каскада повторителя напряжения подключение одной (левой на фиг. I) иэ обкладок конденсатора к выходу повторителя выгодно отличает предлагаемую импульоную линию задержки от известного уст-. ройства, так как увеличивает время задержки каждой ячейки Tyjyg Сц(йу +

+ Й„„ ) эа счет значения резистора Й который не повышает существующие уровни нестабильности времени задержки (значения С® и Й„4 не увеличиваются) и энергопотребления (каскад повторителя в исходном состоянии закрыт). Кроме того, стало возможным плавное регулирование времени задержки ячейки при использовании переменного резистора 7.

Технико-экономическая эффективность данного устройства заключается в том, что при фиксации длительности задержки всей линии потребность в количестве ячеек уменьшается не менее чем в 2 раза, что соответственно приводит к уменьшению примерно в 2 раза энергопотребления. При этом общее количество транзисторов, резисторов и конденсаторов в линии остается неизменным, а значит,не изменится и стоимость предлагаемого устройства по сравнению с известным.

Импульсная линия задержки, со,стоящая из входного каскада и одно86 типных задерживающих ячеек, соединенных последовательно и содержащих ключевой каскад, состоящий из тран- зистора, нагрузочного резистора и резистора в цепи смещения входа транзистора по питанию, и накопительного конденсатора, одна обкладка которого подсодинена к входу транзистора ключевого каскада, о т л и ч а ю щ а я с я тем, что, с целью увеличения длительности задержки при сохранении уровней нестабильности времени задержки и энергопотребления, в ячейку введен каскад повторителя напряжения, состоящий из нагрузочного резистора и транзистора, вход которого подсое6724 б динен между выходом транзистора и на" груэочного резистора ключевого кас.када предыдущей ячейки, а между выхо,дом транзистора и нагрузочным реэисS тором повторителя подсоединена другая обкладка конденсатора.

Источники информации, принятые во внимание при экспертизе

I. Самойлов Л. К. Устройства задержки, информации в дискретной технике. M., "Советское радио", 1973, с. 10.

2. Самойлов Л.К. Устройства задержки информации в дискретной технике, М., "Советское радио", 1973, с. 63-70 (прототип).

ВНИИПИ Заказ 8099/79. Тираж 991 Подписное

Филиал ППП"Патент". г. Ужгород, ул. Проектная, 4