Устройство приема многократно передаваемых комбинаций

Иллюстрации

Показать всеРеферат

Союз Сааетскнк

Соцнайнстнчесинк

Ресттфбанк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ВТИЛЬСТВУ (ii}866763 (61) Дополнительное к авт. свид-ву (22) Заявлено 1412.79 (21) 2850618/18-09 (51)М. Клз с присоединением заявки Йо

Н 04 L 1/10

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 230981. Бюллетень 89 35

Дата опубликования описания 230981 (53) УДК 621. 394. .625.33(088.8) (72) Авторы изобретения

Ю.В.. Сулимов, B.È. Котов и Ф.Г. Фоми ев

Н; (71) Заявитель (54) УСТРОЙСТВО ПРИЕМА МНОГОКРАТНО ПЕРЕДАВАЕМЫХ

КОМВИНАЦИЙ

Изобретение относится к технике связи и может быть использовано в аппаратуре передачи данных при разработке устройств, обеспечивающих помехоустойчивый прием многократно повторяемой информации.

Известно устройство приема многократно передаваемых комбинаций, содержащее последовательно соединенные блок преобразования и блок мажоритарной выборки, два элемента И, два регистра сдвига, первый блок памяти, элемент ИЛИ и сумматор f1).

Однако в известном устройстве недостаточная помехозащищенность. ель изобретения — повышение помехоз ищенности.

Для этого в устройство приема многократно передаваемых комбинаций, содержащее последовательно соединенные блок преобразования и блок мажоритарной выборки, два элемента И,два регистра сдвига, первый, блок памяти, элемент ИЛИ и сумматор, введены декодирующий блок, блок определения достоверности символов, последовательно соединенные делитель, второй блок памяти и блок сравнения, а так" З же блок управления и запоминающий блок, причем вход блока преобразования соединен с входом декодирующего блока, первый выкод которого соединен с одним входом элемента ИЛИ,другой вход которбго соединен через первый элемент И с вторым выходом декодирующего блока, выходы блока преобразования соединены с входами блока определения достоверности символов, выход которого через последовательно соединенные первый регистр сдвига и второй элемент И соединен с одним входом сумматора, другой вход которого через второй регистр сдвига соединен с выходом элемента ИЛИ, соедин нениым с первым входом делителя,второй вход которого соединен с одним выходом блока управления, соединенным с входом запоминающего блока, вы-. ходы которого соединены с входами блока сравнения, выход которого соединен с другим входом второго элемента И, выход которого соединен с первым входом первого блока памяти, второй и третий входы которого соединены соответственно с выходом делителя и другим выходом блока управления, выход блока мажоритарной выборки соединен с другим входом первого элемента И, при этом выходы первого блока

866763

25

$0

И

60 памяти и сумматора являются выходами устроиства.

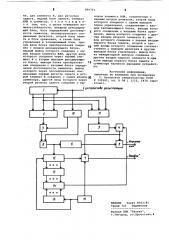

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит блок 1 преобразования, блок 2 мажоритарной выборки, элементы И 3 и 4, регистры 5 и б сдвига, блок 7 памяти, элемент ИЛИ 8, сумматор 9, декодирующий блок 10 блок 11 определения достоверности символов, делитель 12, блок 13 памяти,.блок 14 сравнения, блок 15 управления и запоминающий блок 16.

Устройство работает следующим образом.

Информация, закодированная циклическим кодом, в виде и-элементных кодовых комбинаций поступает на вход устройства. В декодирующем блоке 10 осуществляется проверка комбинаций на соответствие циклическому коду.

В случае, когда хотя бы одна из трех повторяемых комбинаций будет правильна, то по информационному выходу она будет выдана на вход элемента ИЛИ 8.

Если все повторяемые комбинации будут искажены, то по служебному выходу декодирующего блока 10 будет выдан сигнал "Ошибка", который открывает элемент И 3. Информация со входа устройства поступает также в блок

1 преобразования, осуществляющий преобразование информации иэ последовательного вида в параллельный. Одноименные разряды повторяемых комбинаций из блока 1 преобразования поступают в блок 2 мажоритарной выборки, который формирует из них символы итогс9вой комбинации по принципу большинства. Итоговая комбинация через открытый элемент И 3, элемент ИЛИ 8 поступает в регистр б сдвига и в делитель 12. По сигналу с блока 15 управления остаток от деления многочлена кодовой комбинации на образующий многочлен циклического кода считйвается в блок 13 памяти. Кроме того, при ненулевом остатке делитель

12 выдает сигнал "Ошибка" на блок 7 памяти. Если комбинация не будет искажена, то в блоке 13 памяти будет записан нулевой остаток, а в блок 7 памяти не поступит сигнал "Ошибка".

Одновременно с записью остатка в блок 13 памяти, блок 15 управления запускает запоминающий, блок 16, который формирует двоичные комбинации,соответствукищие многочленам остатков, получаемых при делении многочленов кодовых комбинаций, пораженных одиночными ошибками, на образующий многочлен циклического кода. Формируемые остатки одни эа другим поступают на первые входы блока 14 сравнения, на другие входы которого поступает остаток, хранящийся в блоке

13 памяти. Блок 14 сравнения сравнивает эти остатки и при совпадении, т.е. при наличии одиночной ошибки, выдает сигнал на вход элемента И 4.

Момент выдачи сигнала с блока 14 сравнения на вход элемента И 4 будет соответствовать искаженному разряду кодовой комбинации, пораженной одиночной ошибкой.

На второй вход элемента И 4 поступает через второй регистр 5 сдвига последовательность нулей и единиц с блока 11 определения достоверности символов, на вход которого поступают одноименные разряды повторяемых комбинации с ныхода блока 1 преобразования. Блок 11 определения достбверности символов выдает на выход сигнал "Нуль", если все одноименные разряды повторяемых комбинаций совпадают, и сигнал "Единица", если хотя бы один разряд отличается от других.

Таким образом, единицы в последовательности единиц и нулей, выдаваемой блоком 11, следовательно и регистром 5 сднига, будут отмечать недостоверные символы, а нули — достоверные символы, т.е. символы с малой вероятностью искажения.

Элемент И 4 выдает сигнал при совпадении импульсов, выдаваемых регистром 5 сдвига (импульс недостоверности данного разряда), и импульсов, выдаваемых блоком 14 сравнения (импульс одиночной ошибки в данном раз-, ряде) . Сигнал с выхода элемента И 4 поступает на один вход сумматора 9, на нторой вход которого поступает информация с регистра б сдвига, а также на сбрасывакиций вход блока 7 памяти, стирая сигнал "Ошибка".

На сумматоре 9 осущестнляется исправление одиночнои ошибки только в недостоверных символах, и исправленная комбинация поступает на первый выход устройства.

В том случае, когда делитель 12 обнаружит ошибку и выдаст сигнал на блок 7 памяти, а блок 14 сравнения не выдаст сигнал, что свидетельствует о наличии многократной ошибки в комбинации, импульсом с блока 15 управления сигнал "Ошибка" будет сосчитан с блока 7 памяти на нторой выход устройства, При получении этого сигнала получатель стирает искаженную комбинацию.

Таким образом, в предлагаемом устройстве осуществляется исправление однократных ошибок только в недостоверных символах итоговой комбинации,. что приводит к уменьшению числа непринятых кодовых комбинаций беэ заметного снижения достоверности информации, и, следовательно, к повышению помехоустойчивости ее приема.

Формула изобретения

Устройство приема многократно переданаемых комбинаций, содержащее последовательно соединенные блок преобразонания и блок мажоритарной выбор866763

8102/81 писное ки, два элемента И, два регистра сдвига, первый блок памяти, элемент

ИЛИ и сумматор, о т л и ч а ю щ е ес я тем, что, с целью повышения помехоустойчивости, введены декодирующий блок, блок определения достоверности символов, последовательно соединенные делитель, второй блок памяти и блок сравнения, а также блок управления и запоминающий блок, причем вход блока преобразования соединен с входом декодирукщего блока, первый выход которого соединен с одним входом элемента ИЛИ, другой вход которого соединен через первый элемент И с вторым выходом декодирующего блока, выходы блока преобразова- !5 ния соединены с входами блока определения достоверности символов, выход которого через последовательно соединенные первый регистр сдвига и второй элемент И соединен с одним входом Щ сумматора, другой вход которого через второй регистр сдвига соединен с выходом элемента ИЛИ, соединенным с первым входом делителя, второй вход которого соединен с одним выходом блока управления, соединенным с входом запоминающего блока, выходы которого соединены с входами блока сравнения, выход которого соединен с другим входом второго элемента И, выход которого соединен с первым входом первого блока памяти, второй и третий входы которого соединены соответственно с выходом делителя и другим выходом блока управления, выход блока мажоритарной выборки соединен с другим входом первого элемента И,при этом выходы первого блока памяти и сумматора являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 330561, кл. Н 04 L 1/10, 1970 (про,тотип).

Филиал ППП "Патент", г.ужгород, ул.Проектная,4