Устройство защиты от ошибок с решающей обратной связью

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналнстических

Реснублнк

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

«i>866766 (6! ) Дополнительное к ввт. свид-ву (22) Заявлено 0201.80 (21) 2863078/18-09 с присоединением заявки Мо (23) Приоритет

Опубликовано 23.09.81. Бюллетень М 35

Дата опубликования описания 2309.81 р1) м. кл.

Н 04 L 1/16

Государственный комитет

СССР по делам изобретений и . открытий (53) УДК 621. 394. .14(088.8) (72) Авторы (54) УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК С РЕШАЮЩЕЙ

OEPATHOR СВЯЗ ЬЮ

Изобретение относится к технике передачи дискретной информации и может быть использовано при модернизации существующей и создании новой аппаратуры передачи данных.

Известно устройство защиты от ошибок с решающей обратной связью, содержащее последовательно соединенные входной накопитель, дешифратор служебных комбинаций, счетчик блокировки и датчик сигнала обмена, а также декодйрующий блок, выходной накопитель и распределитель, ко входу которого подключен соответствующий выход дешифратора служебных комбинаций,а 15 выход распределителя подключен к первымавходам входного и выходного накопителей, при этом выход счетчика блокировки подключен к вторым входам входного и выходного накопителей,а выход входного накопителя подключен к третьему входу выходного накопителя, выход которого подключен к нторому входу датчика сигнала обмена,причем третий вход нходного накопителя объединен со входом декодирующего блока и является нходом устройства (1).

Однако известное устройство обладает низкой помехоустойчивостью. ЗО

Цель изобретения — повышение помехоустойчивости.

Для этого н устройство защиты от ошибок с решающей обратной связью, содержащее последовательно соединенные входной накопитель, дешифратор служебных комбинаций, счетчик блокировки и датчик сигнала обмена, а также декодирующий блок, выходной накопитель и распределитель, ко входу которого подключен соответствующий выход дешифратора служебных комбинаций, а выход распределителя подключен к первым входам входного и выходного накопителей, при этом ныход счетчика блокировки подключен к вторым входам входного и выходного накопителей, а выход входного накопителя подключен к третьему входу выходного накопителя, выход которого подключен к второму нходу датчика сигнала обмена, причем третий вход входного накопителя объединен со входом декодирующего блока и является входом устройства, введены элемент И и блок анализа результатон декодирования, к первому нходу которого и первому входу элемента И подключен выход декодирующего блока, а к вторым входам блока анализа результатон декодиро866766 вания и элемента И подключен выход распределителя, при этом выход элемента И подключен к второму входу счетчика блокировки. Кроме того, блок анализа результатов декодирования содержит последовательно соединенные первый элемент ЗАПРЕТ, первый элемент И, триггер, второй элемент И,первый счетЧик, третий элемент И, второй счетчик и второй элемент ЗАПРЕТ, при этом выход второго счетчика подключен к первому входу элемента ИЛИ, к второму входу которого подключен выход третьего элемента ЗАПРЕТ, а выход элемента ИЛИ подключен к установочным входам первого и второго счетчиков и триггера, второй выход которого подключен к второму входу первого элемента И, первый выход которого подключен к второму входу третьего элемента И и запрещающему входу третьего элемента ЗАПРЕТ, к второму входу которого подключен выход первого счетчика.

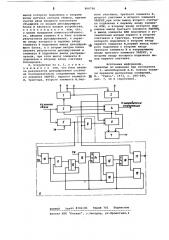

На чертеже представлена структурная схема. предложенного устройства.

Устройство содержит дешифратор 1 служебных комбинаций, распределитель

2, Входной накопитель 3, выходной накопитель 4, декодирующий блок 5, счетчик 6 блокировки, датчик 7 сигнала обмена, элемент И 8, блок 9 анализа результатов декодирования.

Блок 9 анализа результатов декодирования содержит первый элемент ЗАПРЕТ 10, первый элемент И 11, триггер

12, второй элемент И 13, первый счетчик 14, третий элемент И 15,второй счетчик 16, второй элемент ЗАПРНТ 17, .третий элемент ЗАПРЕТ 18,элемент ИЛИ 19.

Устройство работает следующим образом.

В исходном состоянии триггер 12, первый и второй счетчики 14 и 16 находятся в нулевом состоянии, первый элемент И 11 открыт, второй элемент

И 13 и третий элемент И 15 закрыты.

Результаты декодирования с выхода декодирующего блока 5, который должен быть реализован по принципу решения проверочных соотношений группового кода, поступают на входы элемента И 8 и блока 9 анализа результатов декодирования в каждом такте.

Нф выходе элемента И 8 результат декоДирования появляется один раз в цикле приема элементного кодового блока, как в известном устройстве.

На выходе первого элемента ЗАПРЕТ

10 сигнал появляется при правильном декодировании принимаемой последовательности, т.е. при выполнении проверочных соотношений. В последнем случае сигнал с выхода первого элемента ЗАПРЕТ 10 пройдет через открытый первый элемент И 11 и установит триггер 12 в единичное состояние, откроется второй элемент И 13, с выхода

40

$S

3$

$0

40 которого на вход первого счетчика 14 начнут поступать тактовые импульсы (ТИ). На выходе первого счетчика 14 с периодом и-1 будет появляться разрешающий сигнал длительностью с единичного интервала, который поступает на третий элемент И 15 и третий элемент ЗАПРЕТ 18. При появлении на выходе первого элемента ЗАПРЕТ 10 сиг-т налов, отстоящих от первого сигнала на время пс К, где К = 1,2...i, i емкость второго счетчика 16,они будут поступать через третий элемент

И 15 на вход второго счетчика 16.При поступлении i сигналов на вход второго счетчика 16, сигнал с его выхода поступит на вход второго элемента

ЗАПРЕТ 17 и, в случае несовпадения по времени с цикловым импульсом,появится на выходе блока 9 анализа результатов декодирования как сигнал

"Дать фазу";

При появлении сигналов на выходе третьего элемента ЗАПРЕТ 18 в случае, если последующий сигнал на выходе первого элемента ЗАПРЕТ 10 появится через время с ф nto К, или на выходе второго счетчика 16, они через элемент ИЛИ 19 устанавливают блок 9 анализа результатов декодирования в исходное состояние.

Таким образом, устройство анализа результатов декодирования выделяет из последовательности результатов декодирования принимаемой информационнои последовательности i+1 моментов правильного декодирования, отстоящих друг от друга на время nto,÷òî позволяет путем выбора величинй i обеспечить практически любое, сколь угодно малое значение вероятности ложного перехода (P л.п.) аппаратуры передачи данных в режим циклового фазирования (в этом случае Р л.п. 2 " где r — число избыточных элементов группового кода),и тем самым повысить помехоустойчивость передачи информации.

Формула изобретения

1. Устройство защиты от ошибок с решающей обратной связью, содержащее последовательно соединенные входной накопитель, дешифратор служебных комбинации, счетчик блокировки и датчик сигнала обмена, а также декодирующии блок, выходной накопитель и распределитель, ко входу которого подключен соответствуюШий выход дешифратора служебных комбинаций, а выход распределителя подключен к первым входам входного и выходного накопителей, при этом выход счетчика блокировки подключен к вторым входам входного и выходного накопителей, а выход входного накопителя подключен к третьему входу выходного накопителя, 866766 нНИИПИ Заказ 8102/81 Тираж 701 Подписное

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная,4 выход которого подключен к второму входу датчика сигнала обмена, причем третий вход входного накопителя объединен со входом декодирующего блока .и является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, введены элемент И и блок анализа результатов декодирования, к первому входу которого и первому входу элемента И подключен выход декодирую- а щего блока, а к вторым входам блока анализа результатов декодирования и элемента И подключен выход распределителя, при этом выход элемента И подключен к второму входу счетчика блокировки. 15

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок анализа результатов декодирования состоит из последовательно соединенных первого элемента ЗАПРЕТ, первого элемента Щ

И, триггера, второго элемента И,перного счетчика, третьего элемента И, второго счетчика и второго элемента

ЗАПРЕТ при этом выход второго счетчик ка подключен к первому входу элемента ИЛИ, к второму входу которого подключен выход третьего элемента ЗАПРЕТ а выход элемента ИЛИ подключен к установочным входам первого и второго счетчиков и триггера, второй выход которого подключен к второму входу первого элемента И,первый выход которого подключен к второму входу третьего элемента И и запрещающему входу третьего элемента ЗАПРЕТ, к второму входу которого подключен выход первого счетчика.

Источники информации, принятые во внимание при экспертизе

1. Шляпоберский B.È. Основы техники передачи дискретных сообщениЯ, М., "Связь", 1973, с. 395-399, рис. 7, 10 б (прототип).