Устройство для выделения многоразрядного кода

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ТЕЛЬСТВУ. Союз Сееетскик

Соцнаектическик

Республик (61) Дополнительное к авт. сеид-ву в 746501 (22) Заявлено 16.04. 79 (21) 2753005/18-24 Р )М. тратт. с присоединением заявки Нов (23) Приоритет—

6 06 F 7/02

Государственный комнтет

СССР не ямви нзебретення н еткрмтнй

Опубликовано 300981.Бюллетень 1я936

Дата опубликования описания 300981 (СЗ) УДК 681. 325. .66(088.8) (А

И.И.Захарчук, В.А.Смагин и Ю.В.Трудов (72) Авторы изобретения (71) Заявитель (54 ) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ МНОГОРАЗРЯДНОГО

КОДА

Изобретение относится к автоматы. ке и вычислительной технике и может быть использовано при создании цифровых систем переработки информации.

По основному авт.св. Ф 746501 известно устройство для выделения многоразрядного кода, содержащее

nx(2m-1) узлов анализа мажоритарных элементов, причем информационный вход каждого (ixj}-ого узла анализа соединен с j-ым входом i-ой группы входов устройства, где i = 1,2,...п, ) = 1,2,... (2m-1), выход i-ого мажоритарного элемента подключен к первому входу управления (ix1), (ix2),....1з (iх(2m-1))-ого узлов анализа, первый, второй, третий, четвертый и пятый выходы каждого (ixj)-ого узла анализа соединены со вторым, третьим, четвертым, пятыми шестым входами управле- 20 ния (i+1)xj-ого узла анализа, выход результата iiх 1-ого узла анализа подключен к j-ому входу i-ого мажоритарного элемента, при этом каждый (ixj)-ый узел анализа, где i = 2, З,...л;) 1,2,...(2m-l), содержит элементы И, ЙЛЙ НЕ, элемент неравнозначности, элемент запрета, причем первый вход первого элемента И соеди-. нен с информационным входом узла, ЗО выход первого элемента И подключен к первому входу первого элемента ИЛИ, выход которого соединен с. первыми входами элемента неравнозначности и элемента запрета и с выходом. результата узла анализа, выходы элемента неравнозначности и элемента запрета подключены к первым входам второго и третьего элементов ИЛИ соответственно., второй и третий входы первого злсмента И соелинены со вторым и четвертым входами управления узла анализа, второй вход элемента неравнозначности и второй вход элемента запрета подключены к первой шине управления узла анализа, второй вход второго элемента ИЛИ соединен с третьим входом управления узла анализа, вторые входы первого и третьего элементов

ИЛИ подключены к шестому и пятому входам управления узла анализа соот-. ветственно, выход второго элемента

ИЛИ соединен с первым входом второго элемента И, со вторым выходом узла анализа и через первый элемент НЕ— с первым выходом узла анализа, выход третьего элемента ИЛИ подключен ко второму входу второго элемента И, к четвертому выходу узла анализа и через второй элемент НŠ— к третьему

868748 входу узла анализа, выход второго элемента И соединен с пятым выходом узла анализа, а каждый (ixJ)-ый, узел анализа, где J = 1,2,...(2m-l), содержит элемент неравнозначности, элемент запрета, элементы И,НЕ, причем

:первый входы элемента неравноэначнос- ти и элемента запрета соединены с информационным входом узла анализа, вторые входы элемента неравнозначности и элемента запрета подключены к .первому входу управления, выход элемента неравнозначности соединен с первым входом элемента И, со вторым выходом узла анализа и через первый элемент НŠ— .с первым выходом узла анализа, выход элемента запрета, 15 подключен ко второму входу элемента

И, к четвертому выходу узла анализа и через второй элемент НŠ— к третьему выходу узла анализа, выход элемента И соединен с пятым выходом Щ узла анализа. Это устройство позволяет формировать на выходе код среднего значения совокупности входных кодов (1).

Недостатком указанного устройства р5 является невозможность выделения наряду со средним минимального н макси мального кодов.

Цель изобретения — расширение функциональных возможностей за счет выделения наряду со средним максимального и минимального кодов.

Поставленная цель достигается тем, что устройство для выделения многоразрядного кода содержит дополнительно и элементов ИЛИ, и элементов И, и управляющих элементов И и объединяющих элементов ИЛИ, причем информационные входы каждого мажоритарного элемента соединены с одноименными входами соответствующих элементов И и ИЛИ, управляющие входы мажоритарных элементов подключены к первой шине задания режима устройства, управляющие входы элементов И подключены ко второй шине задания 4 режима устройства, выход каждого элемента ИЛИ соединен с первым входом соответствующего управляющего элемента И, второй вход которого подключен к третьей шине задания режима устройства, входы каждого объединяющего элемента ИЛИ соединены с выходами соот.-етствующих элементов И, мажоритарного элемента и управляющего элемента И, а выход — с первыми входами управления узлов анализа соответствующего столбца и с соответствующим выходом устройства.

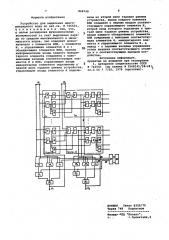

На чертеже показана функциональная схема предлагаемого устройства для случая n = 2. бО

Устройство содержит пх (2m-1) узлов анализа 1+,..., 1 (2m-l ), 121,..., 1 (2m-1 ), . ° ., n мажоритарных элементов 2,1,2,..., каждый узел анализа

1й (где i = 2,...,п; ) = 1,...,(2m 1) 65 содержит элемент И 3, элемент 4 не-;, равнозначности, элемент 5 запрета, элементы ИЛИ 6,7 и 8, элементЯ BE s и 10 и .элемент И 11. Каждый узел анализа 11 содержит элемент 12 неравнозначности, элемент 13 запрета, элементы HE 14 и 15 и элемент H 16.

Устройство имеет И выходов 17, 17, и и групп входов 18.,18,... по (2а-1) входов в каждой группа. Устройство дополйительно содержйт n элементов ИЛИ 19(, 19<,...,n эле,ментов И 20, 20@,...,п управляющих элементов И 211,22й,..., n объединяющих элементов ЙЛИ 22, 22 . .. °

Устройство содержит также шины 23,24 и 25 задания режимов, сигналы на которых задаются, например, с помощью регистра 26 режима, выходы которого подключены ко входам дешифратора 27, выходы последнего соединены с шинами 23, 24 и 25 задания режимов. Выход каждого элемента ИЛИ 19к соединен с первым входом соответствующего управляющего элемента И 21 (k1,...,п).

Управляющие входы мажоритарных элементов 2к соединены с шиной 23 задания режимов (появление сигнала на этих входах мажоритарных элементов позволяет осуществлять прием информации на информационные входы мажоритарных элементов 2к) . Управляющие входы элементов И 20к соединены с шиной 24 задания режимов. Вторые входы элементов И 21к, соединены с шиной 25 задания режимов. Выходы элементов И 20к, 21 и мажоритарного элемента 2 к соединены со входами элемента ИЛИ 22„, выход которого соединен с выходом 17к устройства.

При выделении среднего кода единичный сигнал формируется на шине

23 и поступает на управляющие входы мажоритарных элементов 2к, разрешая прием на них информационных сигналов.

На входы 18 устройства поступают коды чисел, причем значения первых разрядов кодов поступают на входы узлов анализа 1 1,..., 11(2m-1) и на входы элементов ИЛИ 19, И 201, и мажоритарного элемента 2, значения i-x разрядов кодов поступают на входы узлов анализа 1,д,... g 1 i (2m-1) . Элементы И 20к и 21< закрыты нулевыми сигналами на шинах 24 и 25, а мажоритарные элементы 2к открыты сигналом на их управляющих входах, поступающим с шины 23, и, таким образом, к выходу 17к подключен через элемент

ИЛИ 22> выход мажоритарного элемента 2к.

В режиме выделения среднего кода предлагаемое устройство работает так же, как и известное. На выходе макоритарного элемента 2 (и соответственно на выходе 174 ) образуется значение первого разряда кода, которое затем сравнивается узлами анализа

868748

1И,..., 1, (2а-1) с первыми разрядами соответствующих чисел. При совпадении, значений первого разряда j-ого числа и выходного разряда ("0", "0" или

"1", "1") устройство подготавливает следующий узел анализа 1 > к приему второго разряда соответствующего чи сла, который проходит на соответствукщий j-ый вход мажоритарного элемента

2 ..В случае несовпадения значений первого разряда ) -ого числа и выходного разряда ("0", I" илн i" "v ) на соответствующие )-ые входы всех мажоритарных элементов 2й,...,2 и подаются соответственно значения "0" или "1". После поступления на входы ма (оритарного элемента 2 значений разрядов чисел, первые Разряды которых совпадают по величине с первым разрядом результата, а также значений "0" или "1" вместо разрядов тех чисел, первые разряды которых не совпадают по величине с первым разрядом результата, этим мажоритарно элементом 2 формируется значение второго разряда результата, которое поступает на выход 172 и сравнивается затем на блоках 12,...,12(2 к-1), которые соответствуют тем числам, первые разряды которых совпадают по величине с первым разрядом результа.та. Дальнейшая работа устройства по формированию последукщих разрядов результата и их анализу в соответствии с соответствукщнмн разрядами чисел аналогична вышеуказанной. Таким образом, на выходах 17,...,17 фор" мируется средний код.

В режиме выделения минимального кода сигнал "1" формируется на шине

24 по потоку к выходам 17,...,17и, которые оказываются подключенными (через элементы ИЛИ 22,..., 22и).

Элементы И 204,...,20н соответственно, элементы ИЛИ 19, ° ° °,19н и мажоритарные элементы 2,...,2> в это время отключены от выходов 17, ...,17И соответственно, так как сигналы на шинах 23 н 25 в это время равны "0". При анализе первых разрядов всех чисел, поступающих на входы 18, элемент И 20 срабатывает только в том случае, когда все эти разряды равны "1", в случае же наличия среди первых разрядов чисел хотя бы одного "0" сигнал на выходе элемента И 20,(и соответственно на выходе 17) равен "0". Таким обраэом,на выходе 17 формируется первый разряд результата, значение которого совпадает со значением первого разряда минимального числа; .После этого аналогично режиму выделения среднего кода йроизводится сравнение первого разряда результата и первых разрядов сравниваемых чисел (с учетом того, что в данном случае запрещенной является комбинация, когда разряд числа равен "0", а раэ-, ряд результата равен 1", чего ие может произойти в правильно работающем устройстве) . Таким образом, последукщие разряды тех чисел, у которых соответствующий разряд не совпадает с разрядом результата, заменяются при формировании последукщих разрядов результата значениями "1", а само формирование последукщих разрядов результата на элементах И 20, g ...,20 осуществляется аналогично укаэанйому выше. Таким образом, на каждый из выходов 17,...,17Ь проходит значение "0", если присутствует хотя бы один "0" среди соответст- . вукщих разрядов сравниваекайх чисел, а разряды тех чисел, предыдущие разряды которых не совпадают с разрядами результата, заменяются на значения "1" н в дальнейшем сравнении эе участвуют.

В режиме выделения максимального кода сигнал "1" формируется на шине

25 и выходы элементов ИЛИ 19,...,19> через открытые по второму входу элементы И 21,...,21и и элементы ИЛИ

22,...,22и оказываются подключенными к выходам 174 17 соответственно.

Выходы элементов И 20,...,20н и мажоритарных элементов 2,...,2 н в это время отключены от соответствующих.выходов 17,...,17, так сигналы на шинах 23 и 24 в это время равны

"0". При анализе первых разрядов всех чисел, поступающих на входы 18,, элемент ИЛИ 194 пеРедает на выход 174 значение "1" в случае наличия ее в первом разряде хотя бы одного иэ чисел. В дальнейшем производится сравнение первого разряда каждого из чисел с первым Разрядом результата с

40 помощью узлов анализа 1, °, 1 к х(2а-1) так же, как было указано ранее (в данном случае запрещенной является такая ситуация, когда разряд числа равен "1", а соответствующий

45 Разряд резУльтата равен "0"). В тех иэ чисел, в которых значения разрядов не совпадают со значением разряда результата, все последующие разряды заменяются значениями "0" и, таким образом, эти числа в дальнейшем выделении максимального кода не участвуют. Во всех последукщих разрядах выделение производится аналогично: в случае наличия значения "1" в соответствующем разряде хотя бы одного иэ сравниваемых чисел это значение передается на соответствующий выход 17.

Таким образом, предлагаемое устрой40 ство по сравнению с известным кроме выделения значения среднего кода позволяет выделять значения минимального и максимального кодов, что ведет к расширению его функциональных g5 возможностей;.868748

Формула изобретения

Устройство для выделения многоразрядного кода по авт.св. 9 746501, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет выделения наря-ду.со средним максимального и минимального кодов, оно содержит дополнительно и элементов ИЛИ, и элементов

И, и управляющих элементов И и и объединяющих элементов ИЛИ, причем информационные входы каждого мажоритарного элемента соединены с одноименными входами соответствующих элементов И и ИЛИ, управляющие входы мажоритарных элементов подключены к первой. шине задания режима устройства управляющие входы элементов И подключены ко второй шине задания режима устройства, выход каждого элемента

ИЛИ соединен с первым входом соответствунщего управляющего элемента И, второй вход которого подключен к третьей Шине задания режима устройства, входы каждого объединяющего элемента

ИЛИ соединены с выходами соответствующих элементов И, мажоритарного элемента и управляющего элемента И, а выход - c первыми входами управления узлов анализа соответствующего столбца и с соответствующим выходом устройства.

Источники информации,, принятые во внимание при экспертизе

5 1. Авторское свидетельство СССР

9 746501 (по заявке 9 2568141/18 24), кл.G Об F 7/02, 1978 (прототи ). >

ВНИИПИ Заказ 8329/70

Тираж 748 Подписное

Филий,-пПП "Патент" г. .,Проектная,4