Устройство для умножения

Иллюстрации

Показать всеРеферат

ОПЙСАЛИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Рес убли (63) Дополнительное к авт. свид-ву (22) Заявлено 13.1238 (21) 2695323/18-24 (5 }

G 06 F 7/52 с присоединением заявки ¹

Государственный комитет

СССР по делам нзобретеннй н открытнй (23) Приоритет

Опубликовано 300981. Бюллетень ИЯ 36

Дата опубликования описания 30. 09 . 81 (53} УДК .681.325 (088.8) (72) Авторы изобретения

Ю.П.Барметов и Ю.И.Евтеев (71) Заявитель

5 6,1 И. < ii.w p

Воронежский технологический институт. (54 ) УСТРОИСТВО ДЛЯ УМНОЖЕНИЯ

Изобретение относится к цифровой вычислительной технике.и предназначено для умножения двоичных чисел, представленных в форме фиксированной запятой.

Известны устройства для умножения, формирующие произведения двух чисел иэ частных произведений одного иэ них на различные группы разрядов (Ц и (2) .

Наиболее близким по технической сущности к предлагаемому является устройство для умножения, содержащее генератор кратных множимого, регистр множителя, коммутаторы, параллельные сумматоры без распространения переноса, параллельный сумматор с одновременным переносом и элементы задержки (3) .

Однако данное устройство обладает относительно низким быстродействием .вследствие применения элементов задержки для синхронизации поступления различных Разрядов На сумматоры 25

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройстве для умножения, содержащем генератор кратных множимого, коммутаторы и блок-суммирования частичных произведений, причем вход множимого устройства подключен ко входу генератора кратных множимого, m выходов которого подключены к информационным входам и коммутаторов (= †„;m = 2, где 6 — количество

8 разрядов множителя; k — количество разрядов в каждой группе множителя), управляющие входы которых соединены с и входами групп разрядов множителя, а выходы подключены ко входам блока суммирования частичных произведений, блок суммирования частичных произве-. дений содержит (n-1) (p+k) ðàçðÿäíûõ комбинационных сумматоров (р — количество разрядов множимого), причем разрядные входы первой группы каждого i-ого сумматора (i = l,...,n-l) соединены с выходами разрядов соответствующего

i-ого коммутатора, а разряды второго входа — с р старшими разрядами выхода (i+1) — ого сумматора, разрядные входы второй группы (и-1) -ого сумматора соединены с р старшими разрядами выхода п-ого коммутатора, разряды выхода первого сумматора, K младших разрядов выхода каждого из последующих сумматоров и k младших разрядов выхода n-oro коммутатора являются раэрядами выхода устройства.

868752

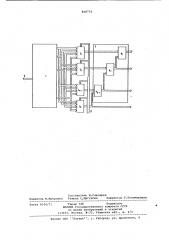

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит генератор 1 кратных множимого, комммутаторы 2 (2 „, 2 ...,, 2„), блок 3 суммирования частичйых произведений, содержащий (n-1) комбинационных сумматоров 4 (4« 4я < ) . Код множимого (М) подается со входа 5 множимого устройства на вход генератора 1 кратных множимого а код множителя — со вхоР (О да 6 множителя устройства на управляющие входы коммутаторов 2, соответственно группами,по разрядов.На выходах генератора 1 кратных множимого формируются коды произведений разрядов множимого на все возможные числа 15 от 0 до N {N - максимальное возможное число, записываемое k разрядами

N 2 -1) . С выходов генератора 1 коды полученных произведений подаются на информационные входы коммутаторов

2 таким образом, чтобы на входы каждого коммутатора 2 подавались произведения множимого на все возможные числа.от 0 до N„

На выходах коммутаторов 2 формируются коды произведений множимого на те разряды множителя, которые подаются на управляющие входы коммутаторов

2. Коды с выходов коммутаторов 2 поступают на входы соответствующих параллельных сумматоров 4, на другие входы которых поступают старшие разряды результатов сложения на предыдущих сумматорах 4. Результат умножения формируется выходом сумматора 4„, а 35 также группами младших разрядов с выходов сумматоров 4,..., 4п и последнего коммутатора 2.

За счет изменения конструкции суммирующего блока увеличивается быстро- 4р действие предлагаемого устройства, работающего в параллельном режиме.

Формула изобретения

Устройство для умножения, содержащее генератор кратных множимого, коммутаторы и блок суммирования частичных произведений, причем вход множимого устройства подключен ко входу генератора кратных множимого, m выходов которого подключены к информационным. входам и коммутаторов (n

m = 2к, где Ю вЂ” количество разрядов множителя> k — количество разрядов в каждой группе множителя), уйравляющие входы которых соединены с п. входами групп разрядов множителя, а выходы подключены Ко входам блока суммирования частичных произведений, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, блок суммирования частичных произведений содержит (п-1) (р+) )-разрядных комбинационных сумматоров (р — количество разрядов множимого), причем разрядные входы первой группы каждого i-ого сумматора (i = 1,..., п-1) соединены с выходами разрядов соответствующего

i-ого коммутатора, а разряды второго входа — с р старшими разрядами выхода (i+1)-oro сумматора, разрядные входы второй группы (n-1) -ого сумматора соединены с р старшими разрядами выхода и-ого коммутатора, разряды выхода первого сумматора, к младших разрядов выхода каждого иэ последующих сумма.— торов и k младших разрядов выхода п-oro коммутатора являются разрядами выхода устройства, Источники ниформации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 562818, кл. G 06 F 1/39, 1975.

2 ° Патент ClOA 9 4041292, кл, 235-164, 1977 .

3. Авторское свидетельство СССР

М 583433, кл . G 06 F 7/39, 197 6 (прототип) .

8á8752

Составитель Н.Слюсарев

Редактор М,Митровка Техред С,.Мигунова Корректор У.Пономаренко

Заказ 8330/71

Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4