Устройство для проведения матричных испытаний микроэлектронных схем

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИКАНИЕ

ИЗОБРЕТЕНИЯ о| 868778

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву !е 760117 (22) Заявлено 021179 (21) 2841294/18-24 с присоединением заявки ¹â€” (St)hA. Нл.З

G 06 F 15/46

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет—

Опубликовано 300981. Бюллетень ЙЯ 36

Дата опубликования описания 30Р981 (53) УДК 621 ° 396 (088. 8) (72) Авторы изобретения

Ф. Ф. Колпаков, В. А. Шевелев, A. Е. Сычев. и В. П. Семенов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРОВЕДЕНИЯ МАТРИЧНЫХ

ИСПЫТАНИЙ МИКРОЭ1!ЕКТРОНН61Х CXEM

Изобретение относится к автоматике и вычислительной технике и предназначено для исследования и оптимизации параметров микросхем и допусков на них по критерию процента выхода годных микросхем любых безынерционных схем в статическом режиме.

По основному авт. св. 9 760117 известно устройство, содержащее блок управления, выход которого подключен к управляющим входам датчика случайных чисел, блоков формирования тестовых сигналов моделирования, контроля, построения сечений области работоспособности, вычислительных блоков,накопителей, элементов И, блока установки номинальных значений и детектора влияния параметров, первый вход соединен с первым выходом генератора тактовых импульсов, остальные 2О выходы которого подключены к первым входам блоков коммутации, контроля и установки номинальных значений, второй вход блока коммутации соединен с выходом блока перебора реализации, вход которого связан с выходом датчика случайных чисел, выход блока коммутаций подключен к первому входу блока моделирования, второй вход которого связан с выходом блока ЗО формирования тестовых сигналов, а выход — ко второму входу блока контроля, выход которого связан с входом анализатора реализаций, первый выход которого соединен со входом блока построения сечений области работоспособности, подключенного выходом через первый вычислительный блок ко второму входу блока установки номинальных значений, подключенного выхо.дами ко второму входу блока управления и детектору влияния параметров, связанного выходом с первым входом второго вычислительного блока, вторые входы которого связаны с выходаМи накопителей, подключенных входами к выходам элементов И, входы которых и третий вход блока управления соединены соответственно со вторым и третьим выходами анализатора реализации.

Недостаток известного устройстванеудовлетворительная точность устройства, так как при построении гистограммы, т.е. дифференциальной функции распределения выходного сигнала испытуемого устройства считается,что вероятность появления каждой комбинации квантов варьируеьых параметров, удовлетворившей условиям работоспособности и дающей в соответствующий

868778 накопитель единицу, одинакова. На самом деле вероятность появления кван-. та параметра изменяется в пределах поля допуска в соответствии с законом распределения погрешности данного параметра, отличного от равнове5 роятного. Поэтому и вероятность каждого сочетания квантов параметров испытуемой схемы будет различной. Другими словами, для точного построения гlte. тограммы распределения выходного сигнала испытуемой схемы с учетом влияния условий эксплуатации необходимо знать не только количество неот-. казавших реализации в каждом из диапазонов, на:которые разбит весь воз— можный диапазон изменения выходного сигнала, но и вероятность каждой реализации, и учитывать зто при построе— нии гистограммы. Неучет этого факта приводит к неверному определению закона распределения выходного сигна- 2Q ла испытуемого устройства, и, в конечном .счете, к недостаточной точности получаемых устройством результатов.

Цель изобретения — повышение точности устройства. 25

Поставленная цель достигается тем, что в устройство для проведения матричных испытаний микроэлектронных схем, введены блоки умножения, подключенные первыми входами к выходам соответствующих элементов И, вторыми входами — ко второму выходу второго вычислительного блока, третьими входами — к первым входам элементов И, а выходами — ко входам соответствующих накопителей.

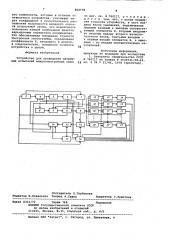

На чертеже представлена функциональная схема устройства.

Схема содержит блок 1 коммутации, блок 2 перебора реализаций, датчик 3 случайных чисел, блок 4 управления, 40 генератор 5 тактовых импульсов, блок

6 формирования тестовых сигналов,блок 7 моделирования, блок 8 контроля, анализатор 9 реализации, элементы И 10, накопители 11, блок 12 пост роения сечений области работоспособности, первый вычислительный блок 13, блок 14 установки номинальных значений, детектор 15 влияния параметров, второй вычислительный блок 16, блоки

17 умножения.

Устройство работает следующим образом.

После пуска устройства блок 4 управления, работающий по заданной программе, выдает команду в датчик случайных чисел, который случайным образом выбирает кванты в соответствующем исходном диапазоне каждого параметра схемы, разрешает выдачу сигналов о координатах первого случайно- до го вектора в блок 2 перебора реализации на срабатывание соответствующих ключевых элементов блока 1 коммутации для включения выбранных представителей квантов внутренних параметров физической модели схемы в блок 7 моделирования. На вход собранной физической модели схемы из блока 6 тестовых сигналов подается комплекс входных сигналов, а блок 8 контроля и анализатор 9 реализаций в соответствии с заданными ограничениями на выходные параметры схемы проводят оценку реализации (работоспособность схемы при данном наборе значений внутренних параметров). Сигнал с анализатора 9 реализаций поступает на блок 4 управления, который в случае неудовлетворения первого случайного вектора условиям работоспособности выдает команду.в датчик 3 случайных чисел на выбор следующего случайного вектора, в противном случае дает разрешение в датчик 3 случайных чисел с поступлением следующих тактовых импульсов на проведение последовательного попарного случайного перебора квантов первого и второго внутренних параметров схемы, причем остальные параметры представлены своими номинальными значениями, являющимися координатами случайного вектора, удовлетворившего условиям работоспособности.

Результаты оценки работоспособности каждой ситуации попарного случайного перебора и координаты квантов параметров, участвующих в реализации, выдаются также в блок 12 построения сечения области работоспособности. Полученное таким образом двумерное сечение области работоспособности по команде блока 4 управления передается в первый вычислительный блок в виде, удобном для его работы. Вычислительный блок 13 вписывает в каждое двумерное сечение области работоспособности оптимальное двумерное сечение допусковой области. Параллельно с работой вычислительного блока 13 продолжается случайный перебор квантов первого и третьего внутренних параметров схемы, первого и четвертого и т.д. Таким образом, получают серию оптимальных двумерных сечений допус-. ковой области относительно первого параметра. Первый вычислительный блок

13 проводит совместную обработку всей серии сечений, определяя максимально допустимый диапазон изменения первого параметра и его оптимальное для этой серии сечений номинальное значение. При получении сечения области работоспособности первого и последнего параметров первый вычислительный блок

13 останавливает работу устройства до момента выдачи оптимального номинального значения первого параметра для первого случайного вектора, удовлетворившего условиям работоспособности.По окончании обработки серии сечений первого параметра с остальными по команде блока 4 управления это значение сообщается в блок 14 установки номинальных значений, который преобразует

868778 номер кванта, соответствующий опти- мальному значению первого параметра в вид,. удобный для изменения программы работы блока 4 управления, и блокирует работу устройства на время своей работы и время включения представителя кванта первого парамет- .

5 ра, соответствующего определенному номинальному значению (время блокировки кратно периоду поступления тактовых .импульсов), после чего с поступлением следующих тактовых импульсов дает команду на продолжение работы устройства.

Аналогичным образом проводится попарный случайный перебор второго внутреннего параметра схемы со. все- 15 ми остальными, кроме первого, и определяется его оптимальное номинальное значение, затем третьего со всеми остальными, кроме первого и второго параметров и т.д. 20

По окончании попарного случайного перебора всех параметров для первого случайного вектора, удовлетворившего условиям работоспособности, и нахождения оптимальных номинальных значений последние по команде блока

4 управления, поступают в детектор 15 влияния параметров, где находятся коэффициенты влияния каждого входного параметра исследуемой схелы на выходной параметр и по команде блока 4 30 управления передаются во второй вычислительный блок 16, который íà основании известного коэффициента вариации г = ц /m определяет средне1

3,5 квадратические отклонения о; для m j каждой компоненты вектора, полученного в ходе обработки двумерных сечений для каждого начального случайного вектора„ удовлетворившего условиям работоспособности, передает их в 4О блок 4 управления, остановив работу устройства на время, кратное периоду поступления тактовых импульсов и внеся изменения в работу блока управления. Блок 4 управления, отключив датчик случайных чисел, управляет блоком 2 перебора реализации, пройдя по заданной программе полный перебор .комбинации квантов из поля 36„ каждого параметра. Сигналы с каждой реализации квантов поступают на срабатывание соответствующих ключевых эле-. ментов блока 1 коммутации для включения выбранных представителЕЯ квантов внутренних параметров физической модели в блок 7 моделирования, а так- 55 ,же (в удобном для последующей работы виде) во второй вычислительный блок

16. На вход собранной физической модели схемы из блока 6 тестовых сигналов подается комплекс входных сиг- @) малов, а блок 8 контроля и анализа-» тор 9 реализаций в соответствии с заданными ограничениями на выходные параметры схемы проводят оценку реализации. Блок 4 управления дает раз-, решение на параллельное считывание результата оценки работоспособности каждой реализации с анализатора 9 реализации на группу элементов И 10, настроенные каждый на определенное число, на которое разбит весь возможный диапазон изменения выходного сигнала испытуемой схемы. На выходе элемента И, у которого н данной реализации число совпадает с поступившим с анализатора 9 реализации, появляется сигнал, в числовом эквиваленте равный единице. Параллельно с оценкой реализации в анализаторе 9 реализации во втором вычислительном блоке

16 определяется вероятность этой комбинации с учетом закона распределения входных лараметров исследуемой схемы, значение которой в удобном для последующей работы виде по коман-де блока 4 управления подается на первые входы блоков 17 умножения,на вторые входы которых также по сигналу блока 4 управления, выдаются сиг-. налы с соответствующих элемеHToB И

10. В одном из блоков 17 умножения, на который подавался ненулевой сигнал с элемента И, появляется сигнал, пропорциональный вероятности появления выходного параметра испытуемой схемы в заданном диапазоне разбиения, который по команде блока управления поступает в соответствующий накопитель. В результате полного перебора комбинации квантов в диапазоне + 36„ каждого параметра для первого номинального вектора, полученного в ходе обработки двумерных сечений, в накопителях 11 собираются числа, предс тавляющие в целом гистограмму, т.е. дифференциальную функцию распределения выходного сигнала испытуемой схемы, причем информация с накопителей по сигналу блока управления поступает во второй вычислительный блок 16, который определяет закон распределения выходного параметра и на основании данных о коэффициентах влияния входных параметров, закона распределения входных параметров и корреляционных связей между ними определяет оптимальные допуски на параметры схемы для первого начального случайного вектора. Аналогичным образом прово,— дится цикл испытаний для остальных начальных случайных векторов, после чего второй вычислительный блок выбирает по заданному алгоритму из серии полученных номинальных точек оптймальную и печатает значения номиналов компонентов и допусков на них.

Таким образом, введение в устроЯство для проведеиия матричных испытаний микроэлектронных схем между выходами соответствующих элементов И и входами накопителей блоков умножения,,позволяет получить помимо оптимального номинального вектора параметров схемы такие оптимальные допуски нв

868778

Формула изобретения

Составитель Н. Горбунова

Редактор И.Ковальчук Техред A.Ñàâêà Корректор Г.Решетйик

Эаказ 8331/72 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 его компоненты, которые в отличие от известного устройства, учитывают через коэффициент К относительного рассеивания погрешности входного сигнала испытуемой схемы, что вероятность появления каждой комбинации квантов варьируемых параметров неодинакова.

Это обеспечивает повышение точнбсти построения гистограммы, определения коэффициента К, входящего в допуск, а следовательно, повышение точности устройства в целом.

Устройство для проведения матричных испытаний микроэлектронных схем по авт. св. Р 760117, о т л и ч а ющ е е с я тем, что, с целью повышения точности устройства, в него введены блоки умножения, подключенные первыми входами к выходам соответствующих элементов И, вторыми входамико второму выходу второго вычислительного блока, третьими входами к первым входам элементов И, а выходами - ко входам соответствующих накопителей.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 760117 по заявке Р 2630041/18-24, >5 кл. G 06 F 15/46, 1978 (прототип).