Широтно-импульсное множительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик (i<>868783 (61) Дополнительное к авт. саид-ву(22) Заявлено 180180 (21) 2871917/18-24

М )<лз с присоединением заявки No(23) ПриормтетG G 7/16

Государствеииый комитет

ССС Р оо делам изобретеиий и открытий

Опубликовано 300981. БюЛлетень М36

Дата опубликования описания 300981 (5З) УД)(681.335 (088. 8) (72) Авторы изобретения.М.Ф.Бартновский,A.C.Äàâûäoâ, В.У.Кизилов и И.И.,Смилянский

4ь (-,ц-, и, С

" м и яв;),:л ъ„

Харьковский ордена Ленина политехнический институт им.В.И.Ленина i а ь.й, и 1 i:. ь

1 (71) Заявитель (54) ШИРОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к аналоговой вычислительной технике, в частности к множительным устройствам.

Известны широтно-импульсные множительные устройства, в которых результат перемножения представляется в виде разности длительностей импульсов, содержащий интеграторы, компараторы и ключи (1).

Основной недостаток. этих устройствсложность преобразования выходного сигнала в цифровой код.

Наиболее близким по технической сущности к предлагаемому устройству является широтно-импульсное множи- 15 тельное устройство, которое содержит широтно-импульсный модулятор, состоящий из последовательно соединенных интегратора, ко входу которого подключен источник входного сигнала, 20 и компаратора, ко входу которого подключен другой источник входного сигнала, дополнительный компаратор и два ключа {2) .

В этом множительном устройстве ре- 25 эультат перемножения входных сигналов представляется в виде относительной разностц длительностей четырех разнополярных импульсов, что умень шает точность преобразования иэ-за 30 увеличения погрешности дискретности и влияния фронтов выходных импульсов, а также уменьшает быстродействие уст- ройства.

Цель изобретения — повышение точности и быстродействия.

Поставленная цель достигается тем, что в широтно-импульсном множительном устройстве, содержащем источник первого сомножителя, широтно-импульсный модулятор, состоящий из.последовательно соединенных ийтегратора и основного компаратора, первый вход которого является входом второго сомножителя устройства, второй вход основного компаратора подключен к шине нулевого потенциала, а выходподключен к первому суммирующему входу интегратора, дополнительный компаратор, первый вход которого подключен к выходу интегратора, и два ключа, второй вход дополиительного ком паратора подключен к.шине нулевого потенциала, а выход — к управляющим входам первого и второго ключей, прямой выход источника первого сомножителя через первый ключ подключен ко второму суммирующему входу интег» ратора, инверсный выход источника первого сомножителя через второй

868783 ключ подключен к третьему суммирующему входу интегратора, выход основного компаратора является выходом устройства.

В результате выходной сигнал устройства формируется в виде двух

Разнополярных примыкающих импульсов, относительная разность длительностей которых пропорциональна произведению входных сигналов, что уменьшает погрешности дискретности при преобразовании и погрешности, связанные с длительностью фронтов.

Быстродействие увеличивается за счет уменьшения в два раза минимально возможного периода измерения.

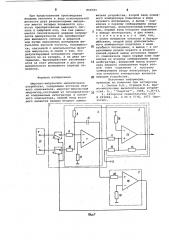

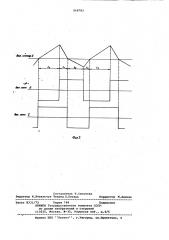

На фиг.1 приведена принципиальная схема широтно-импульсного множительного устройства; на фиг.2 — временные диаграммы работы множительного устройства.

Широтно-импульсное множительное устройство содержит широтно-импульсный модулятор 1, компаратор 2 и ключи 3 и 4 на полевых транзисторах с каналом различной проводимости.

Широтно-импульсный модулятор 1 содержит интегратор 5 и основной компаратор 6. Интегратор 5 выполнен на . операционном усилителе 7, к инвертирующему входу. которого подключены первые выводы резисторов 8-10, вторые выводы которых образуют первый, второй и третий суммирующие входы ин- . тегратора соответственно, выход операционного усилителя 6 является выходом множительного устройства, неинвертирующий вход операционного усилителя 7 через резистор 11 подключен к шине нулевого потенциала, между инвертирующими входом и выходом операционного усилителя включен конденсатор 12, основной компаратор б выполнен на операционном усилителе

13 и резисторах 14-17, дополнительный компаратор, выполнен на операционном усилителе 18 и резисторах 19 и

20. Выход интегратора 5 подключен к первому входу компаратора 2, который переключается при переходе через ноль напряжения на выходе интегратора 5. Выходной сигнал компаратора 2 управляет работой ключей 3 и 4, работающих в противофазе. Через ключи

3 и 4 ко второму и третьему суммирующим входам интегратора подключены выходы источника 21 парафаэного входного сигнала первого сомножителя.

Широтно-импульсное множительное устройство работает следующим.образом.

При отсутствии входных сигналов интегратор 5 и компаратор б работают в автоколебательном режиме как релаксационный генератор. На выходе интегратора 5 формируется симметричное пилообразное напряжение, а на выходе компаратора б — напряжение прямоугольной формы. Дополнительный компаратор 2 переключается при пере ходе через ноль напряжения на выходе интегРатора 5. На выходе компаратора 2 формируется напряжение прямоугольной Формы, которое подается на управление ключами 3 и 4. При сутствии входных сигналов относительная разность длительностей импульсов на выходе компаратора б равна нулю. Если на вход интегратора подан входной сигнал-сомножитель !

О Х, а на вход компаратора 6 сигналсомножитель У, то происходят следующие изменения в работе схемы, Скорость измерения напряжения на выходе интегратора будет равна

15 — (u0- X) — при положительных

—," сu,+х) „- i g „+ - 1- - . х 1 „+ 6 -» 1 . Up U<

1аким образом, относительная разность длительностей двух примыкающих импульсов на выходе компаратора б оказывается пропорциональной проиэ6 ведению входных сигналов. напряжениях на выходах компараторов б и 2;

20 — — 9 - Х ) — при положительном напряжении на выходе компаратора 6 и отрицательном напряжении на выходе компарато25 ра 2; при отрицательных напряжениях на выходах компараторов 6 и 2; — — (Но-х) — при отрицательном

О напряжении на выходе компаратора б и положительном напряжении на выходе ком35 паратора 2, где Тд — постояннная времени интегрирования;

Ug — выходное напряжение компаратора б.

Длительности участков, на которых

40 напряжение на выходе интегратора изменяется с постоянной скоростью (фиг.2), равны

uc+Y нс- Ч = о и„.,х 1 aоо-х "с- где U< — порог срабатывания кЬмпаратора 6.

Длительности положительного Ф, и отрицательного импульсов на выходе компаратора 6 равны (.„=4 +++, С = kg+ +kg

Относительная разность длительнос-, тей положительного и отрицательного

С импульсов эа период Т генерируе- . мого напряжения

868783

При представлении произведения входных сигналов в виде относительной разности двух разнополярных импульсов вместо четырех повышается точность преобразования выходного сигнала в цифровой код, так как уменьшается относительное влияние погрешности дискретности при преобразова,нии выходного сигнала в цифровой код путем заполнения интервалов импульсами высокой частоты, погрешности, связанной с длительностью фронтов импульсов, в связи с тем, что результирующая погрешность определяется не на четырех, а на двух интервалах. Быстродействие увеличивается за счет уменьшения в два раза минимального возможного периода измерения.

Формула изобретения

Широтно-импульсное множительное устройство, содержащее источник первого сомножителя, широтно-импульсный модулятор, состоящий из последовательно соединенных интегратора и основного компаратора, первый вход кото- рого является входом второго сомножителя устройства, второй вход основного компаратора подключен к шине нулевого потенциала, а выход - подключен к первому суммирующему входу интегратора, дополнительный компаратор, первый вход которого подключен к выходу интегратора, и два ключа, о т л и ч а ю щ е е с я теМ, что, с целью повышения точности и быстродействия, второй вход дополнительного компаратора подключен к шине нулевого потенциала, а выход " к управляющим входам первого и второго ключей, прямой выход источника первого сомножителя через первый ключ подключен ко второму суммирующему входу

15 интегратора,.инверсный выход источника первого сомножителя через второй ключ подключен к третьему суммирующему входу интегратора, выход основного компаратора является выходом устройства.

Источники информации, принятые во внимание при экспертизе

l. Смолов В.Б., Угрюмов Е.П. Время-импульсные вычислительные устройства. Л., Энергия, 1968, с.36-43.

2. Авторское свидетельство СССР

9 492886, . G 06 G 7/16, 1973 (прототип) .

868783 даю. имиар

Составитель Т.Сапунова

Редактор И.Ковальчук Техрел Л.Пекарь Корректор М.Демчик

Заказ 8331/72 Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР. по делам изобретений и открытий

113035, Москва, Ж-35, Раужская наб., д.4/5 филиал ППП Патент, г.ужгород, ул. Проектная, 4