Ассоциативный запоминающий элемент на мдп-транзисторах

Иллюстрации

Показать всеРеферат

Союз Соввтсиик

Социалистических

Респубпии

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИЯЕТЕЛЬСТВУ ((u868834 (6!) Дополнительное к авт.сеид-ву (22) Заявлено 04. 01. 80 (21) 2864922/18-24 с присоединением заявки М— (53)M. Кл.

С II С 15/04

)Осудэрстееииый K0NHTOT (23) Приоритет— ио делан изебретеиий и открытий

Опубликовано 30.09.81. Бюллетень М 36

Дата опубликования ollNcBHH$I 30.09.81. (53) У Д, К 681. 327 (088. 8) (72) Ааторы изобретения

С. И. Наймарк и С. И. Коняев (71) Заявитель (54) АССОЦИАТИВНЫЙ ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

НА МДП-ТРАНЗИСТОРАХ

Изобретение относится к запоминающим устройствам и может быть использовано в оптоэлектронных информационнопоисковых системах и системах обработки и распознавания символов.

Известен ассоциативный запоминающий элемент, содержащий активные и нагрузочные МДП вЂ транзисто, образующие статический триггер, реализующие элемент Неравнозначность", один из которых работает в режиме ключа, и два управляющих транзистора. Затворы управлчющих транзисторов подключены к соответствующим плечам триггера, истоки — к разрядным шинам, стоки — к числовой шине, соединенной с затвором ключевого транзистора, исток которого подключен к общей шине элемента pl).

Элемент имеет большое число транзисторов, что усложняет его конструк- Эт цию и приводит к потере площади кристалла в случае интегрального исполнения матрицы таких элементов. Кроме того, в элементе отсутствует возможность оптической записи информации, что не позволяет записывать информацию в матрицу элементов параллельно, страницами и снижает скорость обработки информации.

Наиболее близким к предлагаемому изобретению является ассоциативный запоминающий элемент, содержащий активные и нагрузочные транзисторы, образующие статический триггер, транзисторы, образующие элемент "РавнозначНость", управляющие транзисторы, фотодиод, шину нулевого потенциала, pasрядные шины, шину результата, число-.. вую шину, шину запоминания состояния триггера, шину питания (2).

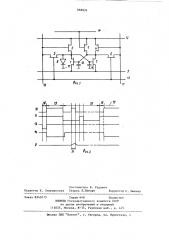

Затворы первого и второго транзиси ° I торов элемента Равнозначность соединены с разрядными шинами, стоки — с шиной результата, а истоки — со стоками транзисторов, истоки которых соединены с шиной нулевого потенциала, а затворы — соответственно с выходами триггера, затворы управляющих тран4 41 соединены с шиной 9 результата, сток транзистора 1 соединен с анодом @отодиода 8, истоком транзистора 3 и стоком транзистора 5, сток транзистора 2с истоками транзисторов 4 и 7 и стоком транзистора 6, а затворы переключающих транзисторов 1 и 2 включены в перекрестную обратную связь в триггере, Затворы транзисторов 3 и 4 соединены соответственно с разрядными шинами 10 и

11 а стоки — с шиной 12 питания. Затворы управляющих транзисторов 5 и 6 соединены с числовой шиной 13, исток транзистора 5 соединен с разрядной шиной !О, исток транзистора 6 — с pasрядной шиной 11. Затворы транзистора

7 соединены с шиной 14 запоминания, а сток подключен к шине 12 питания.

Через 15 и 16 обозначены паразитные конденсаторы затворов TpaH3HcTop4gl 1 и 2. Катод фотодиода 8 соединен с шиной 17 нулевого потенциала.

Элемент работает следующим образом.

Для предустановки триггера — участок диаграммы 18 (см. фиг. 2) — на разрядные шины 10 и 11 подаются напряжения, соответствующие парафазному коду бита, который необходимо записать в триггер по электрическому каналу, Затем на шину 13 подается адрес-. ный разрешающий сигнал, и информация на шинах 10 и 11 переписывается в триггер.

Для оптической записи — участок диаграммы 19 (см. фиг. 2) — фотодиод освещается светом, интенсивность которого соответствует оптическому состоянию "0" или "1", при этом на шины 10 и 11 подается нулевой потенциап и нагруэочные транзисторы 3 и 4 запираются. Элемент представляет собой в этом режиме усилительный каскад с переключающим 2 и нагрузочным 7 транзисторами, охваченный положительной обратной связью на транзисторе 1. По истечении времени экспоэии света на фотодиоде, в течение которого конденсатор фотодиода разряжается под действием света, одновременно включаются нагрузочные транзисторы 3 и 4 (участок 20 на фиг. 2) и затем отключается иагрузочный транзистор 7, триггер запоминает записанную информацию, обеспечивая на конденсаторах 15 и 16 ло" гические уровни напряжения в соответствии с уравнением:

Э x + y, где х двоичное значение оптического бита;

3 86883 зисторов соединены с числовой шиной, а стоки — соответственно с выходами триггера. Анод фотодиода подключен к стоку одного из управляющих транзисторов.

При переходе этого элемента из режима оптической эаниси к режиму запоминания коммутируется один из нагрузочных НДН-транзисторов, что приводит к несимметричной помехе через паразит- lð ный конденсатор, образуемый затвором и стоком транзистора в плечах триггера и снижает фоточувствительность, а следовательно, и надежность элемента.

Кроме того, элемент содержит больmoe число транзисторов, что увеличивает габариты.

Цель изобретения — повышение надежности и упрощение элемента, Поставленная цель достигается тем, что в ассоциативный запоминающий элемент на МДП-транзисторах, содержащий управляющие транзисторы, истоки которых соединены с соответствующими разрядными винами, затворы — с числовой виной, фотодиод, анод которого подключен к стоку одного из управляющих транзисторов, а катод — к шине нулевого потенциала, шину питания и шину эайоминания, переключающие транзисторы, истоки которых подключены к шине результата, стоки — к истокам соответствующих нагрузочных транзисторов, причем затвор каждого из переключающих транзисторов соединен со стоком смежного переключающего транзистора, стоки управляющих транзисторов подключены к истокам соответствующих нагрузочных транзисторов, введен дополнительный нагрузочный транзистор, исток которого соединен со стоком другого

4р управляющего транзистора, сток — с шиной питания, затвор — с шиной запоминания, затворы основных нагрузочных транзисторов соединены с соответствукш1ими разрядными шинами, стоки — с ши- ной литания, а истоки переключающих транзисторов соединены с шиной результата.

На фиг, 1 изображена принципиальная схема ассоциативного запоминающе/

ro элемента; на фиг.. 2 — диаграмма операционного цикла элемента.

Элемент содержит переключающие 1 и 2, негруэочные 3 и 4 ИД&транзисторы, образующие статический триггер, 55 управляющие транзисторы 5 и 6, дополнительный нагрузочный транзистор 7 и фотодиод 8. Истоки транзисторов I и 2

868834

Формула изобретения

R = 3Z + 3Z

25 у — двоичное .значение кода пред- установки;

+ — знак логического сложения, Далее, если на разрядные шины 10 и

11 подается парафазное значение кода запроса z и «z, (участок 21 на фиг. 2), то одно из плеч триггера проводит ток (если есть совпадение кода z и информации в триггере) или оба плеча не проводят тока (если нет совпадения кода

z н информации в триггере). На этом такте, который длится порядка 0,51 мкс, информация хранится на конденсаторах 15 и 16. Снятие кода запроса

2 переводит нагруэочные транзисторы 3 и 4 в проводящее состояние и обеспечивает регенерацию логических уровней на конденсаторах 15 и 16.

Таким образом, если регистрировать ток в шине результата 9, то его значение будет соответствовать значению логической функции равнозначность: между содержимым триггера J и кодом запроса г.

Исследования экспериментальной матрицы размерностью 16 х 16, составленной из описанных элементов, показывают, что чувствительность по оптическому входу составляет 1-2 .IO,Цж/бит против 5 10 Дж/бит (в прототипе 2).

Упрощение конструкции элемента до35 стигается уменьшением числа транзисторов до 7 (против I O в прототипе) .

Кроме того эа счет исключения элемента "Равнозначность" потребляемая мощность уменьшается не менее чем в

5 раз.

Ассоциативный запоминающий элемент на ИДП-транзисторах, содержащий управляющие транзисторы, истоки которых соединены с соответствующими разрядными шинами, затворы — с числовой шиной, фотодиод, анод которого подключен к стоку одного из управляющих транзисторов, а катод — к шине нулевого потенциала, шину питания и шину запоминания, переключающие транзисторы, истоки которых подключены к шине результата, стоки — к истокам соответствующих нагрузочных транзисторов, причем затвор каждого из переключающих транзисторов соединен со стоком смежного переключающего транзистора, стоки управляющих транзисторов подключены к истокам соответствующих нагрузочных транзисторов, о т л и ч а ю щ и й— с я тем, что, с целью повышения надежности и упрощения элемента, он содержит дополнительный нагрузочный транзистор, исток которого соединен со стоком другого управляющего транзистора, сток — с шиной питания, затвор — с шиной запоминания, затворы основных нагрузочных транзисторов соединены с соответствукщими разрядными шинами, стоки — с шиной питания, а, истоки переключающих транзисторов соединены с шиной результата.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ф 441592, кл. G ll С 15/00, 1972.

2. Авторское свидетельство СССР по заявке У 2644733/18-24, кл. G II С 15/04, 1978 (прототип).

868834 и.2

Заказ 8340/75

Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР ло делам иэобретений и открытий

ll3035, Москва, Ж-35, Рауиская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель В. Рудаков

Редактор .Е. Спиридонова Техред Л.Пекарь Корректор С. Шекмар