Ячейка памяти для регистра сдвига

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

А. В. Фомичев, М. Ф. Пономарев и И. И. Бычков

Таганрогский радиотехнический институт им. В.Д. Калмыкова

l (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА

Изобретение относится к вычислительной технике и может быть использовано при построении регистров сдвига.

Известен регистр сдвига, ячейка которого содержит два триггера с непосредственной связью на двухколлекторных п-р-и-транзисторах и два двухколлекторных р-п-р"транзистора; причем эмиттеры п-р-п- и базы р-п-р-транзис" торов соединены с общей шиной. Эмиттеры одного и другого р-п-р-транзис10 торов соединены соответственно с одной и другой шинами питания, их коллекторы соединены с соответствующими базами четырех п-р-п.-транзисторов

tS триггеров. В каждом из двухколлекторных п-р,п-транзисторов один коллектор используется .для образования.перекрестной триггерной связи, а второй— для сВН3Н между тркггерами. Входные шины соединены с базами п-р-и-транзисторов первого триггера, выходные шины соединены со вторыми коллекторами п-р-и-транзисторов второго триггера, Описанный регистр построен полностью на транзисторах, не содержит резисторов и конденсаторов, обеспечивает высокую степень интеграции элементов на кристалле и низкую потребляемую мощность 11, Недостатками регистра являются ниэ" кое быстродействие и большая площадь, занимаемая на кристалле микросхемы.

Известен также регистр сдвига, ячейка которого содержит два триггера с непосредственной связью на двухколлекторных п-р-п-транзисторах и два двухколлекторных р-п-р-транзистора.

Схема соединения элементов такая же, как и у предыцущего устройства (2).

Недостатками регистра являются низкое быстродействие и большая вамимаемая площадь.

Наиболее близким к предлагаемому является ячейка памяти для интегрального двухтактного кваэистатического регистра сдвига. Указанная ячейка содержит два триггера с непосредствен868836

55 ными связями на двухколлекторных п-р-п-транзисторах, эмиттеры которых соединены с общей шиной; а также два двухколлекторных р-п-р-транзистора, эмиттеры которых соединены с одной и другой шинами питания, базы " с общей шиной, а коллекторы — с базовыми областями п-р-п-транзисторов соответственно первого и второго триггеров. В каждом из п-р-п-траизисторов один из 10 коллекторов используется для образования перекрестной связи двух п-р-п-транзисторов в триггере полуразряда, а другой — для связи между триггерами полуразрядов и между ячейками в регистре. При реализации ячейки в ИС с инжекционным питанием коллекторные области р-r.-p-транзисторов совмещены с соответствующими базовыми областями п-р-п-транзисторов, а эмиттерные области п-р-п-транзисторов и базовые области р-и-р-транзисторов совмещены общей полупроводниковой п-области— подложке. Ячейка технологична, обладает высокой плотностью компоновки элементов на кристаллле микросхемы при малой потребляемой мощности (3).

Основными недостатками ячейки являются низкое быстродействие и большая занимаемая площадь, обусловленные использованием в каждом полуразряде триггеров на двухколлекторных п-р-п-транзисторах.

Цель изобретения — повышение степени интеграции ячейки памяти и ее

35 быстродействия.

Поставленная цель достигается тем, что в ячейку памяти для регистра сдвига, содержащую первый и второй двухколлекторные п-р-п-транзисторы, эмит40 теры которых соединены с шиной нулевого потенциала, первый и второй двухколлекторные р-п-р-,транзисторы, эмиттеры которых соединены соответственно с первой и второй шинами питания базы первого и второго двухколлекторных .

45 р-п-р-транзисторов подключены к шине нулевого потенциала, база первого двухколлекторного и-р-п-транзистора соединена со входом ячейки памяти и с первым коллектором первого двухколлекторного р-п-р-транзистора, второй коллектор которого соединен с первым коллектором первого двухколлекторного п-р-п-транзистора, второй коллектор которого соединен с базой второго двухколлекторного п-р-и-транзистора и с первым коллектором второго двухколлекторного р-п-р-транзистора, первый коллектор второго двухколлекторного п-р-и-транзистора соединен с выходом ячейки памяти, введены первый и второй п-р-п-транзисторы, эмиттеры которых соединены с шиной нулевого потенциала, база первого п-р-п-транзистора подключена ко второму коллектору второго двухколлекторного р-и-р-транзистора, ко второму коллектору второго двухколлекторного и-р-и-транзистора и к коллектору второго и-р-п-транзистора, база которого соединена с первым коллектором первого двухколлекторного п-р-п-транзистора, коллектор первого п-р-п-транзистора соединен с базой второго двухколлекторного и-p — п-транзистора.

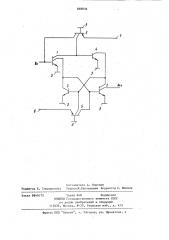

На чертеже представлена электрическая схема ячейки памяти.

Она содержит двухколлекторные п-р-п-транзисторы и 2, и — р-п-транзисторы 3 и 4, двухколлекторные р-и-р-транзисторы 5 и 6, шины 7 и 8 питания, шину 9 нулевого потенциала.

При реализации предлагаемой ячейки памяти в составе регистровых ИС с ин— жекционным питанием с целью увеличения степени интеграции элементов на кристалле микросхемы коллекторные области р-и-р-транзисторов совмещены с соответствующими базовыми областями п-р-п-транзисторов, а эмиттерные области.п-р-п-транзисторов и базовые области р-п-р †транзистор совмещены в общей полупроводниковой п-области— подложке.

Ячейка памяти работает следующим образом.

При воздействии первого тактового импульса на шину 7 транзистора 5 включен и задает базовые токи транзисторов l и 4 первого полуразряда ячейки.

Если при этом на входе ячейки памяти подцерживается высокий уровень напряжения (логическая "1"), то транзистор

1 включен, а транзистор 4 — выключен, так как его базовый ток отводится в коллектор транзистора 1. Емкость эмиттерного перехода транзистора при этом заряжена, а транзистора 4 — разряжена. За счет заряженной емкости транзистора 1 это состояние поддерживается при переключении тактовых импульсов, во время которого напряжение на шине 7 уменьшается, а на шине 8— увеличивается до уровня, при котором включается транзистор 6 и задает базовый ток в триггерные транзисторы 2 и

868836

3 второго полуразряда ячейки. Поддер- живаемый в открытом состоянии транзистор 1 при этом отводит базовый ток транзистора 2, поэтому транзисторы 2 и 3, на которых собран триггер, включится в состояние, при.котором транзистор 3 открыт, а транзистор 2 — закрыт. При повторном переключении тактовых импульсов на коллекторах закрытого транзистора 2 и выходе ячейки to памяти будет зафиксирована логическая "1".

Таким образом, происходит передача ячейкой памяти высокого уровня напряжения. Аналогичным образом будет происходить передача и низкого уровня (логический "0").

Известная ячейка памяти содержит четыре двухколлекторных и-р-п-транзистора, образующих два триггера с непосредственными связями. Предлагаемая ячейка памяти содержит триггерный полуразряд и динамический полуразряд, построенный на двух коллекторных и двух одноколлекторных п-р-и-транзис- 2 торах, что приводит к уменьшению площади ячейки по сравнению с прототипом. Кроме того, в известной ячейке памяти используется парафазная, а в предлагаемой ячейке памяти — однофаэная передача информации между разрядами, что приводит к сокращению площади, занимаемой металлическими шинами. Указанные факторы обеспечивают уменьшение площади, занимаемой пред35 лагаемой ячейкой, на 30-50Е по сравнению с известной.

Использование в известной ячейке памяти четырех двухколлекторных и-р-п40

-транзисторов, кроме увеличения площади ячейки, приводит к снижению ее быстродействия за счет дополнительных задержек включения в этих транзисторах по второму коллектору. Сокращение числа коллекторов в двух и-р-и-тран45 зисторах приводит к исключению в них ! указанных задержек, чем и обусловлено повышение быстродействия предлагаемой ячейки в среднем в 2 раза по сравнению с известной.

Формула изобретения

Ячейка памяти для регистра сдвига содержащая первый и второй двухколлекторные и-р-и-тр нэисторы, эмиттерш которых соединены с шиной нулевого потенциала, первый и второй двухколлекторные р-п-р-транзисторы, эмиттеры которых соединены соответственно с первой и второй шинами питания, базы первого и второго двухколлекторных р-и-р-транзисторов подключены к шине нулевого потенциала, 6asa первого двухколлекторного п-р-п-транзистора соединена со входом ячейки памяти и с первым коллектором перв го двухколлекторного р-п-р-транзистора, второй коллектор которого соединен с первым коллектором первого двухколлекторного п-р-п-транзистора, второй коллектор которого соединен с базой второго двухколлекторного п-р-и-транзистора и с первым коллектором второго двухколлекторного р-п-р-транзистора, первый коллектор второго двухколлекторного п-р-и-транзистора соединен с выходом ячейки памяти, о т л и ч а ю щ а" я с я тем, что, с целью повышения степени интеграции ячейки памяти и ее быстродействия, в нее введены первый и второй п-р-п-транзисторы, эмиттеры которых соединены с шиной нулевого потенциала, база первого и-р-и-транзистора подключена ко второму коллектору второго двухколлекторного р-п-р-òðàíçèñòîðà, ко второму коллектору второго двухколлекторного п-р-и-транзистора и коллектору второго п-р-п-транзистора, база которого соединена с первым коллектором первого двухколлекторного п-р-п-транзистора, коллектор первого и-р-п-транзистора соединен с базой второго двухколлекторного п-р-п-транзистора.

Источники информации, принятые во внимание при экспертизе

I. Патент Франции 9- 2131960,,кл. G 11 С 19/00, 1972.

2. Заявка Великобритании Ф 1333193, кл. G 11 С 19/00, 1973.

3. J, Sol i f-State Electronics 1973, 16, У 9, рр. 1007-1010 (прототип).

868836

Заказ 8340/75

Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель А. Воронин

Редактор Е. Спиридонова Техред Ж,Кастелевич Корректор С, Шекмар