Запоминающее устройство с контролем

Иллюстрации

Показать всеРеферат

Союз Советсиин

Соцналистичесиик

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6! ) Дополнительное к авт. свид-ву (22) Заявлено 10.01. 80 (2! ) 2869338/18-24 с присоединением заявки № (23) Приоритет (51)NL. Кл.

G 11 С 29/00

Гееударстеенный квинтет

СССР но делает нэобретеннй н открытнй

Опубликовано 30 .09 81. Бктллетень № 36

Дата опубликования описания 01.10.81

I (53) д К 681 . 327. .6 (088. 8) (72) Авторы изобретения

А.К. Култыгин, Н.И. Вариес, Г.Х. Власова и А.Д. Булгаков (71) Заявитель (54) ЗАПОМИНАКМЦЕЕ УСТРОЙСТВО С КОНТРОЛЕМ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке запоминающих устройств ЦВМ и систем хранения и переработки информации.

Известно запоминающее устройство с исправлением ошибок, содержащее блок памяти, соединенный с регистром числа, блок контроля, соединенные с триггером маски, блок инвертирова!

О ния (1) .

Блок контроля обнаруживает ошибки при считывании числа, следующим сразу

1$ после записи. В случае обнаружения ошибок число инвертируется и вновь записывается в блок памяти вместе с дополнительным разрядом, содержимое которого указывает на инверсию числа.

При воспроизведении информации исправление ошибок производится вторичным инвертированием числа в соответствии с содержимым дополнительного разряда.

Недостатком этого запоминающего устройства является низкое быстродействие из-за повторных циклов записи и считывания в процессе обнаружения ошибок.

Наиболее близким к предлагаемому является запоминающее устройство с исправлением ошибок, содержащее основной и дополнительные блоки памяти, адресные входы которых соединены с блоком выборки адресов, регистр числа, блок контроля, входы которого соединены с выходами основного блока памяти, а первый выход — с управляющим входом регистра числа, дешифратор, а также схемы "И" — по числу разрядов основного блока памяти, причем, вьтходы дополнительного блока памяти соеди" иены с входами дешифратора, выходы которого соединены с первыми входами соответствующих схем И, а второй вход блока контроля соединен со вторыми

„входами всех схем ИЮ7.

8844

Код числа хранится в основном бло ке памяти. Дополнительный блок памяти хранит номера разрядов, где имеются дефектные запоминающие элементы в основном блоке памяти, При воспроизведении информации, в случае обнаружения ошибки блоком контроля, происходит ее исправление в регистре числа путем инвертирования ошибочного раз ряда в соотватствии. с номером дефектного зааомииа1ацего элемента, считанного из д1жолиительного блока памяти.

Недостатком данного запоминающего устройства является низкая надежность, так как не обнаруживаются отказы запоминающих элементов основного блока ,памяти, происходящие в процессе эксплуатации запоминающего устройства.

Цель изобретения — повышение надежности запоминающего устройства.

Поставленная цель достигается тем, что в запоминающее устройство с контролем, содержащее основной накопитель, адресные входы которого подключены к выходам адресного блока и к адресным входам первого дополнительного накопителя, информационные входы — к выходам информационного регистра и к первым входам первого блока контроля, выходы основного накопителя подключены ко входам второго блока контроля и к информационным входам информационного регистра, дополнительный информационный вход основного накопителя подключен к выходу первого блока контроля и дешифратор, входы которого подключены к выходам первого дополнительного накопителя, а выходы ." к первым управляющим входам информационного регистра, допойиительно введены второй дополнительный накопитель, адресные входы которого подключены к выходам адресного блока, а выход — ко второму входу первого блока контроля, и третий блок контроля, первый вход которого подключен к дополнительному выходу основ ного накопителя, второй .вход — к выходу второго блока контроля, а первый и второй выходы — соответственно ко второму и к третьему управляющим входам информационного регистра, третьи входы первого блока контроля подключены к выходам дешифратора.

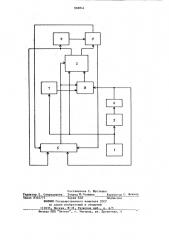

Ra чертеже представлена блок-схема пред мгаемого запоминающего устройства с коитролем.

Запоминающее устройство содержит адресный блок 1, основной накопи5

4 тель 2, первый дополнительный накопитель 3, второй блок 4 контроля, информационный регистр 5, дешифратор .6, второй дополнительный накопитель 7, первый блок 8 контроля, третий блок 9 контроля.

В основном накопителе 2 допускается некоторое количество дефектных запоминающих элементов, но не более одного по каждому адресу, и некоторое количество случайных сбоев или систематических отказов запоминающих элементов, возникших в процессе эксплуатации. Адреса дефектных запоминающих элементов заранее известны.

По этим адресам в первом дополнительном накопителе 3 хранятся номера дефектных запоминающих элементов. Дефекты запоминающих элементов, которые допускаются в основном накопителе 2,могут быть двух типов: выход запоминающего эйемента постоянен и равен 1 и выход запоминающего элемента постоянен и равен О. Типы дефектов запоминающих элементов заранее известны и хранятся в одноразрядном втором дополнительном накопителе 7. Первый 3 и второй 7 дополнительные накопители могут быть выполнены в виде одного блока постоянной памяти и не содержат дефектных элементов.

Запоминающее устройство работает следующим образом., Адресный блок формирует код адреса, который одновременно поступает на адресные входы основного 2 и двух дополнительных 3 и 7 накопителей.

В режиме записи код числа из информационного регистра 5 поступает на числовые входы основного накопителя 2 и одновременно на первый блок 8 контроля. На первый блок 8 контроля поступает также код типа дефекта из второго дополнительного накопителя- 7.

Номер дефектного разряда из первого дополнительного накопителя 3 поступает на входы дешифратора 6, при этом возбуждается одна из его выходных шин.

Сигнал с возбужденной шины дешифратора 6 поступает на первый блок 8 контроля. По сигналу с возбужденной шины дешифратора 6 первый блок 8 контроля производит сравнение типа дефекта запоминающего элемента, с информацией, которая записывается в этот дефектный запоминающий элемент. В случае несравнения первый блок 8 контроля вырабатывает сигнал, соответствующий логической "!", которая записывается

Формула изобретения

20. Источники информации, принятые во внимание при экспертизе

5 8688 в дополнительный разряд основного накопителя 2 одновременно с записью числа. В случае сравнения или в случае отсутствия дефектного запоминающего элемента по выбранному адресу в дополнительный разряд основного накопителя 2 записывается "0".

В основной накопитель 2 информация записывается вместе с контрольным кодом, например, но модулю 2.

В режиме считывания второй блок 4 контроля производит проверку правильности числа, считанного из основного накопителя 2. Сигнал со второго блока 4 контроля одновременно с содержимым дополнительного разряда основного накопителя 2 поступают на соответст вующие входы третьего блока 9 контроля. В случае отсутствия ошибок, сигнал с третьего блока 9 контроля поступает на второй управляющий вход информационного регистра S, разрешая вьдачу числа. В случае обнаружения неисправимой ошибки, сигнал с третьего блока 9 контроля запрещает выдачу числа. В том случае, если ошибка исправима, сигнал с возбужденной шины, дешифратора 6 поступает на первые управляющие входы информационного регистра 5, выполненного, например, на триг- 1б герах со счетными входами, и по управляющему сигналу с третьего блока контроля 9 происходит инвертирование информации в ошибочном разряде, а затем выдача скорректированного числа.

Предлагаемое устройство обладает более высокой надежностью, по сравнению с известными, т.е. позволяет не только исправить ошибки, вызыванные наличием технологических дефектов в ос40 новном блоке памяти, но и обнаружить неисправности, возникающие в процессе эксплуатации запоминающего устройства, что повышает достоверность информации, поступающей в процессор либо другие средства обработки инфор45 мации.

Запоминаннщее устройство с контролем, содержащее основной накопитель, адресные входы которого подключены к выходам адресного блока и к адресным входам первого дополнительного накопителя, информационные входы — к выходам информационного регистра и к первым входам первого блока контроля, выходы основного накопителя подключены ко входам второго блока контроля и к информационным входам информационного регистра, дополнительный информаци" онный вход основного накопителя подключен к выходу первого блока контроля, и дешифратор, входы которого подключены к выходам первого дополнительного накопителя, а выходы — к первым управляющим входам информационного ре" гистра, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены второй дополнительный накопитель, адресуые входы которого подключены к выходам адресного блока,.а выход — ко второму входу первого блока контроля, и третий блок контроля, первый вход которого подключен к дополнительному выходу основного накопителя, второй вход— к выходу второго блока контроля, а первый и второй выходы — соответственно ко второму и к третьему управляющим входам информационного регистра, третьи входы первого блока контроля подключены к выходам дешифратора.

1. Патент США !I9 376807Т, кл. Q 11 С 29/00, 1976.

2. Авторское свидетельство СССР ,по заявке ll 2605)69/18-24, кл. G 11 С 29/00, 13.04.78 (прото" тип) .

868844

Составитель С. Шустенко

Репактор Е. Спиридонова Техред М.Голинка Корректор С Шекмар

Заказ 8340775 Тираж 648 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 l3035 Москва Ж-35 Ра ская наб. д. 4/5 т л т P

2.

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4