Д-триггер

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

„„868982 (61) Дополнительмое к авт. саид-ву— (22) Заявлено 04.01ВО (21) 2863407/18-21 с присоединением заявки Но— (23) Приоритет—

Опубликовано 30.0981. Бюллетень М

Дата опубликования описания 30.0981 (51)М. Кл.

Н 03 К 3/286

Государственный комитет

СССР

Ilo делам изобретений и открытий (53) УДК 621.375. . 68 3 (0 88". 8 "1-"-- =

f (72) Авторы изобретения A.H. Гаршин, JI.II.Äîìíèí, Ю, Г. Верон и B, H. Никишин

Опытно-конструкторское бюро специального физического (71) Заявитель приборостроения при Воронежском политехническом институте (54) 0-ТРИГГЕР

Недостатком известного устройства является низкая помехоустойчивость из-за малой величины перепада логических уровней.

Цель изобретения — увеличение помехоустойчивости триггера °

Изобретение относится к импульсной технике.

Известен тактируемый О-триггер, состоящий из управляющего вентиля, переключателя тока с тактовым входом, источника постоянного тока и источника опорных напряжений(11.

Недостатком известного триггера является низкая надежность из-за большой сложности.

Известен также триггер, содержащий бистабильный элемент на двух транзисторах, эмиттеры которых соединены между собой, а коллекторы через резисторы соединены с источником питания, управляющий транзистор, коллектор которого соединен с коллекторром одного из транзисторов бистабильного элемента, база соединена с источниксу входных импульсов, а эмиттер соединен со вторым эмиттером второго транзистора бистабильного элемента, переключатель тока на двух транзисторах, коллекторы которых соединены соответственно с эмиттерами транзисторов бистабильного элемента и управляющего транзистора, базы подключены к генераторам тактовых импульсов, а эмиттеры соединены с источником поc òîÿííîão ToKa(2).

Для достижения постанленной цели н О-триггере, содержащем выходной транзистор, эмиттер которого подключен к первому эмиттеру входного транзистора, коллектор которого подключен к базе выходного транзистора и через резистор к общей шине, первый и второй эмиттеры входного транзистора подключены соответственно к коллекторам транзисторов переключателя тока, эмиттеры которых подключены к источнику тока, база первого транзис2О тора переключателя тока подключена к тактовому нходу триггера, база входного транзистора подключена к перному источнику опорного напряжения, а второй эмиттер — к информационному входу, база второго транзистора переключателя тока подключена ко второму источнику опорного напряжения, коллектор выходного транзистора подключен к общей шине, а дополнительные эмит30 теры — к выходам триггера.

868982

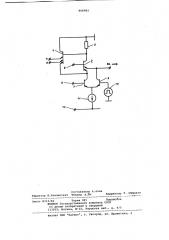

На чертеже представлена принципиальная схема О-триггера.

База выходного транзистора 1 соединена с коллектором входного транзистора 2 и через резистор 3 соединена с коллектором транзистора 1 и с шиной нулевого потенциала, дополнительные эмиттеры транзистора 1 соединены с выходами устройства 4 и 5, ба.— за входного транзистора 2 соединена с первым источником 6 опорного напряжения, коллектор второго транзисто ра 7 переключателя тока соединен с эмиттерами транзисторов 1 и 2, а его база — co вторым источником 8 опорного напряжения, коллектор перво""о транзистора 9 переключателя тока «5 соединен с эмиттером транзистора 2 и со входом информации, а его база с источником 10 тактового сигнала, эмиттеры транзисторов 9 и 7 соединены между собой и через источник 11 gp тока с шиной 12 питания.

Устройство работает следующим образом.

Если на базу первого транзистора

9 переключателя тока подан логичес- 25 кий "0", триггер находится в режиме хранения информации. 1ок источника 11, течет через открытый второй транзистор 7 переключателя тока, входной и выходной транзисторы 1 и 2 образуют триггер Шмидта, который может находиться в двух устойчивых состояниях.

В нулевом состоянии открыт входной транзистор 2, его коллекторный ток понижает потенциал на базе выходного транзистора 1.

Напряжение коллектор-эмиттер входного транзистора 2 в этом режиме выбирается путем подбора номинала резистора 3 равным 0,4В. Это напряжение достаточно для надежного запира- 4О ния транзистора 1 и не вызывает заметного насыщения входного транзистора 2. В этом режиме на выходах

4 и 5 присутствует уровень логического нуля. В единичном состоянии входной транз««стор 2 закрыт, потенциал связи выходного транзистора 1 близок к нулевому, на выходах 4 и 5 находится уровень логической единицы.

В режиме хранения информация, поступающая .на вход устройства, не изменяет его состояния, т.е. первый .транзистор 9 заперт, и заперт второй эмиттер вхог «ого транзистора 2, соединенный со входом информации.

Ес«ли на базу первого транзистора 9 пере!Ь«ючателя тока подана логическая "1", триггер находится в режиме приема информации. Ток источника 11 тока течет через открытый первый транзистор 9 переключателя тока. 6Î

При подаче на вход информации логического нуля с выхода .подобного устройства второй эмиттер входного транзистора 2 открыт. Ток течет по цепи: шина нулевого потенциала резистор 3 — коллектор- эмиттер входного транзистора 2 — коллектор-эмиттер первого транзистора 9 переключателя тока — источник 11 тока-шина 12 питания.

При этом на базе выходного транзистора 1 находится низкий потенциал и при переключении триггера в режим-хранения в нем записывается "0".

При подаче на вход информации логической единицы второй эмиттер входного транзистора 2 заперт, ток коллектора равен нулю, потенциал коллектора равен нулю и при переключении триггера в режим хранения в нем записывается "1".

Подключение базы входного транзистора 2 к источнику 8 опорного напряжения, имеющему потенциал, равный минус 0,3 В, позволяет получить величину перепада выходных уровней 0,6-0,8В, исключая режим насыщения транзисторов.

Подключение дополнительных эмиттеров выходного транзистора 1 к выходам

4 и 5 позволяет оптимальным образом реализовать логическую функцию расширения по выходу.

Подключение второго эмиттера входного транзистора 2 ко входу информации, а базы второго транзистора 7 переключателя тока ко второму источнику 8 опорного напряжения, имеющему потенциал, равный минус 1 В, позволяет согласовать по уровню вход информации и вход такта с выходом устройства ° формула изобретения

D-триггер, содержащий выходной транзистор, эмиттер которого подключен к первому эмиттеру входного транзистора, коллектор которого подключен к базе выходного транзистора и через резистор к общей шине, первый и второй эмиттеры входного транзистора подключены соответственно к коллекторам транзисторов переключателя тока„ эмиттеры которых подключены к источнику тока, база первого транзистора переключателя тока подключена к тактовому входу триггера, о тл и ч а ю шийся тем, что с целью увеличения помехоустойчивости, база входного транзистора подключена к первому источнику опорного напряжения, а второй эмиттер — к информационному входу, база второго транзистора переключателя тока подключена ко второму источнику опорного напряжения, коллектор выходного транзистора подключен к общеи шине, а дополнительные эмиттеры — к выходам триггера.

Источники информации, принятые во внимание при экспертизе

1. The integrated Circuit Date

Book Supp!ament, Motoroia Semiconductor Products !nc. 3, 1969, р. 2-15.

2. Авторское свидетельство CCCP

9 587607, кл. Н 03 К 3/286, 1 978 (прототип).

868982

Составитель A.ßíîâ

Редактор Л.Пчелинская Техред A.Ач Корректор H Швыдкая

Заказ 8353/82 Тираж 991 Подписйое

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, .4