Делитель частоты

Иллюстрации

Показать всеРеферат

ОП ИСАН

ИЗОБРЕТЕН

К АВТОРСКОМУ СВИДЕТЕ,ее

Союз Советсиих

Социалистических

Респубпни (61) Дополнительное к авт. саид-ву-(22)Заявлено! 4.01.80 {2I) 2869092 с присоединением заявки J4— (23) Приоритет—

Опубликовано 30.09.81. Бюллет (осударетесииый комитет

СССР ао деизм изеЬретеиий и открытий

Дата опубликования описания (72) Автор изобретения

Ю. В. Смирнов (7l ) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТ01г1

Изобретение относится к импульсной технике.

Оно предназначено для использования в устройствах вычислительной техники, а также в устройствах автоматики и телемеханики.

Известен делитель частоты, содержащий счетчик, выход которого соединен со входом дешифратора, инвертор, вход которого подключен к входной ши10 не делителя, и триггер, счетный вход которого соединен с выходом дешифратора, установочный вход с выходом инвертора, а выход — с шиной сброса счетчика, счетный вход которого под I j ключен к входной шине делителя (I ).

Недостатком этого делителя частоты является относительно низкая достоверность функционирования.

Наиболее близким техническим решением к предлагаемому является делитель частоты, содержащий счетчик, дешифратор, триггер и >,нвертирующий элемент, вход которого соединен с входом делителя частоты, а выход инвертируюшего элемента соединен с входом сброса триггера, вход установки и выход которого соединены соответственно с выходом дешифратора и входом сброса счетчика, выходы которого соединены с входами дешифратора f2).

Недостатком этого делителя частоты является относительно низкая достоверность функционирования.

Цель изобретения — повышение достоверности функционирования.

Поставленная цель достигается тем, что в делителе частоты, содержащем счетчик, дешифратор, тригт ер и ннвертирующий элемент, вход которого соединен с входом делителя частоты, а выход инвертирующего элемента соединен с входом сброса триггера, вход установки и выход которого соединены соответственно с выходом дешифратора и входом сброса счетчика, выходы которого соединены с входами дешифратора, нулевой выход дешифрато869055

Формула изобретения

Делитель частоты, содержащий счетчик, дешифратор, триггер и инвертирующий элемент, в .од которого соединен с входом делителя частоты, а выход инвертирующего элемента соеди30 нен с входом сброса триггера, вход установки и выход которого соединены соответственно с выходом дешифратора и входом сброса счетчика, выходы которого соединены с входами дешифратора, отличающийся тем, что, с целью повышения достоверности функционирования, нулевой выход г. дешифратора соединен с управляющим входом инвертирующего элемента, а счетный вход счетчика соединен с

40 входом делителя частоты.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

4 В 612414, кл. Н 03 К 23/00, 1977. ра соединен с управляющим входом инвертирующего элемента, а счетный вход счетчика соединен с входом делителя частоты.

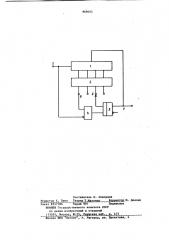

На чертеже показана структурная схема делителя частоты.

Делитель частоты содержит счетчик 1, дешифратор 2, триггер 3 и инвертирующий элемент 4, вход которого соединен с входом 5 делителя частоты, а выход инвертирующего элемента 4 соединен с входом сброса триггера 3, вход установки и выход которого соединены соответственно с выходом дешифратора 2 и входом сброса счетчика 1, выходы которого соединены с входами дешифратора 2, нулевой выход дешифратора 2 соединен с управляющим входом инвертирующего элемента 4, а счетный вход счетчика 1 соединен с

20 входом 5 делителя частоты.

Делитель частоты работает следующим образом.

Входные импульсы с входа 5 делителя поступают по вход счетчика 1, который производит их подсчет. Счет входных импульсов продолжается до тех пор, пска на ра.-рядных шинах счетчика 1 не устанавливается код числа, соот.зетствующий выбранному коэффициенту деления. При этом на управляющем выходе 6 дешифратора 2, соединенным с входом триггера 3, появляется сигнал, по которому триггер 3 переходит в единичное состояние ° Сигнал с прямого выхода триггера 3 поступает на вход сброса счетчика 1 и на выходную шину 7. Это сигнал устанавливает счетчик 1 в нулевое состояние. После прихода счетчика 1 в нулевое состояние, на нулевом выходе 8 дешифратора 2 появляется сигнал единичного логического уровня, который поступае; на управляющий вход элемента 4. Если к этому моменту времени входной импульс делителя заканчивается, т.е. запрещающий сигнал исчезает, то на выходе элемента 4 появляется сигнал единичного логического уровня, который переводит триггер 3 в нулевое состояние. Если же к моменту установки счетчика 1 в нулевое состояние

4 входной импульс делителя не заканчивается, то сигнал н установку в нулевое состояние триггера 3 сформируется по окончании входного импульса, вызвавшего ус гановление в счетчике

1 кода, соответствующего выбранному коэффициенту деления. После перевода триггера 3 в исходное состояние прекращается обнуление счетчика 1 и заканчивается выходной импульс делителя.

В дальнейшем работа делителя повто-. ряется, в результате чего на выходной шине 7 появляются импульсы с частотой следования, пропорциональной частоте входных импульсов и обратно пропорциональной коэффициенту деления, значение которого определяется выбором соответствующего управляющего выхода 6 дешифратора 2.

2. Шурыгин И.Т., Новиков Л.Г.

Счетчики импульсов с коэффициентами счета, управляемыми с помощью двоичного кода.-"Приборы и системы управления", 1972, 11 6, с. 31, рис. 6 (прототип).

869055

Составитель О. Скворцов

Редактор E. Папп Техоед T.Èàòî÷ê ã Корректор M. Демчик

Заказ 8357/86 Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035> Москва Ж-35> Рабская наб.п 4 5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4