Устройство пересчета на три

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ ,ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советск мх

Соцналнстмческмк

Республик

<и869067 (i2) Авторы изобретеHHfl

В. П. Грибок и 10. Д. Ивасенко (7! ) Заявитель (51) УСТРОЙСТВО ПЕРЕСЧЕТА НА ТРИ

Изобретение относится к импульсной технике и может быть использовано в раз. личных устройствах автоматики и вычиолительной техники.

По основному авт. св. № 506132 известно устройство пересчета на три, выполненное по несимметричной схеме, содержащее шину запуска, троичный однофазный асинхронный установочный триггер и три вспомогательных триггера, каж10 дый из которых выполнен на двух логических элементах И-НЕ (ИЛИ-HE) с перекрестными обратными связями, причем выход логического элемента каждого вспомогательного триггера соединен со входом аналогичного элемента последующего вспомогательного триггера и с соответствующим установочным входом троичного однофазного асинхронного триггера, выходы двух логических элементов которого подключены ко входам вторых логических элементов соответствующих двух вспомогательных триггеров, вход второго логического элемента третьего вспомогательного

2 триггера соединен с выходом второго лс>гического элемента последующего вспомогательного триггера, а третьи входы первых -логических элементов всех вспомогательных триггеров подключены к шине запуска (11.

Данное несимметричное построение уст ройства определяет его достаточно широ-. кие функциональные возможности. Среди сигналов на выходах логических элементов этого устройства сушес вуют не только три сигнала, изменяющиеся (при выполнении устройства, например, на логических элементах И-НЕ) синфазно переднему фронту входного сигнала, но и один сигнал, меняющийся по заднему фронту входного сигнала. Это существенно облегчает построение счетных цепей на указанных устройствах.

Цель изобретения — повышение надежности работы за счет полного исключения состязаний в функционировании устройства.

Поставленная цель достигается тем, что в устройстве пересчета на три, со15

25

35 ются неизменными.

4О

50

55 держащем троичный однофазный асинхронный установочный триггер и три вспомогательных триггера, каждый из которых выполнен на двух логических элементах И-НЕ (ИЛИ-НЕ), четвертый вход первого логического элемента третьего вспомогательного триггера соединен с последующим выходом троичного однофазного - асинхронного установочного триггера.

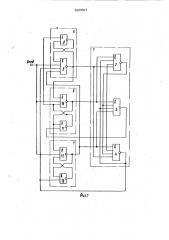

На фиг. 1 изображена схема устройства пересчета на три; на фиг. 2 — временные диаграммы его работы.

При этом номер диаграммы показывает выходной сигнал логического элемента ИНЕ с тем же номером. Аналогичным образом может быть выполнена и схема на элементах ИЛИ-HE.

Устройство содержит троичный однофазный асинхронный установочный триггер 1, выполненный на трех элементах

И-НЕ (или ИЛИ-НЕ) 2,3 и 4; три вхо- . да троичного однофазного асинхронного установочного триггера 1 подключены к выходам трех вспомогательных триггеров

5,6 и 7; триггер 5 выполнен на двух логических элементах И-НЕ(ИЛИ-НЕ): двухвходовом 8 к четырехвходовом 9, первые входы которь:х подключены к выходу другого элемента; триггер 6 выполнен на двух логическчх элементах И-НЕ(ИЛИ-НЕ) трехвходовом 0 и двухвходовом 11, первые входы которых подключены к выходу другого элемента; триггер 7 выполнен на двух логических элементах И-НЕ(ИЛИ-НЕ): трехвходовом 12 и двухвходовом 13; ко вторым входам логических элементов 9, 10 и 12 подключена шина запуска; выход элемента 9 соединен с третьим входом элемента 10, выход которого подключен к третьему входу элемента 12, выход которого соединен с .третьим входом элемента 9; выход элемента 3 подключен ко второму входу элемента 11, выход которого соединен со вторым входом элемента И-НЕ(ИЛИ-НЕ) 8; выход элемента 4 . подключен ко второму входу элемента

13 и к четвертому входу элемента 9.

Устройство работает следующим образом.

Пусть в рассматриваемый момент времени трончный однофазный асинхронный триггер 1 находится в состоянии, при ко ° тором на выходе его логических элементов 2 и 3 присутствуют единичные сигналы, а на выходе логического элемента 4 нулевой. Если в рассматриваемый момент на вспомогательные триггеры 5 6 н 7 не подаются входные сигналы, т.е. на шине запуска имеет место низкий нулевой смгнал, то на выходе обоих логических элементов 8 и 9 вспомогательного триггера 5 оказываются единичные сигналы, на выходе логического элемента 10 триг гера 6 присутствуют единичный сигнал, на выходе логического элемента 11 этого триггера — нулевой, на выходах обоих логических элементов 12 и 13 триггера .7

1 высокие единичные сигналы.

Рассматривается момент 4 начала первого импульса, на шине запуска. При этом формируется низкий сигнал на выходе эле мента И-HE 12. Низкий сигнал не может быть сформирован на выходе элементов

И-HE 10, так как на одном из его входов присутствует низкий сигнал с выхода элемента И-НЕ 11. Кроме того, на выходе элемента 9 не может сформироваться низкий сигнал, поскольку к его входу приложен нулевой уровень напряжения с .выхода элемента И-НЕ 4,После формирования низкого потенциала на выходе элемента И-НЕ 12 подтверждается высокий уровень сигналов на выходах элементов 9,13 и 3, и формируется высокий потенциал на выходе элемента И-НЕ 4.Его формирование не может изменить высоких выходных сигналов на элементах И-НЕ 3, 9 и

j.3, так как их поддерживает ранеесформированный низкий потенциал с выхода элемента И-НЕ 12, но после формирования высокого сигнала на выходе элемента

-HE 4 на всех вхоцах элемента И-HE

2 оказываются высокие сигналы, и на выходе этого логического элемента формируется низкий .игнал. Остальные сигналы на выходах логических элементов остаПо окончании первого входного импульса (момент 4 g) ко входа> элементов ИНЕ 9,10 и 12 оказывается приложенным низкий входной сигнал, который поддерживает высокие сигналы на выходах элементов И-НЕ 9 и 10 и устанавливает высокий сигнал на выходе логического элемента И-НЕ 12. После этого на обоих входах логического элемента -HE 13 оказываются высокие сигналы, и на его выходе формируется низкий уровень 0ап» ряжения. Остальные сигналы на выходах логических элементов устройства остаются неизменными.

В момент ф начала второго входного нмцульса на всех входах логического эле- мента 9 оказывак>тся единичные сигналы, н на его выходе формируется нулевой потенциал. Этот сигнал подтверждает высокие сигналы на выходах элементов И-НЕ

9,10 и 4 н вызывает формирование едипичного потенциала на выходе элемента

И-НЕ 2. Других изменений выходных сигналов логических элементов в момент С не происходит.

По окончании второго входного сигнала (момен. 4g) ко входу логических элементов

И-НЕ 9,10 и 12 оказывается приложенным низкий входной сигнал. Он подтверждает высокие потенциалы на выходах логических элементов И-НЕ 10 и 12 и устанавливает высокий сигнал на выходе элемента И-НЕ 9. После этого на обоих входах элементов И-НЕ 8 оказываются единичные сигналы, и íà его выходе формируется нулевой потенциал. Других изменений выходных сигналов логических элементов в момент - не происходит.

В момент4 > начала третьего входного импульса на всех входах логического элемента И-НЕ 10 оказываются единичные сигналы, и на его выходе формируется н левой потенциал. Этот сигнал подтверждает единичные сигналы на выходах элементов И-НЕ 11,12 и 2, а также вызывает формирование единичного сигнала на выходе элемента И-НЕ 3, пооле этого на всех входах логического элемента И-НЕ 4 оказываются единичные сигналы, и на его выходе формируется сигнал логического нуля, ко1 орый подтверждает сигналы единичного уровня на выходах логического элемента И-НЕ 2,3 и 9, а также формирует единичный сигнал на выходе логического элемента И-НЕ 13.

Других изменений выходных сигналов логи- ческих элементов в момент не происходит.

По окончании третьего входного импульса (момент 6iKo входу логических элементов И-НЕ 9,10 и 12 оказывается приложенным низкий входной сигнал. Он подтверждает вы<-окне потенциалы н выходах элементов И-НЕ 9 и 12 и формирует высокий сигнал на выхоце элемента И-НЕ 10.

После этого к обоим входам элемента И»

НЕ 11 оказываются приложены высокие сигналы, и на его выходе формируется потенциал логического нуля, котоу ый подтверждает высокий сигнал на выходе элемента И-НЕ 10 и формирует высокий сиг нал на выходе элемента И-HE 8. Других изменений не происходит.

По окончании третьего импульса во всех логических элементах устройства пересчета на три оказываются выходные сигналы, полностью совпадающие с сигналами перед подачей первого импульса. Это означает, что дальнейшая работа устройства полностью повторяет вышеописанную.

Анализ работы предлагаемого устрой-. ства показывает, что в его функционирова: нии полностью исключены состязания . За« счет этого существенно повышается надежность работы устройства.

Формула изобретения

Устройство пересчета на-"три по авт.св.

И 506132, о т л и ч а ю щ е е с я тем, что, с целью повышении надежности работы, четвертый вхоЪ первого логического элемента третьего вспомогате .ьного триггера соединен с последним выходом троичного однофаэного асинхронного установочного триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

¹ 506132, кл. Н 03 К 29/ОО, 22.06.73.

Составитель Н. Дубровская редакч ор р. Папп ТехредТ.Маточка Корректор, М. немчик

Заказ 8357/86 Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4