Преобразователь частоты в код

Иллюстрации

Показать всеРеферат

П.В.Соловов, Н.Л.Москвитин, О.А.Титов, Н.К.Кокорин, С.Ф.Стрепетов, А.П.Панкрашин, А.Н;-,Кукушкин, А.А.Маштаков, Е.М.Бахнов и А.И.Сметднин

I (72) Авторы изобретения

Рязанский радиотехнический!институт (7!) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД ПОРАЗРЯДНОГО

КОДИРОВАНИЯ

Изобретение относится к автоматике и вычислительной технике и может быть использовано как в качестве автономного устройства, так и в составе информационно-измерительных систем.

Известен преобразователь частоты в код поразрядного кодирования, содержащий управляющий регистр, двоичный умножитель, программный блок, блок .сравнения, делитель частоты, причем входы программного блока соединены с установками "Q" и "!" каждого иэ его разрядов, а входы — соответственно с выходом блока сравнения, а также с установками в "0" делителя частоты и двоичного умножителя и с одним иэ входов блока сравнения, второй вход которого соединен с выходом делителя частоты, вход которого соединен с выходом двоичного умножителя, кодовые входы которого соединены с выходами соответствующих разрядов управляющего регистра, а к ча..

2 стотному входу подключена высокая опорная частота (! ).

В данном устройстве первый при" шедший импульс входной частоты обнуляет двоичный умножитель и делитель частоты. В тот же момент программный блок устанавливает старший разряд управляющего регистра в "!". В результате на выходе делителя частоты формируется период длительностью т- 2 (Й1Fo, где 2 — коэффициент деления делиИ теля частоты, д! — значение старшего разряда управляющего регистра.

Если Т меньше периода 7! входной частоты Fy,, блок сравнения подает команду в программный блок на возвращенке старшего разряда управляющего регистра в "О". В противном случае он остается в "!", с приходом следующего входного импульса включается п-!-ый разряд! управлякщего регист871093 „. -F 2"-",ее и aF„- Г,/ 1-"

40 о) где Ьà — частота на выходе элемента .1

ИЛИ q-òîãî каскада;

QF — входная частота 1-того каскада, Fpf2 + опорная частота, подаваемая на 1-тый каскад с делителя частоты.

Следовательно, для выходного кода и р„ <

Fo

К недостаткам этого преобразователя следует отнести малое быстродействие, 5> обусловленное тем, что при Р )F / 1- t первый импульс частоты с выхода вы)читающего блока устанавливает в "1" ра и т.д. По окончании цикла преоб.разования с точностью до единицы младшего разряда выходной код аи

N = — FFx.

К недостаткам этого преобразователя относится невозможность преобразования высоких частот, т.к.

<в

Со Х макс И

От указанного недостатка свободен известный преобразователь частоты в код, содержащий блок временного разделения импульсов, подключенный к шине преобразуемой частоты, генератор опорной частоты, соединенный с блоком временного разделения импульсов и И -разрядным двоичным делителем частоты, вычитающие блоки, число которых равно разрядности выход- 20 ного кода и выходы которых подключены к регистрирующим блокам, два элемента И и элемент ИЛИ, причем входы вычитающего блока старшего разряда подключены к генератору опорной ча- 25 стоты и блоку временного разделения ,импульсов и БВРИ, выходы регистрирующего блока подключены к первым входам элементов И, вторые входы которых соединены соответственно со входом з0 регистрирующего блока и входом вычитающего блока, а выходы через элемент

ИЛИ подключены ко входу вычитающего следующего разряда, другой вход которого соединен с соответствующим выходом делителя частоты(2), В этом устройстве в каждом 4 -том каскаде реализуется операция регистрирующий блок, и только второй ее импульс через открывшийся элемент

И и элемент ИЛИ пройдет на следующий каскад.

Целью изобретения является увеличение быстродействия.

Поставленная цель достигается тем, что в преобразователь частоты в код, содержащий генератор опорной частоты, выход которого соединен со входом двоичного делителя частоты и первым входом блока временного разделения импульсов, второй вход которого соединен с шиной входной частоты, а выход соединен со входом И-ного из последовательно соединенных каскадов, состоящих из вычитающих и регистрирующих блоков и элементов И и ИЛИ, выход каждого из каскадов соединен со входом следующего каскада, при этом первые входы вычитающих блоков каждого каскада соединены с соответствующими выходами двоичного делителя частоты, а вторые входы соединены со входом каскада и первым входом элемента И того же каскада, второй вход которого соединен с нулевым выходом регистрирующего блока, а выход соединен с первым входом элемента ИЛИ, выход которого соединен с выходом каскада, а выходы вычитающих блоков подсоединены к соответствующим входам регистрирующего блока, причем второй вход, элемента ИЛИ каждого каскада соединен с единичным входом регистрирующего блока этого же каскада.

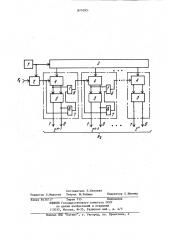

На чертеже представлена структурная электрическая схема преобразователя частоты в код.

Устройство содержит генератор 1 опорной частоты, блок 2 временного разделения. импульсов, двоичный делитель 3 частоты, вычитающие блоки 4, регистрирующие блоки 5, элементы

6 ИЛИ и элементы ? И.

Устройство работает следующим образом.

Импульсы входной частоты Е поступают в блок 2 временного разделения импульсов, на второй вход которого приходят также импульсы опорной частоты Fp с генератора 1 опорной частоты. Блок 2 обеспечивает некоторый временной сдвиг импульсов частоты Fy в случае их совпадения с импульсами частоты Fp . В двоичном делителе 3 производится выработка ча стотных составляюших F Q, Fp(Q, Fp/g, 871093

yl-1 .Е

>К

Благодаря увеличению быстродейст10 вия снижаются также динамические погрешности, обусловленные изменением входной частоты за время кодиро-> вания.!

Формула изобретения

В любом 1-том каскаде импульс разностной частоты ЬГ4 одновременно с установкой в "1" регистрирующего блока 5 проходит через элемент 6 ИЛИ 25 на следующий каскад.

Для 1-того каскада условие (3) приобретает вид (1) . Моделирующая зависимость предлагаемого устройства аналогична выражению (2 ) для прототиЗО па.

Выигрыш в быстродействии предлагаемого устройства достигается за счет снижения времени задержки в выдаче первого импульса разностной частоты.

-t.o/2 в каждом 1-том каскаде.

Использование предложенного устрой, ства позволяет существенно снизить время кодирования. Так, для случая

Е1ф) = „С04>-,чему соответствует выходной код К =1 1...1, уменьшение задержки в вьдаче первого импульса частоты ЬГ4 для 1-того разряда равно периоду 11 =1/ЬТ1 или, с учетом того, что пРи 12®= 1 мсИСС> Ж- о 2.",Т; 2" 1 го, выигрыш по времени кодирования предложенного устройства .по сравнению с прототипом составит

50 г" .Е Т. F > о

Источники информации, принятые во внимание при экспертизе

1. Мартяшин А.И. и др. Преобразователи электрических параметров для

55 систем контроля и измерения. М

Энергия, 1976, с. 208-209.

2. Авторское свидетеЛьство СССР

Ф 251958, кл. С 01 R 23/02, 20.05.68 (прототип).

»-1

° . о 2 Вычитающий блок 4 первого каскада реализует операцию Fy-F o.

Если Fy ) Г > импульсы разностной частоты появляются на выходе вычитающего блока 4, связанном с установкой "1" регистрирующего блока 5, устанавливая последний в "1" (значение старшего разряда выходного кода становится равным "1"). В противном случае регистрирующий блок 5 устанавливается импульсами с противоположного выхода вычитающего блока 4 в "0".

Следующий каскад функционирует аналогичным образом с той разницей, что вместо Fy u Fo подаются частоты

> 1 и о12, где

1=õ-Fo, ÅÑËÈ Е„) Го (5)

1 F„,ОСЛА Fq - 1-О где 11 — разрядность кода Й

Известно, что время кодирования для прототипа составляет г +

Т= к

Следовательно, быстродействие предложенного устройства вдвое выше быстродействия прототипа, т.к.

Преобразователь частоты в код, содержащий генератор опорной частоты, выход которого соединен со входом двоичного делителя частоты и первым входом блока временного разделения импульсов, второй вход которого соединен с шиной входной частоты, а выход соединен со входом

1 1-ного из последовательно соединенных каскадов, состоящих из вычитающих и регистрирукицих блоков и элементов И и ИЛИ, выход каждого из каскадов соединен со входом следующего каскада, при этом. первые входы вычитающих блоков каждого каскада соедииены с соответствующими выходами двоичного делителя частоты, а вторые входы соединены со входом каскада и с первым входом элемента И того же каскада, второй вход которого соединен с нулевым выходом регистрирующего блока, а выход соединен с первым входом элемента ИЛИ, выход которого соединен с выходом каскада, а выходы вычитающих блоков подсоединены к соответствующим входам регистрирующего блока, отличающийся тем, что, с целью увеличения быстродействия, второй вход элемента ИЛИ каждого каскада соединен с единичным входом регистрирующего блока этого же каскада.

871093 рФ-1

Составитель Л.Беляева

Редактор Б.Федотов Техред М.Рейвес Корректор С.Шекмар

Заказ 8430 17 Тираж 735 Подписное

ВЦИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r.. Ужгород, ул. Проектная, 4