Цифровой преобразователь координат

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сеюэ Сееетсннк

Социалистических

Реслублик

<щ 873 162 (6t ) Дополнительное к авт. сеид-ву(22) Заявлено г80380 (23) г874880/18-г4 (5f)PA gp 3

G 06 Р 7/548 с присоединением заявки йоГосударственный комитет

СССР но делам изобретений н открытий (23}ПрмормтетОпубликовано 0 11081. Бюллетень Н9 37 (53) УДК 881. ЗгЗ (088.8) Дата опубликования описания 07.1081 (72) Автор изобретения

E.Ô. Киселев (73) Заявитель

{54} ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ КООРДИНАТ

Изобретение относится к вычисли тельной технике и предназначено для вычисления по известным кодам полярных координат н измеряемой величины кодов ее прямоугольных координат к и ч и наоборот.

Известно устройство (1), функционирование которого связано с числоимпульсной обработкой информации.

Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство для преобразования прямоугольных координат в полярные f2), содержащее регистры, коммутаторы, цифровой преобразователь, умножитель, сумматор и блок управления.

Недостатком этих устройств является низкое быстродействие.

Цель изобретения.- повышение быстродействия.

Поставленная цель достигается тем, что в цифровой преобразователь координат, содержащий два регистра, два коммутатора и первый функциональный преобразователь, введены второй функциональный преобразователь и арифметический блок. Группы разрядных выходов первого и второго регистров соединены соответственно с первой и второй группами входов первого коммутатора. Группа выходов первого коммутатора соединена с группой входов арифметического блока.. Выходы первого и второго регистров соединены соответственно с первым и,вторымвходами первого функционапьного преобразователя, третий вход которого соединен с первым выходом арнфмети« ческого блока и с первым выходом устройства. Группа разрядных выходов второго регистра и группа выходов первого функционального преобразова теля соединены соответственно с пер

15 вой и второй группами входов второго коммутатора. Группа выходов второго коммутатора соединена с группой входов второго функционального преобразователя и с первой группой вы20 ходов устройства. Группа выходов второго функционального преобразователя соединена с третьей группой входов первого коммутатора. Группа выходов арифметического блока соединена с второй группой выходов устройства и с группой входов первого функционального преобразователя.

Второй выход арифметического блока. является вторым выходом устройства.

30 Вход второго коммутатора являетсд

871162 первым управляющим входом устройства.

Второй управляющий вход устройства соединен с первым и вторым входами первого коммутатора и арифметического блока. Третий и четв эртый управляющие входы устройства соединены соответственно с третьим входом арифме5 тического блока и входом второго функционального преобразователя.

Четвертый,. пятый и шестой входы арифметического блока являются соответ-, ственно первым, вторым и третьим тактовыми входами устройства.

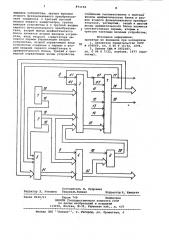

Структурная схема устройства при-, ведена на чертеже. Устройство содержит регистры 1, 2, коммутаторы

3, 4, функциональные преобразователи 35

5, 6, арифметический блок 7.

На чертеже обозначены управляющие

<" входы .8-11 устройства, тактовые входы 12 — 14 устройства, выход 15 регистра 1, выход 16 регистра 2, вы- gQ ход 17 устройства, группа выходов

18 регистра 1, группа выходов 19 регистра 2, группа выходов 20 функ-. ционального преобразователя б, группа выходов 21 функционального преобразователя 5, группа выходов 22 коммутатора 3, группа выходов 23 устройства, группа выходов 24 устройства, выход 25 устройства.

При выполнении вычислИтельной операции умножения и деления выполняются арифметическим блоком 7, вычисление по аргументу (углу ч ) функции синуса или косинуса — функциональным преобразователем 6, а вычисление по аргументу (tg с ) функции, (т.е. угла Д ) — функциональным преобразо в ателегл 5.

Каждое из.вычислений выполняется за цикл по содержимому регистров

1, 2 по сигналам, вырабатываемым на выходах 17, 24 и 25 арифметического блока 7 (на выходе 17 выраба- ° тывается информационный сигнал С17, а выходе 25 — управляющий сигнал .П25 такой, что если арифметический 4 блок 7 занят вычислением, то П25=1, а если — .свободен,, то П25=0) и по входным управляющим и синхронизирующим сигналам: сигналам. управляющего двухразряд50 убого кода . al и а2 (al и а2 разрядные цифры кода), поступающим с входов 8 на управляющие входы коммутатора 3 и арифметического блока 7; управляющим сигналам П9, П10 и Пll соответственно поступающим с входов 9, 10 и 11 на управляющие входы коммутатора 4, функционального. преобразователя б и на управляющий вход арифметического блока 7; импульсу ИВ12 ввода, импульсу

И313 запуска и тактовым импульсам .

ТИ14 соотвЕтственно, поступающим с-входов 12, 13 и 14 на соответствующие входы арифметического блока 7. 65

В каждом цикле выполнения прямого преобразования или обратного преобразования можно выделить два временных такта, в каждом из которых в установившемся состоянии с выхода

15 и с выходов 18 регистра 1 снимается информационный сигнал С15 и код функций Ф18, с выхода 16 и с выходов 19 регистра 2 — информационный сигнал Сlб и код функции Ф19, с выходов 20 функционального преобразователя 6 — код функции Ф20, с выходов 21 функционального преобразователя 5 — код функции Ф21, с выходов 22 и 23 коммутаторов 3 и 4 - код функции Ф22 и код функции Ф23,с выхода 17, выходов 24 и выхода 25 арифметического блока 7 — информационный сигнал С17, код функции Ф24 и выходной управляющий сигнал П25.

При выполнении .в преобразователе координат прямого преобразования и обратного преобразования есть некоторые аналогии. С связи с этим описание работы при выполнении прямого и обратного преобразований будем проводить по возможности параллельно, (в круглых скобках информация, относящаяся к описанию работы при обратном преобразовании).

Преобразователь координат по кодам Ч и (кодам )(и У )„за время каждого цикла прямого (обратного) преобразования осуществляет вычисление в первом такте кода Х (кода Ч ), а во втором — кода у (кода г ).

Перед началом:некоторого очередного цикла прямого (обратного) преобразования арифметический блок 7 занят (вырабатывает сигнал П25=1), в регистрах 1 и 2 .содержатся коды

Ф18=г. и Ф19= Ч (коды Ф18= Х и Ф19=У и вырабатываются сигналы С15=Х +л и С16=У„ л, на входы 8 поступает код 00, а на входы. 9 и 10 сигналь П9=0 и П10=0 (сигналы П9=1 и П10=С17). С помощью сигналов П9=

10=0 функциональный преобразователь

6 вырабатывает код Ф20=Соэ Ч (код

Ф20 при П9=1 и П10=С17).

С помощью кода 0 коммутатор

3 выдает на арифметический блок 7 код Ф22=Ф18= г (код Ф22=Ф18=Х).

Цикл прямого (обратного) преобразования начинается в момент выработ ки арифметическим блоком 7 сигнала

П25=0, по которому на выходы 17 и 24 арифметического блока 7 выдается результат вычисления.

По сигналу П25=0 код Ф24 снимается с арифметического блока 7, поступают сигнал П11=0 (сигнал Пll-l) и первый импульс ИВ12.

По сигналу П11=0 (IIll=l) арифметический блок активизируется на выполнение операции умножения (деления), а по первому ИВ 12 в память арифметического блока 7 заносится код Ф22= (код Ф22= Х.).

871162

5 (О

20

Х У

Ф24.= к созе к ч

Формула и обретения

После окончания первого ИВ12 на входы 8 подается код 10 (код 01 ), на входах арифметического блока 7 устанавливается код Ф22=Ф20=

=Cos Ч (код Ф22=Ф19= У ) и на арифметический блок 7 проходят второй ИВ12 и первый импульс запуска И313. По второму ИВ12 в память арифметического блока заносится код Ф22=Соэ Ч (код Ф22=у). После окончания первого

ИВ13 на вход.10 поступает сигнал .П10=1, на входы 8 - код 00 (код OC17 ) преобразователь 6 занят вычислением кода Ф20=81п ч по сигналу П10=1 и коду Ф23= Ч (кода .

Ф20 по сигналам П9=1, П10=С17,C15=X»<

С16=Ун+g и кодам Ф24, Ф21=Ф23, а арифметический блок 7 запускается на выполнение операции умножения по кодам г и Cos 4 (операции деления по кодам )1и У ) .

После окончания каждого И313 арифметический блок 7 выполняет (при П11=0) операцию умножения за длительность времени урн (при, П11=1) операцию деления за длительность времени Àå с помощью тактовых импульсов ТИ14.

При выполнении прямого преобразования через время преобразования

1 ).и. преобразователь 6 вырабатывает код Ф20=81п У, а через время t>M> Ъ

>4Ф н.арифметический блок 7 вырабатывает сигнал П25=0 и код Ф24= СоэЧ=Х

По сигналу П25=0 с арифметического блока 7 снимается код Ф24=Х, и начинается второй такт преобразования, который аналогичен первому такту, за исключением того, что во втором такте в памяти арифметического блока 7 заносятся коды P и sin9

Поэтому в конце цикла прямого преобразования арифметический блок 7 вырабатывает сигнал П25=0 и код

Ф24= Б1пЧ=У. По данному сигналу

П25=0 производятся съем с арифметического блока 7 кода Ф24= У и запуск преобразователя координат для последующего цикла либо прямого, либо обратного преобразования. Если длительностью времени ввода информации в арифметический блок 7 пренебречь, то длительность Т А выполнения прямого преобразования можно оценить выражением

Ч" 2 ЯБАН

В первом такте при выполнении обратного преобразования через время %*st, арифметический .блок 7 вырабатывает сигнал П25=0, код Ф24=

= .К-Я - k.-()и сигнал С17=К, где

К=О, если)х(>(ч(и К =1, если !Х!с)У!

Так как П9=1, П10=С17=К,С15=Хи, С16=У, а входной управляющий код

ОК, то через некоторое время после выполнения первой операции деления на входах арифметического блока 7 устанавливается код Ф22= К X+ К.У, преобразователь 5 вырабатывает код

Ф21=Ч, коммутатор 4 - коц Ф23=Ф21=Ч. а преобразователь 6 - код Ф20=ГСоя

+KSing . После установления кодов на арифметический блок 7 приходит третий ИВ12, после окончания которого на входы 8 йодается код 10 ., на входах арифметического. блока 7 устанавливается код Ф22=Ф20=КСозЧ +КЯ1п9 и поступает четвертый ИВ12 и второй

ИВ13. По третьему и четвертому ИВ12 в арифметический блок 7:заносится .код Ф22= К.<+ кl и код Ф22=КСоЖ КЯ1пЧ а по второму импульсу И313 заканчивается первый такт и начинается второй такт обратного преобразователя; т.е. производится съем кода

Ф23= и запуск арифметического блока

7 на выполнение операции деления по коду (Кх + кy) и коду (кСоеУ+

+КюиЧ) . Поэтому в конце цикла обратного преобразования арифметический блок 7 вырабатывает сигнал П25=0 и код

По данному сигналу П25=0 производится съем с арифметического блока 7 кода Ф24= )" и запуск преобразователя координат для последующего цикла либо обратного, либо прямого преобразования.

Применение изобретения позволяет повысить быстродействие устройства, Цифровой преобразователь координат, содержащий два регистра, два коммутатора и первый функциональный преобразователь, о т л и.ч а ю щ и йс я тем, что, с целью повышения его быстродействия, он -содержит второй функциональный преобразователь и арифметический блок, причем руппы разрядных выходов первого и второго регистров соединены соответственно с первой и второй группами входов первого коммутатора, группа выходов .

50 .первого коммутатора соединена с группой входов арифметического блока, выходы первого и второго регистров соединены соответственно с первым и вторым входами первого функционального преобразователя, третий вход которого соединен с первым выходом арифметического блока и с первым выходом устройства, группа разрядных выходов второго регистра и группа выходов первого функционального пре обраэователя Соединены соответственно с первой и второй группами входов второго коммутатора, группа выходов второго коммутатора соединена с группой входов второго функционального преобразователя и с первой группой

871162

Составитель. М. Кудряшев

Редактор Л. Утепина ТехредМ.Рейвес Корректор Н. Швыдкая

Тираж 748 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 8436/21

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 выходов устройства, группа выходов второго функционального преобразователя соединена с третьей группой входов первого коммутатора, группа выходов устройства н с группой входов первого функционального преобразователя, второй выход арифметического блока является вторым выходом устройства, вход второго коммутатора является первым управляющим входом устройства, второй управляющий вход устройства соединен с первым и вторым входами первого коммутатора и арифметического блока, третий и четвертый управляющие входы устройства соединены соответственно с третьим входом арифметического блока и sxoдом второго функционального преобразователя,- четвертый, пятый и шестой входы арифметического блока являются соответственно первым, вторым и третьим тактовым входами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 656069, кл. G 06 F 15/32, 1976.

2. Патент США Р 3952187, кл. G 06 G 7/22, опублик. 1977 (прототип) .