Устройство для синхронизации импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОЗРЕТЕН ИЯ

<,871322

Союз Соаетскмн

Социалистическин

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свил-ву (53)NE. Кл. (22) Заявлено 26.1079 (2) ) 2832686/ 1 8-21

Н 03 К S/)3 с присоеяинением заявки ¹

3Ъвулврстеенны11 квинтет

СССР

40 аиеш нзабретеннй

N открытий (23) Приоритет

Опубликовано 07,1081. Бюллетень ¹ 37 (53) УДК 621.

374 3 088 8

Дата опубликования описания 10.1(Ь1

А.В. Ицкович, Н.М. Кравченко, А.С. Ко и Я.В. Сахновнч

L i утенко > с ";,; р

Г4 j ßÈ, I1д»

С 1 :" <:.ы,;,.;р ° f 3 (72) Авторы изобретения

У, I (71), Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ ю

Изобретение относится к импульсной технике, предназначено для синхронизации импульсов и может быть использовано в автоматике, приборостроении, вычислительной технике, особенно в интерфейсных блоках, например в автоматизированных системах управления в различных отраслях народного хозяйства.

Известно устройство для синхронизации импульсов, содержащее последоlO вательно. соединенные три триггера и элемент исключающее ИЛИ 11.

Недостатком данного устройства является невысокая помехозащищенность.

Наиболее близким по технической сущности является устройство для синхронизации ямпульсов, содержащее ключ,, вход которого подключен к источнику синхронизируемых импульсов, а выход соединен со входом установки первого триггера, .выход которого связан с одним входом первого разряда сдвигового регистра, другой вход которого.подключен к источнику тактовых импуль-сов, а также второй триггер, вход установки которого подключен к источнику синхронизируемых импульсов, а выход соединен со вторым входом ключа, а входы сброса первого и второго триггеров подключены к выходу первого разряда сдвигового регистра (2).

Известное устройство обладает следующими существенными недостатками: сложность схемы, что при необходимости синхронизации большого количества устройств требует большого количества микросхем, малая помехоустойчивость, из-за чего на выходе устройства появляется сигнал даже при короткоф помехе на входе.

Целью изобретения является повышение помехоустойчивости устройства.

Поставленная цель достигается тем, что в устройстве для синхронизации импульсов, содержащем триггер и сдвиговый регистр, вход первого разряда которого соединен с выходом триггера, 871322

1О

Z0

Q(t+1) 0{t) 1 2

3 4

1 0 0 0 0

2 1 0 О. 0

3 1 0 0 1

4 1 0 1 1

5 1 1 1 1

6 0 1 1

7 0 0 1 1

8 0 0 0 1

50 а

55 выход триггера дополнительно подключен к управляющему входу и входу последнего разряда сдвигового регистра, который выполнен реверсивным.

Использование реверсивного сдвигового регистра и управление направлением сдвига от входного сигнала позволяет добиться высокой помехоустойчивости при подаче как положительных, так и отрицательных перепадов сигнала на вход устройства, причем глубина помехоустойчивости (максимальная допустимая длительность помехи) может изменяться простым добавлением числа разрядов регистра.

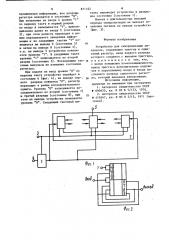

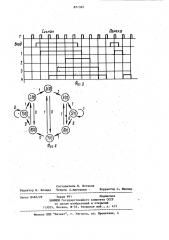

На фиг. 1 представлена структурная схема устройства, на фиг. 2 — вариант реализации на стандартном сдвиговом регистре (155ИР1); на фиг. 3 — временная диаграмма; на фиг. 4 — график переходов.

Устройство для синхронизации импульсов содержит триггер 1, 2m+i раз-. рядный сдвиговый регистр 2, шину 3 тактовых импульсов, входную шину 4 (вход), выходную шину 5 (выход).

Работа устройства происходит сле, дующим образом.

В начальном состоянии на входной шине 4 устройства логический ноль и во всех разрядах регистра 2 Ваписан логический ноль. При этом сдвиговый регистр установлен в режиме сдвига вправо. При подаче на вход 4 устройства логической "1" по первому синхроимпульсу уровень "1" запишется в триггер 1. При этом сдвиговый регистр 2 переводится в режим сдвига влево. По следующему синхроимпульсу произойдет запись "1" в (2 +1) разряд и затем продвижение "1" влево с заполнением всех пройденных разрядов.

Через (n+2) тактов после подачи входного сигнала на вход устройства на выходе 5 (п+!)-ro разряда, являющемся выходом устройства, появится "1", Еще чер з и синхроимпульсов весь регистр заполнится единицами. Если за время действия входного сигнала на шину 3 поступит менее n+1 синхроимпульсов, сигнал на выходе устройства не появится, регистр перейдет в режим сдвига вправо, выталкивая записанные сигналы "1" и заполняя регистр 2 сигналами "0".

Если в исходном состоянии все разряды регистра находились в состоянии

"1", а на вход поступает сигнал "0", после первого синхроимпульса регистр переходит в режим сдвига вправо, через и+2 такта сигнал "0" появляется на выходе, а еще через и тактов сиг" налы "0" заполняют весь регистр.

Таким образом, повышение помехоустойчивости достигается благодаря применению реверсивного регистра и управлению направлением сдвига (влево или вправо) от входного сигнала.

Пример выполнения данного устройства с использованием серийно выпуска- . емого промышленностью последовательно" параллельного сдвигового регистра

155ИР1 показан на фиг. 2, его временная диаграмма — на фиг. 3, график переходов — .на фиг. 4.

Регистр 155ИР1 при подаче высокого потенциала на управляющий вход 5 работает как регистр с параллельной записью информации по тактовым импульсам, поступающим на вход С-2, при подаче низкого потенциала происходит сдвиг информации, подаваемой на информационный вход А первого разряда регистра по тактам, подаваемым на вход С-l Работа регистра иллюстрируется таблицей.

В первом столбце таблицы указан номер текущего состояния, so второмсостояние регистра, в третьем — номер последующего состояния при подаче на вход уровня "0" или "!".

Это устройство (фиг. 2)работает следующим образом.

Предположим, в начальном состоя-нии на входе устройства "0" (состояние 1 — см. фиг. 3, фиг. 4 и таблицу), тогда на выходе первого раэряда — уровень "0", при этом регистр работает в режиме последовательного

871322

Формула изобретения

5 продвижения информации, все разряды регистра находятся в состоянии "0".

При появлении на входе 4 уровня "1" по первому такту в первый разряд по входу А записывается "1", прикладываемая далее ко входу S (состояние

2), при этом регистр переходит в режим параллельного занесения информации и по следующим тактам "1" появляется на выходе 9 (состояние 3) и затем на выходе 8 (состояние 4), т.е. на выходе 5 устройства появляется уровень "1". В следующем такте уровень "l записывается во второй разряд (состояние 5). Последующие тактовые импульсы не изменяют состояние регистра.

При подаче на вход уровня "0" по первому такту устройство перейдет в состояние 6 (фиг. 4), на выходе пер-. вого разряда. появится "0", регистр переходит в режим последовательного сдвига. Уровень "0" записывается последовательно во второй (состояние 7) н третий разряды (состояние 8), при этом на выходе устройства появляетсяуровень "0". Следующий тактовый импульс переводит устройство в начальное состояние (состояние 1).

Помеха с длительностью меньшей периода синхронизации не вызовет появления сигнала на выходе устройства (фиг. 3). устроиство для синхронизации импульсов, содержащее триггер и сдвиговый регистр, вход первого разряда которого соединен с выходом триггера, 15 о т л и ч а ю щ е е. с я тем, что, с целью повышения помехозащищенности, выход триггера дополнительно подключен к управляющему входу и входу последнего разряда сдвигового регистр ра, который выполнен реверсивным.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 690620, кл. Н 03 К 5/153, 1976.

2. Авторское свидетельство СССР

11- 410547, кл. Н 03 К 5/13, 1971 (прототип).

871322

Ьгноя пчела

Составитель В. Потапов

Редактор Н. Коляда Техред C.ìèãóíîâà c - Корректор С. Шекмар

Тираж 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 8485/29

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4