Устройство умножения флуктуаций времени задержки синусоидальных сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТВЛЬСТВУ

Союз Советскнк

Социалистическик

Реслублнк

< >873151 (61) Дополнительное к авт, свид-ву (22) Заявлено 10.1279 (21) 2855378у18-21

<51) М. Кл.

G 01 R 25/04 с присоединением заявки ¹Государственный комитет

СССР но делам изобретений и открытий (23) ПриоритетОпубликовано 15.1081 Бюллетень № 38

Дата опубликования описания 151081 (53) УДК 621. 317. 3 (088.8) (12) Авторы изобретения

Г.П. Пашев и И.Н. Чернышев (71) Заявитель (54) УСТРОЙСТВО УМНОЖЕНИЯ ФЛУКТУАЦИЙ ВРЕМЕНИ

ЗАДЕРЖКИ СИНУСОИДАЛЬНЫХ СИГНАЛОВ

Изобретение относится к радиоизмерительной технике и может быть ис-. пользовано для исследования нестабильности фазы и частоты кварцевых генераторов синтезаторов частот и синхронизированных генераторов.

Известно устройство умножения флуктуаций времени задержки синусоидальных сигналов, содержащее два ка- 10 нала преобразования сигнала, каждый из которых состоит из смесителя фильтра и формирователя, и управляемый фазовращатель, установленный на входе первого канала (1).

Управляемый фаэовращатель позволяет скомпенсировать начальный сдвиг фазы Р на входе устройства между сигналами от опорного и исследуемого генераторов с частотой и и устранить влияние шумов от общего гетеродина-с частотой и +Г, где F — разностная частота (1).

Недостатками известного устройства являются конструктивная сложность, отсутствие возможности компей у» 25 сации задержки в широком диапазоне частот исследуемых сигналов. Кроме того введение фазовращателя нарушает симметрию каналов, что вызывает увеличение температурной нестабильности З0 из-за различия температурных коэффициентов нижней и верхней ветвей устройства.

Наиболее, близким техническим решением к предлагаемому является устройство умножения флуктуацией времени задержки синусоидальных сигналов, состоящее из двух идентичных каналов, каждый из которых содержит выходной формирователь и последовательно соединенные фильтр и смеситель, первый вход которого соединен с одной из шин опорного сигнала, а вторые входы смесителей подключены к шине исследуемого сигнала (2).

Недостатком этого устройства является узкий частотный диапазон.

Цель изобретения-расширение частотного диапазона.

Поставленная цель достигается тем, что в устройство умножения флуктуаций времени задержки синусоидальных сигналов, состоящее из двух идентичных каналов, каждый из которых содержит выходной формирователь и последовательно соединенные фильтр и смеситель, первый вход которого соединен с одной из шин опорного сигнала а вторые входы смесителей подключены к шине исследуемого сигнала, введен re873151 нератор управляющего сигнала с фазоинвертором на его выходе, а в каждый из каналов нведен компенсатор задержки, включенный между выходом фильтра и входом выходного формирователя, причем вторые входы компенса" торов задержки подключены к выходам фаэоинвертора.

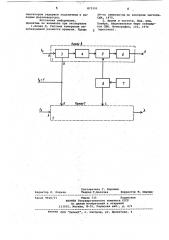

На чертеже представлена блок-схема ус.тройст.ва.

Схема устройства содержит два идентичных канала 1 и 2, каждый из l0 которых состоит из последовательно соединенных смесителя 3, фильтра 4, компенсатора задержки 5 и формирова- теля 6, а также генератор управляющего сигнала 7, соединенный с входом 15 фазоинвертора 8. Выход формирователя

6 является выходом устройства. Выходы фазоиннертора 8 соединены со входами управления компенсаторов задержки 5.

Устройство работает следующим образом.

На вход канала 1 поступает опорный синусоидальный сигнал с частотой

Йр, а на вход канала 2 поступает

) исследуемый синусоидальный сигнал с частотой f, задержанный на величину, S =t + +g4; где t.p — - начальная задержка;

gt — флуктуации задержки. 30

На входы смесителей 3 обоих каналов поступает сигнал от общего гетеродина с частотой f +Г. Выходные сигналы смесителей 3 поступают на входы фильтров 4, где выделяется сигнал разностной частоты. Синусоидальные сигналы разностной частоты F поступают на компенсаторы задержки 5. Компенсатор задержки 5 представляет . собой устройство, изменяющее момент формирования фронта выходного импуль- 40 сного сигнала нз входного синусоидального сигнала при воздействии на вход управления управляющего сигнала. Момену времени формирования фронта изменяется прямо пропорционально вели- 45 чине управляющего сигнала. Управляющий сигнал вырабатывается генератором 7 и поступает на,фазоинвертор 8.

Один из выходных сигналов фазоинвертора 9 поступает на вход управления компенсатора 5 канала 1, а противофазный выходной сигнал фазоинвертора 8 поступает на вход управления компенсатора 5 канала 2. Выходной сигнал компенсаторов 5 поступает на .формирователи 6, где формируются выходные импульсные сигналы с характеристиками, необходимыми для работы.

Выходной сигнал канала 1 предназначен для подачи на вход Старт измерителя временных интервалов, а выходной,„ 69 сигнал канала 2 для подачи на вход Стоп измерителя (на чертеже не показан). При постоянном сигнале управления на входах компенсаторов 5

|флуктуации интервала времени между 65 импульсами на выходах каналов 1 и 2 равны N gt, где N = f /F. Это позво- ляет точно измерить малые флуктуации задержки, фазы и частоты сигналов на входах каналов 1 и 2. Устройство действует таким образом, что при нуленой начальной задержке опорного и исследуемого сигналов и при нулевом управляющем сигнале импульсы на выходах каналов 1 и 2 появляются одновременно. Если начальная задержка не равна нулю, то путем изменения управляющего сигнала добиваются уменьшения интервала между импульсами каналов

1 и 2 до неличины много меньшей времени корреляции шумов гетеродина. При этом исключается влияние шумов гетеродина на погрешность измерения флуктуаций задержки bt.

Включение компенсирующего элемента не в высокочастотном входном тракте, а в низкочастотном тракте разностной частоты облегчает требования к широкополостности компенсатора, позволяет упростить конструкцию компенсаторапо сравнению с регулируемой СВЧ линией задержки в известном устройстне. Диапазон рабочих входных частот определяется при этом только смесителями и легко расширяется до сотен мегагерц.

Включение компенсирующих элементов симметрично в оба канала преобразования уменьшает необходимый диапазон компенсации каждого компенсатора задержки и уменьшает температур"ную нестабильность умножителя флуктуаций задержки, связанную с изменением параметров элементон умножителя.

Наличие генератора управляющего сигнала 7 и фазоинвертора 8 позволяет вручную или автоматически скомпенсировать начальную задержку и систематическое изменение задержки между сигналами на входах каналов 1 и 2.

Формула изобретения

Устройство умножения флуктуаций времени задержки синусридальных сигналов, состоящее из двух идентичных каналов, каждый из которых содержит выходной формирователь и последовательно соединенные фильтр и смеситель, первый вход которого соединен с одной из шин опорного сигнала, а вторые входы смесителей подключены к шине исследуемого сигнала, о т л и ч а ющ е е с я тем, что, с целью расширения частотного диапазона, в него введен генератор управляющего сигнала с фазоинвертором, íà его выходе, а н каждый из каналов введен компенсатор задержки, включенный между выходом фильтра и входом выходного формирователя, причем вторые входы ком873151

Монад R

AI (2

Составитель Г. Королев

Техред Т.Маточка Корректор М. Шароив

Редактор Л. Повхан.

Тираж 735 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий.113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 9026/71

ППП "Патент"," r. Ужгород, ул. Проектная, 4 пенсаторов задержки подключены к выходам фазоинвертора.

Источники информации, принятые во внимание при экспертизе

1.Аллан Д. Система измерения пикосекундной разности времени. Труды

29-ro симпозиума по контролю частоты.

CIQA, 1975.

2. Время и частота. Под. ред.

Блейра. Национальное бюро стандартов США. Монография, 140, 1974

5 (прототип) е