Дешифратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ВЯЛЬСТЮУ (61) Дополнительное к авт, сеид-ву—

{22) Заявлено 171279 (21)2855617/18-24

Свез Советския

Социалистические

Республик

«ii873235 (53)PA К„з

G 06 F 5/02

G 05 F 11/26 с присое4инением заявки Йо

ГосударствеяяыФ комятет

СССР по делам язобретеннй в открытяя (23) Ориорнтет—

Опубликовано151081. бюллетень ЙФЗ.8

Дата опублилбвания описания 15.1081 (53) УДК 681.3 (088. 8 ) Г

В.ИъКорнейчук, В.П.Тарасенко и B jX. Цонев

1 Киевский ордена Ленина политехнический ийститут ищ . Великой Октябрьской социалистической, революции

P2) Авторы изобретения

50-летия (71) Заявитель (54) ДЕШИФРАТОР

Изобретение относится к вычислительной технике и может быть применено в дешифраторах универсальных и специализированных цифровых вычислительных машин.

Известны схемы дешифраторов с контролем и обнаружением ошибок, содержащие элементы И, ИЛИ, схеме кснтроля 1), 2 1 и С31.

Недостатком таких дешифраторов яв-. ляется плохая диагностируемость, состоящая в том, что в них контролируется непосредственно работа дешифраторов и обнаруживаются наиболее вероятные ошибки (чаще всего появление двух нли более единиц или отсутствие единицы на выходах дешифратора). При обнаружении ошибки часто нельзя указать элементарную логическую схему, в которой она произошла, поэтому необходимо проводить проверку правильности работы дешифратора на всех наборах входных переменных, что связано с большими затратами машинного вре- мени.

Наиболее близким техническим решением к предлагаемому изобретению является дешифратор, состоящий из двух каскадов однотипных модулей, каждый из которйх имеет два информа- З0 ционных входа, два управляющих входа и четыре выхода, причем управляющие входы для каждого модуля первого каскада соединены вместе, а к управляющим входам модулей второго каскада подключено по одному выходу модулей первого каскада, причем наборы выходов модулей первого каскада не повторяются, а первые и вторые информационные входы модулей второго каскада соединены соответственно между собой 4 )

Недостатком этого устройства является то, что для полной диагности- ки такой схемы необходимо подавать 2 . входных наборов, что приводит к большим затратам машинйого ремени.

Цель изобретения — повышение быстродействия контроля и диагностики путем сокращения числа наборов, необходимых для полной диагностики дешифратора.

Поставленная цель достигается тем, что в дешифратор, содержащий две группы дешифрирующих ячеек, причем информационные входы дешнфрирующих ячеек первой группы являются группой информационных входов дешифратора, первый и второй управляющие входы каждой дешифрирующей ячейки

873235 первой группы объединены и являются соответственно первьм и вторым управляющими входами дешифратора, выходы каждой 43 -ой дешифрирукнцей ячейки второй группы являются группой выходов дешифратора,.введена группа из 2п элементов ЙЛИ, к первому и второму управляющим входам каждой дейифрирующей ячейки которой группы подключены выходы соответствующей пары элементов ИЛИ. первые входы всех элементов ИЛИ группы соединены с третьим управляющим входом дешифратора. каждый 1-й выход к-ой дешифрирующей ячейки первой групйы соединен со вторыми входами Р-ых элементов ИЛИ группы (Р=16(к-1)+

4(л-1)+8, где 6=1-4, к=1-2, =1-4 первые информационные входы дешиффирующих ячеек второй группы объединены и являются первым информационным входом дешифратора, вторые информационные входы дешифрирующих ячеек второй группы объединены и являются вторым информационным входом дешифратора.

Кроме того, каждая дешифрирующая ячейка содержит четыре элемента.

И и два.элемента НЕ, причем первый и второй управляющие входы дешифрирующей ячейки соединены соответственно с первыми и вторыми входами всех элементов И, выходы которых являются выходами дешифрирующей ячейки, первый информационный вход дешифрирующей ячейки соединен с первыми входами первого и второго элементов И и через первый элемент НЕ с первыми входами третьего и четвертого элемента И, второй информационный вход дешифрирующей ячейки соединен со вторыми входами первого и третьего элемента И и через второй элемент НЕ со вторыми входами второго и.четвертого элементов И.

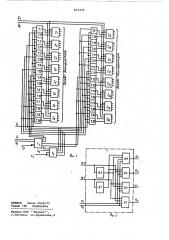

На фиг. 1 приведена схема дешифратора, на фиг. 2 дешифрирующая ячейка.

Дешифратор содержит дешифрирующие ячейки 1.1 и 1.2 первой группы, .дешифрирующие ячейки 2.1...2.16 второй группы, информационные входы устройства 3.1 и 3.2, входную шину устрой- ства 4.1 и 4.2, входную шину устройства 4.3, информационные входы дешиф, ратора 5.1 и 5.2 управляющий вход 6, элементы ИЛИ 7.1, 7.2...7.32. Дешифрирующая ячейка состоит из двух элементов HE 8.1 и 8.2 и четырех элементов И 9.1...9.4, информационных входов 10.1 и 10.2, управляющих входов

11.1 и 11.2, выходов 12.1...12.4 дешифрирующей ячейки.

Дешифратор работает следующим образом.

При нормальном режиме работы на управляющий вход б подается логический сигнал "0" и тогда сигналы на выходах элементов ИЛИ 7 группы определяются только сигналами на выходах

5ешифрирующей ячейки первой группы

1.1 и 1.2. При этом на управлякнцие входы.дешифрирующих ячеек первой группы 1.1 и 1.2 всегда подается логический сигнал ".1". Возбужденным будет тот выход дешифратора, который соответствует набору входных информационных сигналов, подаваемых на входы 3.1 и 3.2, 4.1 и 4.2, 5.1 и 5.2. Когда необходимо проводить диагностику дешифратора, на управляю-, щий вход б подают логический сигнал

"1". Тогда на всех выходах элементов 7 группы сигналы равны "1" и все

1 элементы И 9 дешифрирующих ячеек второй группы 2.1...2.16 открыты.

На входы 5.1 и 5.2 подаются всевозможг ные кодовые комбинации (в данном случае их 2 4) и тем самым последовательно возбуждены все выходы 12.1...

20 12.4 каждой дешифрирующей ячейки второй группы. Таким образом, на первом этапе проверяются дешифрирующие ячейки второй группы дешифратора 2.1...2.16. После этого на упд равляющий вход 6 подают сигнал логического "0". На входы 5.1 и 5.2 можно подавать любой набор. Подавая на входы 3.1 и 3.2, 4.1 и 4.2 всевозможные кодовые комбинации (в данном случае их 9=16) можно првверить правильность .функционирования дешифрирующих ячеек первого каскада 1.1 и 1.2. Необходимость проверки на всех наборах входных сигналов для дешифрирующих ячеек первой группы

1.1 и 1.2 вытекает из того, что надо проверить прохождение сигналов с выходов дешифрирующих ячеек первой группы к выходам всех дешифрирующих ячеек второй группы 2.1...2.16. На

40 этом диагностика дешифратора заканчивается.

Таким образом, для проверки правильнос:и функционирования дешифратора, построчного на однотипных

4 дешифрирующих ячейках, необходимо подать на его входы 2 + 2 наборов, т е. 20, а не 2 - =64. Сокращение.„числа наборов,.йеобходимых для полной диагностики, приводит к сокращению

>О времени, затрачиваемого на нее. Очевидно, что быстродействие дешифратора, построенного на однотипных дешифрирующих ячейках с дополнительными элементами ИЛИ, не уменьшается, При увеличении числа дешифрируемых разрядов выигрыш в быстродействии контроля еще больше.

Формула изобретения

Дешифратор, содержащий две группы, дешифрирующих ячеек, причем информационные входы дешифрирующих ячеек первой группы являются группой информационных входов дешифратора, первый

873235 и второй управляющие входы каждой дешифрирующей ячейки первой группы объединены и являются соответственно первым и вторым управляющими входами, дешифратора, выходы каждой И-ой дешифрнрующей ячейки второй группы являются группой выходов дешифратора, о т л и ч а ю щ н и с я тем, что,, с целью повыаения быстродействия контроля и диагностики, в него введена группа из 2 н элементов ИЛИ, к первому и второму управляющим входам каждой дешифрирующей ячейки второй группы подключены выходы соответствующей пары элементов ИЛИ, первые входы всех элементов ИЛИ группы соединены с третьим управляющим входом дешифратора, каждый +-ый выход"к-.ой дешифрирующей ячейки первой группы соединен со вторыми входами Р-ых элементов ИЛИ группы (P 16 (к-1)+

4(4-1)+ if, где g=1-4,. к= 1-2 20

=1-4, первые информационные .входы дешифрирующих ячеек второй группы объединены и являются первый информационным входом дешифратора, вторые информационные входы. дешифрирующих ячеек второй группы объединены..и являются вторым информационным входом дешифратора.

2. Дешифратор по п.1, о т-л и ч а. ю шийся тем, что каждая дешиф1 рирующая ячейка содержит четыре элемента И и два элемента НЕ,. причем первый и второй управляющие входы дешифрнрующей ячейки соединены соответственно с первыми и вторыми входа . ми всех элементов И, выходы которых являются выходами дешифрирующей ячейки, первый информационный вход дешифрирующей ячейки соединен с первьвы входами первого и второго элементов И и через первый элемент НЕс первыми входами третьего и четвертого элемента И, второй информационный вход дешифрирующей ячейки соединен со вторьвюи входами первого и третьего элемента И и через второй элемент НЕ со вторьваи входами второго и четвертого элементов H. Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 305472, кл. G 06 F 5/02, 16.03.70.

2. Авторское свидетельство СССР

Р 398951, кл. G 06 F 11/02, 24.04.70..

3. Патент COQ. В 3585377, 235-135, опублик. 16.06.69.

4. Корнейчук В.И.,Тарасенко В.Н и Тесленко А.П. Синтез. модульных структур дешифраторов. "Автоматика . и вычислительная техника", 1973, 9 6; с.: 68, рис. 4 (прототип).