Сумматор в коде "м из n

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (1873238

Союз Советскик

Социалистических

Республик ф! (61) Дополнительное к авт. саид-ву(22) Заявлено 061179 (2 )2838935/18-24 (51)M. Кл З с присоединением заявки М(23) ПриоритетG 06 F 7/49

Государственный комитет

СССР ио делам изобретений и открытий (53) У4К 681. З25 (088. 8) Опубликовано 15.10.81 бюллетень М З8

Дата опубликования описания 15.1081 (72) Автор изобретения

В.A. Гуменюк

«Н»„ l

Киевский ордена Трудового Красного Знамени институт--------- †.»:" инженеров гражданской авиации (1! ) Заявитель (54) СУММАТОР В КОДЕ М иэ N

Изобретение относится к вычислительной технике и предназначено для выполнения арифметических операций с числами, представленными в коде М as N, где N — количество позиций в кодовом слове, М вЂ” количество единиц в кодовом слове.

Известен двухраэрядный сумматор в коде 2 из 5, содержащий схему © местного управления, преобразователи кодов операндов, матрицы элементов И, схемы коррекции, схемы пеРеноса, шифратор младшего разряда и схемы выдачи старшего разряда суммы.

Сйгналы, соответствующие командам

° Сложить ° или Вычесть., поступают через схему местного управления на управляющие входы преобразователей кодов. Преобразователи расшифровывают подаваемые на них операн- 20 ды в код 1 иэ 10 и посылают их на матрицы элементов И. Одновременно указанные преобразователи посыла- ют сообщения в схемы коррекции о четности или нечетности прошедших через них операндов. Матрицы эле« ментов И выполняют суммирование или вычитание операндов. Сигналы с матриц элементов И поступают на схемы коррекции и на схемы переноса.Откор- 30 ректированный результат суммирования младшего разряда операндов поступаетиз схемы коррекции в шифратор,с выходов которого снимается младший раз--.... ряд суммы. Сигналы со схемы младшего разряда подаются на схемы выдачи старшего разряда суммы. Откорректированный результат суммирования старших разрядов операндов поступа ет из схемы коррекции также в схеме выдачи старшего разряда сумьм. Одна из схем зашифровывает старший разряд суммы в код 2 из 5, другая в код 2 из 5 с добавленйем единицы . Сигналы иэ схемы коррекции старшего разряда и из схемы выдачи старшего разряда суммы поступают на схему переноса старшего разряда.

Выходные сигналы последней управляют преобразователями кодов (1).

Недостатком этого сумматора является низкое быстродействие, вследствие преобразования кодов операндов перед подачей их на матрицы элементов И, проведения коррекции перед шифровкой результатов операции, а также низкое быстродействие самой матрицы элементов И.

Наиболее близким к предлагаемому по технической сущности является

873238

4 сумматор в коде N из N, младший разряд которого содержит блок выдачи результата, шифратор, матрицу элементов И, блок переноса и блок контроля, причем входы матрицы элементов И и блока контроля соединены со 5 входными шинами устройства, выходы матрицы элементов И соединены со входами шифратора и блока переноса, выходы шифратора и блока контроля соединены со входами блока выдачи ре. fp зультата. С выходов блока выдачи результата сигналы, как правило, поступают на регистр результата, выходы блока выдачи результата соединены с первой группой входов регистра результата, вторая группа входов регистра результата соединена со входной шиной устройства, являющейся шиной йредварительной установки в 0 всех;триггеров регистра результата, а выходы регистра результата соеди- 20 иены с выходными шинами устройства f2).

Недостатками данного устройства является сравнительно невысокое быстро действие из-за необходиМости прохожде д ния сигналов, соответствующих резуль.тату выполненной операции, через блок

l выдачи результата и большие аппаратурные затраты на реализацию блока контроля и блока выдачи результата.

Цель изобретения - повышение быстродействия, а также сокращение .аппаратурных затрат íà его реализацию нри предотвращении распростра.нения ошибочного результата операции с выходов регистра результата.

Поставленная цель достигается тем, что в сумматоре кода"И из N . со-. держащем регистр результата, шифратор, матрицу сложения и блок переноса, причем входы матрицы сложения соединены соответственно с-входными шинами первого и второго операндов сумматора, выходы матрицы сложения соединены соответственно со входами шифратора и блока переноса, 45 выходы регистра результата соединены с выходными шинами сумматора, первая группа входов регистра результата соединена со входной шиной установки сумматора, выходы шифрато- яО ра соединены со второй группой вхо дов регистра результата.

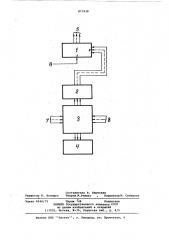

На чертеже представлена блоксхема сумматора в коде И из N

Сумматор содержит регистр 1 результата, шифратор 2, матрицу 3 сложения и блок 4 переноса, выходы регистра 1 соединены с выходными шинами 5 устройства. Первая группа входов регистра 1 соединена со входной шиной установки 6 устройства; 60 являющейся шиной предварительной установки в 1 всех триггеров регистра 1, вторая группа входов ре гистра 1 соединена с выходами шифратора 2, выходы матрицы 3 сложения соединены со входами шифратора 2 и блока переноса 4, входы матрицы 3 соединены со входными шинами 7 и 8 устройства.

Регистр 1 представляет собой группу из N триггеров, единичные входы которых образуют первую группу входов регистра 1, а нулевые - вторую группу входов регистра 1. Единичные выходы триггеров образуют группу выходов регистра 1. Шифратор 2это группа из И многовходовых элементов ИЛИ, входы которых соединены с определенными входами шифратора 2, согласно выбранному алфавиту. Результат операции шифруется в коде, противоположном (по уровням напряжений) коду М из N . Количество входов элементов ИЛИ 3 = МР/й, где Р - основание системы счисления.

Выходы элементов ИЛИ являются выходами шифратора 2. Матрица сложения представляет собой матрицу многовходовых элементов H. Количество входов элемента И равно 2 М . Входы элементов И матрицы 3 соединены с оп» ределенными шинами 7 кодов операндов согласно выбранному алфавиту.

Шины 7 кодов операндов соединены со входами матрицы 3. Шины, объединяющие выходы элементов И, соответствующих одинаковым реэультатаве операций, соединены с выходами матрицы 3. Блок

4 является группой из двух элементов

ИЛИ. Р входов одного элемента ИЛИ соединены с 1-ми входами блока 4,0 я:ЖР-1. Этот элемент ИЛИ соответствует переносу нуля. P-1 входов другого элемента ИЛИ соединены с входами блока 4, где РМД4Р-2. Этот элемент ИЛИ соответствует переносу единицы. Выходы элементов ИЛИ соединены с выходами блока 4. . Сумматор работает следующим образом.

Операнды в коде М из N поступают на входы матрицы 3. Если поступают правильные кодовые слова операндов, срабатывает один из элементов И матрицы 3 и с его вЫхода сигнал результата поступает на один из входов блока 4 переноса и один из входов шифратора 2. С одного из выходов блока 4 переноса сигнал, соответствующий 0 или 1, поступает в выходную шину, если рассматриваемый сумматор является частью многоразрядного устройства. С выхода шифратора

2 сигналы противоположные (по уровням напряжений) результату операции в коде М из N,поступают на нуле- вые икэды триггеров регистра 1,предварительно установленных в единичное состояние. На выходах регистра 1 результата образуется кодовое слово, соответствующее результату операции в коде М из N

Появление ошибочных кодовых слов операндов с меньшим, чем положено, 873238 количеством единиц,приводит к от сутствию сигналов на всех выходах элементов 4 матрицы 3. Появление ошибочных кодовых слов операндов с- большим, чем положено, количеством единиц приводит к появлению на выходах элементов И матрицЫ 3 сразу нескольких сигналов, которые затем шифруются в коде, обратном (по уровням напряжений) коду М из N, шифратором 2 как результаты нескольких правильных операций, появившихся одновременно. Вследствие этого на выходах шифратора 2 появляется кодовое слово с большим, чем положено количеством единиц . Сигналы, соответствующие единицам этого ко- !5 дового слова поступают на нулевые входы соответствующих триггеров(предварительно установленных в единичное состояние) регистра 1. На выходах регистра 1 результата образуется кодо- З) вое слово с меньшим чем, положено, количеством единиц . Как уже отмечалось, такое кодовое слово не может быть дешифровано как правильное и, следовательно, ошибка не получает дальнейшего распространения.

Шифратор 2 не обязательно должен шифровать значение результата в.коде, обратном коду М из N . Шифрация может производиться и в прямом коде, нулевые входы триггеров регистра 1 должны быть в таком случае инверсны ми. Вместо матрицы 3 сложения можно испольэовать матрицу вычитания, ум- ножения и т.д.

Положительный эффект данного сум- Зз матора заключается в повыаении.быстродействня не менее, чем на 25%, так как сигналы s нем до сформирования результата операции проходят через три блока, а в прототипе-- через четыре, и в сокращении айпаратурных затрат за счет исключения блока контроля и блока выдачи результата.

Формула изобретения

Сумматор в коде М нз N содержащий регистр результата, шифратор, матрицу сложения и .блок Переноса, причем входы матрицы сложения соединены соответственно с входными шинами первого и второго операндов сумматора, выходы матрицы сложения соединены соответственно со входами шифратора и блока переноса, выходы регистра результата соединены с выходными шинами сумматора, о т л нч а ю шийся тем, что, с целью повышения быстродействия и сокращения аппаратурных затрат, первая группа входов регистра результата соединена со входной шиной установки сумматора, выходы шифратора соединены со второй группой входов регистра результата.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 259480, кл. G 06 F 7/50, 1968.

2. Авторское свидетельство СССР по заявке Ю 2681286/18-24, кл. G 06 F 7/50, 1978 (прототнп).

873238

Составитель В. Березкин

Техред М.Рейвес, КорректорВ; Синицкая

Редактор К. Волощук

Тираж 748 Подписное

8НННОН Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 9049/75

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4