Запоминающее устройство

Иллюстрации

Показать всеРеферат

1 (72) Авторы изобретения

Г. Д. Софийский и P. В, Смирнов Г з (.

1 E ! (7I ) Заявитель (54) ЗАПОИИНАКМЦЕЕ УСТРОЙСТВО

Изобретение относится к вычислиФ тельной технике, конкоетно к запоминаюшим чстоойствам.

Известно запоминающее устройство, содеожашее оперативный накопитель, вхолной регистр адоеса и бпок корпекS ции одиночных ошибок(1).

Наиболее близким техническим решением к предлагаемому является запоминающее устройство, содержащее

10 оперативный накопитель, соединенный с адресными входами ассоциативного накопителя и через регистр адреса с адресными шинами, входы оперативного накопителя полключены к соот1 15 ветствующим входам регистра информации, выходы которого подключены к генератору синдромов и двухканальным певеключателям, соединенным с выходными числовыми шинами, выходы генератора синдромов соединены с соответствующими входами дешифратооа, выходы которого соединены с чправляюшими входами двухканальных переклю2 чателей, шифратор и входные числовые шины (2j.

Недостатком известных запоминающих чстоойств является их низкая надежность.

Цель изобоетения — повышение надежности устройства.

Поставленная цель достигается тем, что запоминающее устройство содержит дополнительные двчхканальные переключатели и дешиФраторт сумматоры, два элемента ИЛИ, элемент И, пои этом соответствуюшие выходы ассоциативного накопителя соединены со входами генератора синдоомов, вторы->: ми управляющими входами двухканальных переключателей с соответствующими вхо" дами дополнительного дешиФратора и с управляющими входами сумматоров, пеовые входы которых соединены с выхо". дами шиФратора, вторые входы — с выходом ассоциативного накопителя, а выходы — со входами первого элемента ИЛИ, выходы которого соединены со входом ассоциативного иаков нителя и с управляющими входами дополнительных двухканальных пе— реключателей, входы которых соединены с выходами шиФратора, а выходы — со входами оперативного накопителя, входы ассоциативного накопителя соединены с выходами генератора синдоо1мов и выходом второго элемента ИЛИ, входы которого соединены с выходами . 4. элементов И, первые входы котовых соединены с выхбдами дешифратооа, а вторые входы — с прямыми выходами регистра инФормации, адресные входы ассоциативного накопителя соединены с выходами оегистра адреса.

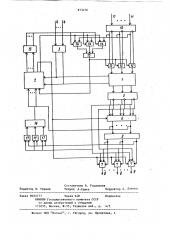

На чеотеже приведена блок-схема запоминающего устройства.

Запоминаюшее чствойство содержит оперативный накопитель 1, ассоциативный накопитель 2, регистр 3 адреса, адреснъ1е шины 4,.регистр 5 информации. генератор 6 синдромов, двухканальные переключатели 7, выход. ные числовые шины 8. дешифратор 9, шифратор 10, входные числовые шины

l1. дополнительные двухканальные переключатели 12, дополнительный дешифратор 13, сумматоры 14, первый элемент ИЛИ 15, второй элемент ИЛИ 16, элементы И 17.

Запоминающее устройство оаботает следчющим образом.

Шифратор 10 преобразчет безызбыточный код числа, постчпаюший по входным числовым шинам ll в избыточный код числа, например, код Хэмминга, позволяющий исправить однократные ошибки. Генератор синдромов 6 формирует синдром SÄ (j равен номеру разряда, в котором йроизошла ошибка) кода числа, считанного из оперативного накопителя 1 по адресу А;.

Особенностью оперативного накопителя является то, что возникающие в .нем отказы являются константными, вследствие чего считываемая по адресу A„ 3 j"ro.oòêàçàâøåãoñÿ разРяда информация е „ всегда равна либо логйческому "0",ëèáo логической

"1", в зависимости от характера возникшей неисправности. В результате, если записываемая в j-ый разряд по адресч А информация Я ° совпадает

1 с d >, то при считывании кода числа по этому адресу в нем не возникает однократной ошибки. т.е. S> О.

Если .же Е„ М д-,15, то в считанйом коде числа возникает однократная

873276 ф ошибка, т.е. S Ф О. Расшифро:—

13 ванное дешифратором 9 значение синдрома S;g определяет позицию одиноч- ной ошибки в считанном коде числа, исправление которой осуществляется путем передачи через двухканальные переключатели 7 обратного кода числа в позиции, укаэанной дешифратором

9, который дополнительно оазрешает

10 прохождение через выбранный им элемент И 17 и далее через второй элемент ИЛИ 16 на входы ассоциативного накопителя 2 значения константной неисправности с прямого выхода регистра 5 информации. Одновременно в ассоциативный накопитель 2 поступает синдром одиночной ошибки S ....

1,1

Условием загиси укаэанной информации в ассоциативный накопитель 2 является неравенство нулю синдрома S1 .

При записи кода числа в запоминающее устройство по адресу А одновремен1 но происходит поиск информации

S„, Ь „ 1 с признаком А в ассо1 циативном накопителе 2. При наличии

S ., 4 в ассоциативном накопите11 11 ле синдром S" расшифровывается дополнительным дешифратором 13 и осуществляет выборку j-го сумматора 14, который сравнивает значение константной неисправности с ц со значением 1-ro разряда записываемого кода числа

Я; и через первый элемент ЛЛИ 15 выдает результат сравне11инс1 <р" +с ч Ч

35 в ассоциативный накопитель 2 и на уп» равляющие входы дополнительных двухканальных переключателей 12. При равенстве ; ° = cj ° в оперативнйй накопи1 тель I через дополнительные двухка40 нальные переключатели 12 записываетея прямой код числа, в противном случае, т.е. % > 4 d 11 — обратный код числа. Поскольку в обоих случаях записанная в J-ый разряд информация совпадает со значением константной

45 неисправности <1.;., то при считывании кода числа синдром S" равен нулю

О

У что соответствует случаю отсутствия однократной ошибки в считанном коде числа. Параллельно со считыва50 кием кода числа из оперативного накопителя 1 осуществляется поиск информации (4 „ j) с признаком А; в ассоциативном накопителе 2. В зависимости от значения а(; ) происходит выдача

55 через двухканальные переключатели 7 прямого или обратного кода числа.

Предлагаемое запоминающее устрой/ ство дает возможность по сравнению

873276 . 6 дешифратора, выходы которого соединены с первыми управляющими вхрдами двухканальных переключателей, шиф" ратор, входные числовые шины, о ти и ч а ю щ е е с я тем, что, с целью повышения надежности устрой- ства, оно содержит дополнительные двухканальные переключатели и дешифратор, сумматоры, два элемента

ИЛИ, элементы И, при этом соответствующие выходы ассоциативного накопите" ля соединены со входами генератора синдромов, вторыми управляющими входами двухканальных переключателей, с соответствующими входами дополнительного дешифратора и с управляюшующ входами сумматоров, первые входы которых соединены с выходами шифратора, вторые входы — с выходом ассоциативного накопителя, а выходы - со входами первого элемента ИЛИ, выходы которого соединены со входом ассоциативного накопителя н с управляющими входами дополнительных двухканальных переключателей, входы которых соединены с выходами шифратора.а выходы" со входами оперативного накопителя, входы ассоциативного накопителя соединены с выходами генератора синдромом и выходом второго элемента HJIH, входы которогб соединены с выходами элементов И, первые входы которых соединены с выходами дешифратора, а

35 вторые входы - с прямыми выходами регистра информации, адресные входы ассоциативного накопителя соединены с выходами регистра адреса.

Формула изобретения

Запоминающее устройство, содержащее оперативный накопитель,.соединенный с адресными входами ассоциативного накопителя и через регистр адреса с адресными шинами, входы оператив. ного накопителя подключены к соответствующим входам регистра информации, выходы которого подключены к генератору синдромов и двухканальным переключателям, соединенным с выходными числовыми шинами, выходы генератора синдромов соединены с соответствующими входами с известными понизить на единицу кратность возникающей ошибки, что позволяет с помощью обычного кода

Хэмминга, исправляющего однократные ошибки, корректировать также и последовательно возникающие во времени двухкратные ошибки. В сочетании с известным при использовании модифицированного кода Хэмминга, исправляющего одиночные и обнаруживающего двойные ошибки, предлагаемое устройство позволяет исправить три последовательно возникающие во времени ошибки.

Предлагаемое техническое решение дает возможность при незначительном увеличении избыточного оборудования в несколько раз увеличить среднее время наработки на отказ запоминающего устройства, что в свою очередь увеличивает коэффициент готовности устройства. Для запоминающего устройства емкостью 4 Мбайта, выполненного:на микросхемах памяти емкостью 4096 бит с интенсивностью отказов 1 = 10 ч ", исполь-Ь зованне предлагаемого технического решения позволяет примерно на 0,04Ж повысить коэффициент готовности.

Источники информации, 4О принятые во внимание при экспертизе

1. Патент США Ф 39006200 кл. 235-153 АМ, опублик. 1975.

2. Авторское свидетельство СССР по заявке В 2690003/18-24, 45 кл. G 11 С 11/00, 1978.

873276

Составитель В. Гордонова

Техред А.Савка Корректор А, Дзятко

Редактор. Л. Тюрина

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 9055/77 Тираж 648

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5