Транзисторный инвертор

Иллюстрации

Показать всеРеферат

Союз Советскнк

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТИЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено 131179 (21) 2840782/24-07 с присоединением заявки М (23) Приоритет

Опубликовано 15.1081, бюллетень @38 (51)М. Кл.

Н 02 М 7/537

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 621. 314.. 58 (088. 8) Дата опубликования описания 151681 (.72) Авторы изобретения

Г.А. Белов и С.A. Кузьмин т

Чувашский государственный университет им. И Н...,ульянова, (71) Заявитель (54 ) ТРАНЗИСТОРНЫЙ ИНВЕРТОР

Изобретение относится к электро- технике и может быть использовано для преобразования постоянного напряжения высокого уровня в переменное или -постоянное напряжение другого уровня.

Известны инверторы и транзисторные ключи с последовательным соединением транзисторов, в которых для равномер- 1О ного распределения напряжений между последовательно соединенными транзис-

:торами используются выравнивающие цепи (1) ° Эти инверторы имеют пониженную надежность из-за того, что указанные выравнивающие цепи не устраняют перенапряжений и сверхтоков в транзисторах в процессах переключения

Наиболее близким к предлагаемому по технической сущности является ин-, 2О вертор, содержащий две цепочки из Nпоследовательно включенных транзисторов, присоединенных к выходному вЫводу, выравнивающие цепочки, которые выполнены в виде выпрямителей, причем входы выпрямителей подключены к дополнительным обмоткам выходного трансформатора, а выходы зашунтированы конденсатором и включены между симметричными относительно выходного вы- 30 вода точками соединен ия транзисторов в одной и другой цепочках (2).

Из-за разброса времени рассасывания отдельных транзисторов в таком инверторе наблюдаются перенапряжения на отдельных транзисторах и броски тока через них в процессах переключения.

Это приводит к снижению надежности инвертора, увеличению динамических потерь (уменьшению КПД), препятствует повышению рабочей частоты инвертора.

Целью изобретения является повышеwe надежности инвертора.

Цель достигается тем, что в транзисторном инверторе, содержащем по меньшей мере один полумост с .N-последовательно соединенными транзисторами, шунтироваиными встречно включенными диодами в каждом плече, выходной трансформатор,.дополнительные обмотки которого соединены со входом N-1, выпрямителей, выходы которых шунтированы конденсаторами и - вязаны с точками соединения транзисторов в плечах полумоста, и формирователи управляю.— щих импульсов, включенные во входную цепь каждого транзистора, выходы указанных выпрямителей соединены согласно последовательно, образуя цепочку с двумя крайними и N-2 промежуточными

873362 выводами, причем первый вывод цепочки выпрямителей соединен с точкой соединения первого и второго .транзисторов в первом плече полумоста, последний вывод этой цепочки соединен с точкой .соединения последнего и предпоследнег транзисторов во втором плече полумоста, каждый промежуточный К-ый вывод этой цепочки соединен через диоды с точкой соединения транзисторов с номером К+1 и К+2 первого плеча и точкой соединения .транзисторов с номером К и К+1 второго плеча, причем выход формирователя импульсов каждого, кроме последнего, транзистора первого плеча соединен с запирающим входом формирователя импульсов последующего транзистора через введенный элемент задержки, при этом выход формирователя импульсов каждого, кроме первого, транзистора второго плеча, соединен с запирающим входом формирователя импульсов предыдущего транзистора через введенный элемент задер жки, а выход формирователя импульсов последнего транзистора первого плеча и первого транзистора второго плеча соединен через введенный элемент задержки .с отпнрающими входами формирователей всех остальных транзисто-. ров второго и первого плеча соответственно.

Указанные элементы задержки могут быть выполнены регулируемыми.

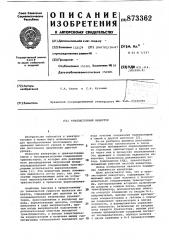

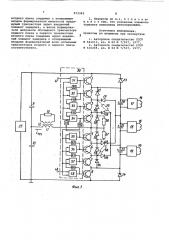

На Фиг.1 приведена принципиальная электрическая схема предлагаемого инвертора в случае последовательного соединения четырех транзисторов в цепочке; на фиг.2 — диаграммы напряжений токов, поясняющие .его работу.

Инвертор содержит первое и второе плечо полумоста с последовательно включенными транзисторами 14 и 5-8„ емкостный делитель напряжения на конденсаторах 9 н 10. В диагональ моста включена первичная обмотка 11 силового трансФорматора 12. Ко вторичной обмотке трансформатора подключена нагрузка 13. Трансформатор 12 имеет дополнительные обмотки 14-16, к которым подключены входы выпрямителей

17-19 с конденсаторами 20-22 на выходах. Выходы выпрямителей 17-18 соединены последоватЕльно согласно и образуют последовательную цепь, крайние выводы которой подключены к общим точкам транзисторов 1, 2 и 7, 8 и через диоды 23 и 24 — к полюсам основного источника питания 25. Первый промежуточный вывод цепи выпрямителей через диоды 26 и 27 подключен к общим точкам транзисторов 2, 3 и 5, б. Второй промежуточный вывод цепи выпрямителей через диоды 28 и 29 подключен к общиМ точкам транзисторов 3, 4 и 6, 7. При этом между общими точками транзисто.роа, связанными с одним выводом цепи выпрямителей оказываются включенными всегда три транзистора, например тРанзисторы 3, 4, 5 и 4, 5, 6, Влок управления 30 содержит формирователи управляющих импульсов 31-38 для каждого транзистора. Формирователи имеют о 5 входы для сигнала запирания и сигнала отпирания транзисторов. В каждой цепочке транзисторов выход каждого формирователя, начиная с Формирователя, ближайшЕго к полюсу источника питания (с формирователей 31 и 38 соответственно), соединен с запирающим входом следующего формировталея через элемент задержки 39-44. Выход последнего формирователя одного плеча (Формирователи 34 и 35) через элемент задер15 жки 45 или 46 соединен со всеми отпирающими входами формирователей дру- . гого плеча, Запирающий вход 47 формирователя 31 является входом для сигнала запирания цепочки транэисторов -.

1-4. Запирающий вход 48 формирователя является входом для сигнала запирания цепочки транзисторов 5-8. Диоды 4954 включены встречно параллельно транзисторам для обеспечения работы на активно-индукTRBHую нагруэ|<у °

Резисторы 55-58 улучшают распределение напряжения между транзисторами.

Инвертор работает следующим образом.

Количество витков дополнительных обмоток 14-16 выбирается таким образом, чтобы напряжения на выходе каж-. дОго выпрямителя UB„,f, равнялись Uä

14, где U - напряжение источника питания 25. Пусть в исходном состояЗ5 нии транзисторы 1-4 открыты, а транзисторы 5-8 закрыты, что соответствует интервалу (to, 1„) на фиг.2. На этом интервале потенциал 0р выходного вывода (общей точки соединения

Щ двух транзисторных цепочек) близок к

0с, ток первичной обмотки ср тран1 сформатора нарастает, напряжения

U„ †на транзисторах 1-4 близки к нулю. Диоды 26, 28, 24 закрыты, так как к первому приложено напряжение с конденсатора 20, ко второму — с конденсаторов 20 и 21, а к третьему приложению напряжение Uq — 30 g6 пр.Ha коллектор транзистора 6 через диод

27 подается потенциал асс - U B pp на коллектор транзистора 7 через диод

20 — потенциал U - 2 UBbWO на коллектор транзистора 8 — потенциал

0п- 30эь я . Таким образом на данном интервале напряжения коллектор

55 эмиттер 0 -UB транзисторов 5-8 определяются напряжениями на выходе вспомогательного выпрямителей и равны

"с(4 -

В некоторый момент подается сигнал щ запирания на вход 47 формирователя 31, затем через элемент задержки на запирающий вход формирователя 32 и т. д.

При этом запирающие сигналы на базы транзисторов 1-4 подаются поочередно, начиная с транзистора 1. Величина эа873362

Формула изобретения

1. Транзисторный инвертор, содержащий по меньшей мере один полумост с

N-последовательно соединенными транзисторами, шунтированными встречно вкл:о-енными диодами в каждом плече, выхоцной трансформатор, дополнительные обмотки которого соединены со входом И-l, выпрямителей, выходы которых шунтированы. конденсаторами и связаны с точками соединения транзисторов в плечах полумоста, и формирователи управляющих импульсов, включенные вс входную цепь каждого транзистора, отличающийся тем, что, с целью повышения надежности, выходы указанных выпрямителей соединены согласно последовательно, образуя цепочку с двумя крайними и N-2 промежуточными выводами, причем первый вывод цепочки выпрямителей соединен с точкой соединения первого и второго транзисторов в первом плече полумоста, последний вывод этой цепочки соединен с точкой соединения последнего и предпоследнего транзисторов во втором плече полумоста, каждЫЙ промежуточный К-ый вывод этой цепочки соединен через диоды с точкой соединения транзисторов с номером К+1 и

К+2 первого плеча и точкой соединения транзисторов с номером К и К+1 второго плеча, при этом выход формирователя импульсов каждого, кроме последнего, транзистора первого плеча соединен с запирающим входом формирователя импульсов последуюшего транзистора через введенный элемент задержки, при этом выход Формирователя импульсов каждого, кроме первого, транзистора . держки подачи запирающего сигнала для очередного транзистора выбирается больше, чем время рассасывания предыдущего транзистора. Через некоторое время после подачи сигнала на вход 47 (по истечении времени рассасывания) в момент 1 происходит запира .ие транзистора 1. На следующем интервале (ty z f.1 ) открыты транзисторы 2-4, остальные транзисторы закрыты. Ток начинает замыкаться по цепи:транзисторы

2»4, конденсаторы 20-22, диод 24. Выходной вывод имеет потенциал Оо -30щ,щр

К выключенному транзистору 1 при этом прикладывается напряжение Од - 3(/8,пр, напряжение на транзисторе 8 падает до нуля, так как диод 24 открывается. - 15

Диоды 26 и 28 по-прежнему закрыты. На коллекторы транзисторов 5, 6 и 7 через открытые диоды 27 и 29 подаются потенциалы выводов цепи выпрямителей.

Потенциал коллектора транзистора. 5 )() равен 3US»„> транзистора 6 - 20 „,„ транзистора 7 -08 „< . Таким образом, на этом интервале напряжения на всех транзисторах равны 0я /4.

В момент Ф происходит запирание транзистора 2. На следующем интервале (, 8 ) остаются открытыми транзисторы 3 и 4. Диод 26 открывается, диод

27 закрывается ток „замыкается по . цепи: транзисторы 3 и 4, диод 26, О конденсаторы 21 и 22, диод 24. Выходной вывод имеет потеициал (/д — 20 +„>, к выключенному транзистору 1 приложе.но напряжение Ор — 3V » ð к транзистору 2 - напряжение Оэ„,яp с конденса- ) тора 20. Напряжение на коллекторе транзистора 8 по-прежнему близко к нулю, потенциал коллектора транзистора 7 равен0ьь,„, поэтому напряжение коллектор-эмиттер транзистора 7 равно 4О

Uq/g суммарное напряжение на транзисторах 5 и 6 0 + 06 также равно

"я/4, и в целом напряжения на закрытых транзисторах не превышает(/„/4, 45

В момент запирается транзистор

3. На следующем интервале (1Э, Ф4 ) остается открытым только один транзистор 4. Ток i замыкается по цепи! транзистор 4, диод 28, конденсатор 22, диод 24. Выходной вывод имеет потенциал Up -06»щ, к коллектору. транзистора 2 приложен потенциал 3Uyg« к коллектору 3 — 2Ugq«, поэтому напряжение на закрытых транзисторах . 1 — 3 не превышае т V„/< . Суммарное напряжение на закрытых транзисторах

+ UЬ + Ut =U Ьып, напряжение на транзисторе 8 близко к нулю

В момент + запирается последний транзистор 4 и одновременно включают- б0 ся все транзисторы другой целочки

5-8, Элементы задержки 45 и 46 при этом предотвращают появление сквозных токов. Процессы в схеме .протекают далее аналогично описанным.

В кривой тока / „на фиг.2 имеются колебательные импульсы тока заряда конденсаторов 20-22.

Элементы задержки 39-41 и 42-44 могут быть выполнены регулируемыми.

При этом появляется возможность регулирования выходного напряжения инвертс ра.

B соответствии с изложенными принципами могут быть построены другие инверторные схемы. Например, однофазная мостовая Схема инвертора будет иметь четыре попарно соединенные цепочки, каждая из N-последовательно соединенных транзисторов, и соответственнЬ две последовательные цепи выпрямителей.

Предлагаемый инвертор по сравнению с известным имеет более высокую надежность, так как в нем устранены перенапряжения на отдельных транзисторах и броски тока через них в процессах переключения. Кроме того, новое построение схемы уменьшает динамические потери в транзисторах, увеличивает при прочих равных КПД инвертора и позволяет увеличить рабочую частоту.

873362 второго плеча соединен с запирающим входом формирователя-импульсов предыдущей транзистора через введенный элемент задержки, а выход формировагаля импульсов последнего транзистора первого плеча и первого транзистора второго плеча соединен через введенный элемент задержки с отпирающими входами формирователей всех остальных транзисторов второго и первого плеча соответственно.

2. Инвертор по п.1, о т л и ч а юшийся тем, что указанные. элементы задержки выполнены регулируемыми.

Источники информации

5 принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 641613, кл. Б.02 М 7/537, 1977.

2. Авторское свидетельство СССР

Р 610269, кл. Н 02 М 7/537, 1977.

873362

4 pp) Составитель

Техрее И.раеау Хоррехтор < « р,макаренко

Редактор Е.Дорошенко

Филиал ППП Патент, r.Óæãîðîä, ул.Проектная, 4

Заказ 9067/81 Тираж 733 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5