Аналого-цифровой фильтр

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

Союз Советских

Социалистическик

Республик о11873387 (61) Дополнительное к авт. сеид-ву (22) Заявлено 16. 01. 80 (21) 2869900/18-09 с присоединением заявки Йо (23) Приоритет

Опубликовано 15.1081. Бюллетень ИЯ 38 (51)м. Кл.з

Н 03 Н 17/00

Государственный комитет

ССС P но делам изобретений и . открытий (53) УДК 621.372. . 542 (088. 8) Дата опубликования описания 15. 10 81

Тараха и Е.И. Прокофьев

/ (72) Авторы иэобретения, A.Â. (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ФИЛЬТР

Изобретение относится к радио- " электронике, предназначено для фильтрации сигналов в быстро и медленнотекущих процессах и может быть использовано в вычислительной и локационной технике.

Известно фильтрующее устройство аналого-цифрового типа, которое сочетает высокую точность с возможностью фильтрации как быстротекущих, так и медленно изменяющихся процеесов, и содержащее последовательно соединенные аналоговый фильтр, ана-. лого-цифровой преобразователь, комт мутирующее устройство, регистр сдвига, цифро-аналоговый преобразователь, второй аналоговый фильтр и второе коммутирующее устройство, а также генератор тактовых импульсов, подключеннь.й к управляющим входам аналого-цифрового преобразователя,регистра сдвига и. обоих коммутирующих устройств Г1).

Фильтрация сигнала осуществля- ется дважды — на входе и выходе устройства, с промежуточными преобразователями и формации. Это обуславливает использование значительного количества аппаратуры и недостаточную скорость обработки информации.

Известен также аналого-цифровой фильтр, содержащий. дифференциальный усилитель (блок сравнения) во входной цепи, последовательно. соединенный с ним аналого-цифровой преобразователь (АЦП), выход которого является выходом фильтра. С выхода

AlgI на второй вход блока сравнения

° включена цепь обратной связи иэ последовательно соединенных цифрового фильтра (ЦФ) и цифро-аналогового преобразователя (ЦАП) (2 ).

Однако в известном устройстве с ростом его быстродействия значитель15 но возрастает объем цифровой части устройства.

Целью изобретения является повышение быстродействия.

Для этого в аналого-цифровой

20 фильтр, содержащий блок сравнения, первый вход которого является входом устройства, цифро-аналоговый преобразователь, аналоговый интегратор, два ключа, элемент совпадения, счет25 чик-сумматор и последовательно включенные генератор тактовых импуль- . сов счетчик импульсов и дешифратор, выход которого соединен с управляю-. щим входом первого ключа, введены

3Q интегрирующий сумматор, компаратор, 873387 определитель знака, дополнительные ключи и инвертор, причем блок сравнения, цифро-аналоговый преобразователь, первый ключ, аналоговый интегратор, инвертор, первый дополнительный ключ и интегрирующий сумматор соединены последовательно,второй вход интегрирующего сумматора соединен с выходом второго ключа, третий вход — с выходом второго дополнительного ключа, а выход — со входом комраратора и со входом определителя знака, выход которого подключен к одному из входов счетчикасумматора, информационные входы второго ключа и вторсго дополнительного ключа объединены и подключены .к выходу цифро-аналогового преобразователя управляющий вход второго дополни10

35 тельного ключа соединен с выходом элезнака 11 интеграла. Выход компаратора

10 соединен с управляющим входом третьего дополнительного ключа 12 и одним из входов элемента 13 совпадения, выход которого соединен с. управляющим входом ключа 8. Выход определителя знака 11 подключен к одному из входов счетчика-сумматора 14, второй вход которого соединен с выходом ключа 12. Выход счетчика-сумматора 14 подключен ко второму взводу блока 1 сравнения и является выходом фильтра.

Фильтр содержит устройство управлеS5

d0

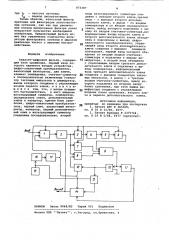

65 мента совпадения, первый вход которого объединен со вторым входом счет- Щ чика-сумматора и подключен к выходу дешифратора, а второй вход объединен с управляющим входом третьего дополнительного ключа и подключен к выходу компаратора, информационный вход третьего дополнительного ключа соединен с выходом генератора тактовых импульсов, а выход — с третьим входом счетчика-сумматора, вь1ход которого подключен ко второму входу блока сравнения, при этом выход дешифратора соединен с управляющими входами блока сравнения, второго ключа и первого дополнительного клю35 на чертеже представлена структурная электрическая схема аналого-цифрового фильтра. аналого-цифровой фильтр содержит во входной цепи последовательно соединенные блок 1 сравнения, цифроаналоговый преобразователь 2, первый ключ 3, аналоговый интегратор 4, инвертор 5, первый дополнительный ключ

6. Выход цифра-аналогового преобразователя 2 подключен ко входам перво- 45 го и второго дополнительных ключей 7 и 8. Вйходы этих ключей сое динены с двумя входами интегрирующего сумматора 9, третий вход которого подключен к вы- Я ходу ключа б. Выход интегрирующего сумматора 9 соединен с первым входом компаратора 10 и входом определителя ния в виде последовательно соединенных генератора 15 тактовых импульсов, счетчика 16 импульсов и дешифратора

17, выходы которого соединены с управляющими входами ключей 3,6 и 7, блока 1 сравнения, счетчика-сумматора

14, вторым входом элемента 13 совпадения. Выход генератора 15 подключен ко входу ключа 12.

В исходном состоянии напряжения на выходе интегратора 4 и интегрирующего сумматора 9 равны нулю,на входы цифро-аналогового преобразователя 2 с выхода блока 1 сравнения поданы нули, на всех разрядах входного кода и напряжение на его выходе также равно нулю. При этом сигнал на выходе компаратора — "ноль", счетчик-сумматор 14.обнулен, а состояние определителя знака 11 любое. Ключи 3,6,7,8 и 12 разомкнуты. Сигнал на выходе инвертора 5 соответствует единичному, а на выходе элемента 13 совпадения — "нулевому".

В начальный момент времени на входе блока 1 сравнения происходит алгебраическое суммирование входного кода, представляющего сумму полезного сигнала и помехи, с кодом отфильтрованного сигнала, поступающего с выхода счетчика-сумматора 14. Выработанный сигнал ошибки ДЧ и „ =. Ц, где Ч - текущее значение кода входного воздействия представляющего сумму полезного сигнала и помехи; текущее значение кода сиг1 нала обратной связи, поступает на вход цифро-аналогового преобразователя 2, где вырабатывается напряжение дп Ks

К Jig 1 где О - опорное напряжение цифроОП аналогового преобразователя 2;

К - коэффициент передачи цифро1 аналогового преобразователя

2 при значении И = Vmax;

Полярность напряжения U« определяется знаковым разрядом чйсла д „ .

По сигналу, приходящему с выхода дешифратора 17, замыкаются ключи б и 7, и начинается процесс фильтрации аналогового напряжения О+;, поступающего с выхода цифро-аналогового преобразователя 2. Фильтрация сигнала осуществляется при помощи последовательной цепи, образованной аналоговым интегратором 4, инвертором 5, ключом б, интегрирующим сумматором 9 и параллельной цепью, образованной ключом 7 и интегрирующим сумматором 9.

Интегрирование аналоговым интегратором 4 длится в течении време873387 ни Т, напряжение U«на выходе его равно

Т

21 Jt =Т С„ 14 2(1-1)Ь=т

by О К1 .Т-М2(1-1)Т), 5 b rnax где 4 — постоянная времени интегратора 4.

Напряжение О „ поступает на первый вход интегрирующего сумматора !О

9, на второй его вход приходит напряжение ОА„ . При этом интегрирующий сумматор 9 интегрирует сумму напряжений 0 „ и О „ и напряжение на его выходе определяется 15 т ч 1 =-,(. J 4v«+ i«)& о

Ч оп 1 on л, =- — Я Т ь.Я„. "во 2 " щ / Га 2О-МттУ где 0 . — берется со знаком "плюс", .1 так как на входе интегрирующего сумматора 9 включен инвертор 5; 25 постоянная времени интегри рующего сумматора 9.

По истечении времени интегрирова- ния Т размыкаются ключи 3, б и 7. На выходе интегрирующего сумматора 9 имеется напряжение U> Оно поступает на компаратор 10 и переводит его в единичное состояние. На выходе определителя знака 11 также появляется сигнал, определяющий операцию (суммирование или.вычетание) в счетчикесумматоре 14. По окончании режима интегрирования на вход цифро-аналогового преобразователя 2 по сигналу от дешифратора 17 поступает числоЬЧ „Щ ьЧ

ЬъДX и является величиной постоянной.

Спустя время, равное времени установления выходного напряжения, циф- ф5 ро-аналоговый преобразователь 2 вырабатывает напряжение 0« = +U ° К ., %

Знак этого «спряжения равен знаку напряжения О „- . Затем по сигналу . управления с дешифратора 17 замыка- 5р ются ключи 8 и 12. Напряжение 0 и поступает на вход интегрирующего сумматора 9. Напряжение U начинает уменьшаться до нуля. Тогда на выходе компаратора 10 появляется сигнал 55 логического "нуля", и ключи 8 и 12 размыкаются. За время уменьшения напряжения в интегрирующем сумматоре

9 через ключ 12 на вход счетчикасумматора 14 поступает некоторое число импульсов от генератора так- 40 товых импульсов 15. Число этих импульсов пропорционально напряжению

U j Ä которое было на выходе интегрирующего сумматора 9 до момента подачи на его вход напряжения 0Д . 65

Величина напряжения 0 „ при подаче напряжения U Ä переменна. Обозначим

3Ф, ее Ом где t p. - время интегрирования интегрирующего сумматора 9 при записи приращений в счетчик-сумматор 14

С вЂ” постоянная времени интегрирующей сумматора 9 при записи приращений в счетчик-сумматор 14.

В это время через замкнутый ключ

12 поступают импульсы с постоянной частотой f>, которые суммируются в счетчике-сумматоре 14.

Число импульсов можно определить согласно выражению

43ci

1 =3 Етм =ХтСЗс„ .

Оно определяет приращение выходной величины, записанной в счетчике-сум маторе 14, на i-m шаге фильтрации входного сигнала. для получения полной характеристики фильтра необходимо рассмотреть сумму из и таких шагов. Полагая,что

tn„ = Ч где аЧ .; — приращение, записанное в счетчик-сумматор 14 на

i-m шаге, можно определить характеристику аналого-цифрового фильтра

И-"

%=z Ч„;

4=o где n — число шагов; т или Ч= 2.". 5>11+ 1Ж

Нолагая, что время интегрирования

Т = const можно найти время работы аналого-цифрового фильтра, которое определяется как t> = nt.Çíà÷åíèå выходной величины „. записанное в счетчик-сумматор 14, подается на вход блока 1 сравнения, где сравнивается со входным кодом. Процесс отработки входного сигнала продолжается до того .момента, пока не. выполнится равенство ЬЧ = О.

Количество аппаратуры предлагаемого устройства не зависит от частоты фильтруемого сигнала. Максимальная частота фильтруемого сигнала определяется быстродействием элементов схемы, в особенности быстродействием цифро-аналогового преобразователя 2 и временем интегрирования Т. Согласно теореме Котельникова частота сигнала, представленного в виде дискретной величины, связана с периодом дискретизации соотношением

М р с 2Т„

873387

Формула изобретения

ВНИИПИ Заказ 9069/82 Тираж 991 Подписное

Филиал ППП Патент, r.Óæãoðoä, ул.Проектная, 4 где f - частота сигнала;

T* - период дискретизации.

Таким образом, известный фильтр пригоден для фильтрации низкочастотных сигналов, так как при увеличении полосы пропускания фильтра резко возрастает количество необходимой аппаратуры. Предлагаемый фильтр может без увеличения количества аппаратуры фильтровать сигналы в широком диапазоне частот с высоким быстродействием.

Аналого-цифровой фильтр, содержащий блок сравнения, первый вход кОторого является входом устройства, цифро-аналоговый преобразователь, аналоговый интегратор, два ключа, элемент совпадения, счетчик-сумматор и последовательно включенные генератор тактовых импульсов и дешифратор, ;выход которого соединен с управляющим входом первого ключа, о т л и ч а юшийся тем, что, с целью повышения быстродействия, в него введены интегрирующий сумматор, компаратор, определитель знака, дополнительные ключи и инвертор, причем блок сравнения, цифро-аналоговый преобразователь, первый ключ, аналоговый интегратор, инвертор, первый дополнительный ключ и интегрирующий сумматор соединены последовательно, второй вход интегрирующего сумматора соединен с выходом второго ключа, третий вход — с выходом второго дополнительного ключа, а Выход — со входом (! компаратора и со входом определителя знака, выход которого подключен к одному из входов счетчика-сумматора,информационные входы второго ключа и второго дополнительного ключа объединены и подключены к выходу цифроаналогового преобразователя, управляющйй вход второго дополнительного ключа соединен с выходом элемента совпадения, первчй вход которого объединен со вторым входом счетчикасумматора и подключен к выходу де35 шифратора, а второй вход объединен с управляющим входом третьего дополнительного ключа и подключен к выходу компаратора, информационный вход третьего дополнительного ключа

Щ соединен с выходом генератора тактовых импульсов, а выход — с третьим входом счетчика-сумматора, выход которого подключен ко второму входу блока сравнения, при этом выжод де 5 шифратора соединен с управляющими входами блока сравнения, второго ключа и первого дополнительного ключа.

Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ Р 265508, кл. Н 03 Н 11/00, 1977.

2. Патент Франции Р 2375764, кл. Н 03 Н 5/08, 1977 (прототип).