Устройство регулируемой задержки

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОИЖОМУ СВ ИТИИвСТВУ

Союз Соаетскнх

Сацйайнстнческнк

Республик (á3) Дополнительное к авт. сеид-еу (22) Заявлено 031279 (21) 2846285/18-21 ®)М Л с присоединением заявки Нов

Н 03 К 5/13

Государственный квинтет

СССР яо дмам нзобретеннй н открытнй (23) Приоритет

Опубликовано 1%1081. бюллетень т4к 38 (Дата опубликованию описания 15.1081 (S3) УДф(621.374.5 (088.8) (72) Авторы изобретения

А.К.Ваганов, В.С.Васильев и В.И.Гордин .1

)

Ч у

1 (71) Заявитель (54) УСТРОЙСТВО РЕГУЛИРУЕМОЙ ЗАДЕРЖКИ

Изобретение относится к импульсной технике и может быть использовано для формирования временных интервалов в устройствах импульсной радиосвязи, .радионавигации, телеметрии, s различных схемах таймирования, при исследованиях в области ядерной физики и т.д.

Известно устройство квантованной задержки, содержащее два счетчика, блок поразрядного сравнения, элемент совпадения и элемент запрета (1),.

Недостатком устройства является ограниченная величина дискретности регулирования временного интервала 15 и нестабильность величины формируемой временной задержки при воздействии асинхронного стартового сигнала, которые определяются периодом тактовой частоты. 20

Наиболее близким к предлагаемому является устройство, содержащее эле» мент ИСКЛЮЧИОЩЕЕ ИЛИ, установочный счетчик н триггер управления (2).

Недостатками устройства являются 25 большая величина дискретности регулирования временного интервала,определяемая.периодом следования тактовых импульсов (T> ), поступающих от внешнего-генератора, и большая вели 30 чина нестабильности формируемой временной задержки при воздействии асинхронного стартового сигнала, макси- . мальная величина которой также определяется периодом следования тактовых импульсов (Т ).

Цель изобретения — уменьшение дискретности регулирования временного интервала и повышение его стабильности.

Для достижения указанной цели в устройство регулируемой задержки, содержащее триггер- управления, установочный счетчйк и регистр памяти, введены дешифратор, И элементов задержки, N логических элементов ИЛИ и (N+1) логических элементов И, причем вход устройства соединен со входом установки единицы триггера управления и с первыми входами И-логических элементов И, вторые входы которых связаны с выходами дешифратора, а выходы — с первыми входами соответствующих элементов ИЛИ, выход триггера управления-подключен ко входу записи установочного счетчика и к первому входу (N+1)-ого логического элемента И, выход которого соединен со . вторым входом первого логического элемента ИЛИ, выход последнего связан

873396

60 со входом первого элемента задержки, выход которого соединен со вторым входом второго логического элемента

ИЛИ, выход последнего подключен ко входу второго элемента задержки и т.д., выход N-ого элемента задержки подключен к счетному входу установочного счетчика и ко второму входу (N+l)-ого логического элемента И, а входы дешифратора и информационные входы установочного счетчика связаны через регистр памяти с шинами записи,, выход установочного счетчика соединен со входом установки нуля тригге- ра управления и выходом устройства.

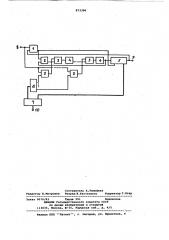

На чертеже представлена структурная схема предлагаемого устройства ре- 15 гулируемой задержки.

Устройство состоит из триггера управления 1, выход которого связан с первым входом (N+l)-ого логического элемента И 2, выход которого соединен Я со вторым входом первого из N -логи-ческих элементов ИЛИ 3, а выходы последних подключены ко входам соответствующих элементов задержки 4 установочного счетчика 5, счетный вход которого подключен к выходу Н-ого элемента задержки и ко второму входу (N+1)-.ого логического элемента И, а вход записи — к выходу триггера управления 1, дешифратора 6, выходы которого связаны со вторыми входами

N логических элементов И, а выходы— с регистром памяти 7, подключенным также к шинам записи установочного счетчика, входа 8 устройства, соединенного со входом установки единицы триггера управления и с первыми входами N логических элементов И, выходы которых подключены к первым входам соответствующих логических элементов ИЛИ, выхода 9 устройства, 40 связанного со входом установки нуля триггера управления и являющегося выходом установочного счетчика, шин записи 10, подключенных ко входам регистра памяти °

1 45

Устройство регулируемой задержки работает следующим образом.

В исходном состоянии (до момента прихода запускающего сигнала на вход 8 устройства) триггер управле- щ ния 1 находится в нулевом состоянии, блокируя по первому входу (N+1)-й логический элемент И 2 и по входу записи установочный счетчик 5. Дешифратор 6 блокирует по вторым входам все N логических элементов И 2 кроме одного, номер которого определяется кодом, присутствующим на входах дешифратора 6. На информационных входах установочного счетчика 5 при сутствует код,определякнций число, записываемое в счетчик. В регистр памяти 7 записано по шинам записи

10 число, соответствующее заданной величине задержки. В момент прихода на вход 8 запускающего импульса триг- 65 гер управления 1 переключается в единичное состояние, деблокируя (N+l)-й логический элемент И 2 и установочный счетчик 5, в который из регистра памяти 7 записывается число. Одновре- . менно с этим запускающий импульс проходит через один из N логических элементов И 2, на втором входе которого отсутствует сигнал запрета от дешифратора 6, и поступает на первый вход соответствующего логического элемента ИЛИ 3. Затем этот импульс проходит через последующие соединенные последовательно, чередующиеся логические элементы ИЛИ 3 и элементы задержки 4, а также через деблокированный (И+1)-й логический элемент И.

Далее импульс циркулирует по кольцу, образованному логическими элементами

ИЛИ З,элементами задержки 4и (N+1) — ûì логическим элементом И 2. На выходе

Н-ого элемента задержки генерируется последовательность тактовых импульсов, период следования которых определяется суммарной величиной задержки элементов кольца. Момент появления первого тактового импульса на счетном входе установочного счетчика 5 определяется временем задержки прохождения импульса от логического элемента ИЛИ 3, связанного с соответствующим деблокированным дешнфратором 6 логическим элементом

И 2, до выхода N-oro элемента задержки. Счетчик начинает считать тактовые импульсы, и когда их число совпадает с записыванным в установочный счетчик числом, он устанавливается в нулевое состояние. На выходе счетчика вырабатывается задержанный относительно запускающего импульса сигнал, который поступает на выход 9 устройства регулируемой задержки и на вход установки нуля триггера управления

1, который переключается в начальное состояние, блокируя по входу записи установочный счетчик 5 и (И+1)=й логический элемент И. Устройство возвращается в исходное . состояние.

Общая величина формируемого временного интервала задержки определяется как т б ц = т + тсц.> (1) где Т вЂ” начальная величина задержйач. ки, определяемая временем прохождения запускающего импульса по цепи задержки от логического элемента

ИЛИ, связанного с деблокированным дешифратором логическиМ элементом И, до выхода N-ого элемента задержки;

Т вЂ” величина временного интерсч. вала, формируемого установочным счетчиком.

873396

Формула изобретения устройство регулируемой задержки, содержащее триггер управления, установочный счетчик, регистр памяти, о т л и ч а ю щ е е с я тем, что, с целью уменьшения дискретности регулирования временного интервала и повышение его стабильности, в него введены дешифратор, и элементов задержки, N логических элементов ИЛИ и (N+1) логических элементов И, причем вход устройства соединен со входом установки единицы триггера управления и с первым входом N логических элементов И, вторые входы которых связаны с выходами дешифратора,. а выходы — с первыми входами соответствующих элементов ИЛИ, выход триггера управления подключен ко входу записи установочного счетчика и к первому вхо" ду (N+1)-ого логического элемента И, выход которого соединен со вторым входом первого логического элемента

ИЛИ, выход последнего связан со входом первого элемента задержки, выход которого соединен со вторым входом . второго логического элемента ИЛИ, выход последнего подключен ко входу второго элемента задержки и т.д выход N-ого элемента задержки подключен к счетному входу установочного счетчика и ко второму входу (N+1)-oro логического элемента И, а входы дешифратора и информационные входы установочного счетчика связаны через регистр памяти с шинами записи, выход установочного счетчика соединен со входом установки нуля триггера управления и выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 639132, кл. Н 03 К 5/13, 28.12.73.

2. Патент Японии Р 52-36669, заявл. 08.12.72, 9 47-123245, кл. 98/5/С22, Н 03 К 5/153, опублнк.

17.09.77 (прототип) .

Tcl4, = m Tî ° (4) где m=0,1,...,М вЂ” число, записанное в установочный 25 счетчик, T — период повторения генерируемых тактовых импульсов, который равен 3О

Т,=Ы/Т„+Т +т = Н TÄ (S)

Таким образом, величина формируемого временного интервала задержки в предлагаемом устройстве равна

Тобы,= К . Т1 + щ - Ty ° (6) 35

В известном устройстве величина временного интервала задержки определяется как .

Т бщ= <.То + Ь Т и Тщц» — "То,.- (7) где То — период следования тактовых импульсов, 4О

aT — нестабильность формируемого, временного интервала, определяемая асннхронностью поступления импульса запускапо отношению к.тактовым им- 45 пульсам.

Из формулы (6) и (7) видно, что при равенстве

To m To,(8) в предлагаемом устройстве возможна у() дополнительная регулировка формируемого временного интервала (см. формулу 5) с дискретностью

Т

N (9)

Следовательно, в предлагаемом уст,ройстве регулируемой задержки дискретность регулирования по сравнению с известным уменьшена в М раз.

Из принципа работы известного устройства следует, что максимальная ве- ФО личина нестабильности формируемого, временного интервала Ь Т (в формуле

7) прн асинхронном воздействии запускающего импульса составляет

ЬТ = То. (10) 65

При этом

Т„„„= К/Т„+ Т + ТЭ, (2) где Т вЂ” величина временной задерж1 ки, определяемая элементом задержки;

Т вЂ” величина временной задержки, вносимая логическим эл)ементом ИЛИ;

Т вЂ” величина временной задержки, Э вносимая (N + 1)-ым логическим элементом И, ((=11,...,й - количество элементов задержки и логических элементов

ИЛИ, через которые проходит импульс запуска до того, как поступает на счетный вход установочного счетчика.

С хорошей степенью приближения можно считать, что величина начальной задержки составляет

T нач К ° Т„. (3)

Величина временного интервала, формируемого установочным счетчиком, равна

В предлагаемом устройстве подобная ошибка исключена, так как момент на-( чала формирования временного интервала всегда жестко связан с произвольным моментом появления импульса запуска, который проходит через деблокированный дешифратором логический элемЕнт И, поступая в определенную точку кольца. Следовательно, предлагаемое устройство формирует временные интервалы, обладающие значительно большей стабильностью, чем у известного устрОйства.

Наибольший эффект от применения предлагаемого устройства достигается при формировании временных интервалов наносекундного диапазона. В качестве элементов задержки в этом случае целесообразно испольэовать интегральные микросхемы.

873396

Составитель А.Тимофеев

Редактор И.Мнтровка Техред Ж.Кастелевич Корректор Г.Огар

Заказ 9070/83 Тирам 991 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретении и открытия

113035, Москва, X-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Умгород, ул. Проектная, 4